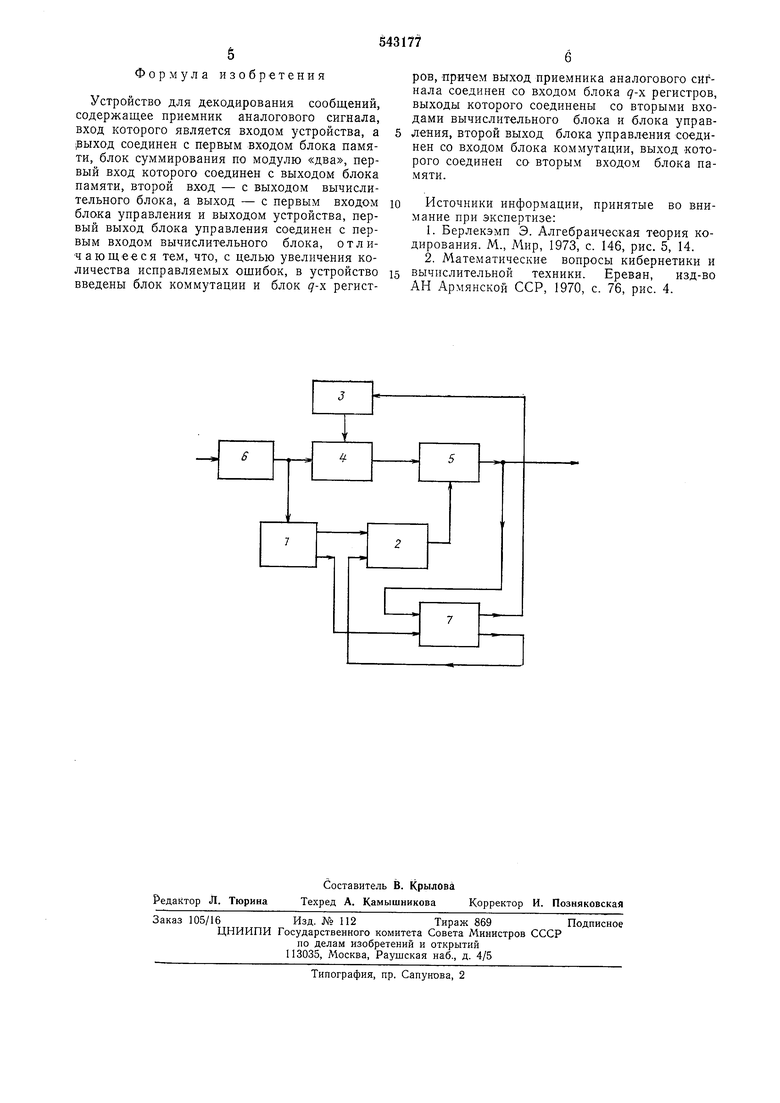

выход которого соединен со вторым входом блока памяти. На чертеже представлена блок-схема описываемого устройства. Опо содержит блок 1 q-y регистров, предназначенный для проверки условий, которым должен удовлетворять кодовый вектор, вычислительный блок 2, где происходят поиски номеров искаженных символов, блок 3 Коммутации, устанавливающий длину кодового вектора, блок 4 памяти, где размещается принятое сообщение, представленное в виде двоичного вектора, блок 5 суммирования по модулю «два, служащий для инвертирования искаженных символов принятого вектора. На входе устройства стоит приемник 6 аналогового сигнала, и функционирование устройства в целом обеспечивается блоком 7 управления. Вход приемника 6 аналогового сигнала является входом устройства, а выход соединен с первым входом блока 4 памяти; первый вход блока 5 суммирования по модулю «два соединен с выходом блока 4 памяти, второй вход- с выходом вычислительного блока 2, а выход - с первым входом блока 7 управления н выходом устройства; первый выход блока 7 управления соединен с первым входом вычислительного блока 2, второй выход - со входом блока 3 коммутации, выход которого соединен со вторым входом блока 4 памяти. Вход блока 1 (7-х регистров соединен с выходом приемника 6 аналогового сигнала, первый выход - со вторым входом блока 7 управления, второй выход - со вторым входом вычислительного блока 2. Аналоговый сигнал проходит через приемник 6, принимает дискретную форму и в виде двоичного вектора ... Xn-i, или 1, поступает в блок 4 памяти и одновременно в блок 1 7-х регистров. В блоке 1 q-- регистров вычисляются симметрические многочлены Os согласно уравнению . а Xi Xt, /.0, . a(modf()), Здесь ffs и а являются элементами поля Галуа GF(q) образуемого неприводимым многочленом 1(х), степени т, показателя п с коэффициентами нз поля GF(q), /(а)0; s пробегает значения от 1 до t, где t- количество несимметрических ошибок, которые исправляются кодом, применяющимся для передачи информации. Количество т ошибок, имеющих место в канале связи т определяется согласнО максимальному индексу симметрического многочлена d, значение которого отлично ОТ значения о, выбранного при кодировании. Величины 01, 02,... (Т-. поступают в вычислительный блок 2, а значение т - в блок 7 управления. По значению t блок 7 управления выдает в вычислительный блок 2 команду на решение уравнения -2 K-a,)-C--f (о I - 2) V -...+ (-1Г(,, если исправляются искажения нулевого символа, и уравнения оооо х- - (о, - С,) X-I + (а, - о,) л;-2 -... + (-1) К - ) О если в канале искажаются символы «1. Решения этого уравнения представлены в виде степеней элемента а и показателем этих степеней - номера искаженных символов дискретного сигнала. Выход вычислительного блока 2, воздействуя на один из входов блока 5 суммирования по модулю «два, меняет значение соответствующего символа дискретного сигнала, поступающего на другой вход блока 5, если этот символ искажен, и оставляет его без изменения, если символ правилен. На выходе блока 5 появляются истинные значения дискретного сигнала. Переключение с одной длины кодового слова над другую происходит при поступлении на блок 7 управления служебной информации из блока 5. Блок 7 управления, воздействуя через блок 3 коммутации на блок 4 памяти, устанавливает необходимую длину кодового слова и, если необходимо, дополнительную величину задержки, зависящую от количества корректируемых ошибок и быстродействия вычислительного блока 2. Таким образом, коррекция ошибок происходит в темпе поступления сигнала иа вход устройства. Эффективность изобретения обеспечивается возможностью исправления многократных неимметрических ошибок; адаптацией к кодоой длине и количеству исправляемых ошиок; использованием в канале связи кодов с ольшой мощностью. При исправлении f несимметрических ошиок для мощностей используемых двоичных одов снраведлива оценка, i и , где р - простое число , (2- + п2 )(п + 1), мощности всех известных кото превышает ов. Применение д-к логики при декодировании воичных сигналов позволяет использовать лассические способы решения квадратного равнения, что и ведет к увеличению быстроействия устройства.

5

Формула изобретения

Устройство для декодирования сообщений, содержащее приемник аналогового сигнала, вход которого является входом устройства, а 1ВЫХОД соединен с первым входом блока памяти, блок суммирования по модулю «два, первый вход которого соединен с выходом блока памяти, второй вход - с выходом вычислительного блока, а выход - с первым входом блока управления и выходом устройства, первый выход блока управления соединен с первым входом вычислительного блока, отличающееся тем, что, с целью увеличения количества исправляемых ошибок, в устройство введены блок коммутации и блок -х регист6

ров, причем выход приемника аналогового сигнала соединен со входом блока -х регистров, выходы которого соединены со вторыми входами вычислительного блока и блока управления, второй выход блока управления соединен со входом блока коммутации, выход которого соединен со вторым входом блока памяти.

Источники информации, принятые во внимание при экспертизе:

1.Берлекэмп Э. Алгебраическая теория кодирования. М., Мир, 1973, с. 146, рис. 5, 14.

2.Математические вопросы кибернетики и вычислительной техники. Ереван, изд-во АН Армянской ССР, 1970, с. 76, рис. 4.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для кодирования сообщений | 1974 |

|

SU543176A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU1001147A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Устройство для исправления ошибок | 1987 |

|

SU1432787A1 |

| Устройство защиты от ошибок внешней памяти | 1981 |

|

SU1018119A1 |

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU1029205A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОДА ХЕММИНГА | 1969 |

|

SU246353A1 |

Авторы

Даты

1977-01-15—Публикация

1974-12-18—Подача