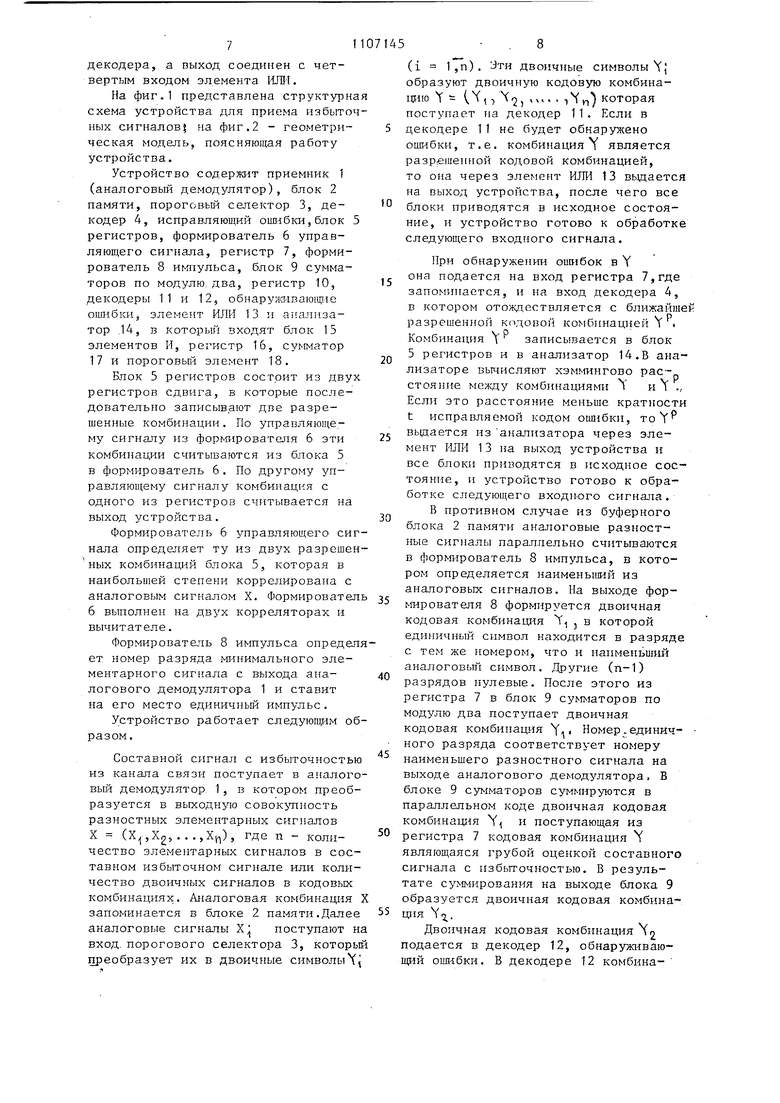

Изобретение относится к электро связи и может быть использовано в системах передачи информации для приема составных сигналов с избыточностью, использующтх длинные и сверхдлинные помехоустойчивые коды. Известно устройство для приема избыточных сигналов, содержащее пороговый селектор, блок сравнения и решающий блок lj , Недостатком известного устройст является низкая помехоустойчивость приема сигналов, поскольку в нем недостаточно полно используется апостериорная информация о принято слолгаом сигнале с избыточностью. Известно также устройство для приема дискретной информации, соде жащее блок отсчета сигнала, блок сравнения, блок памяти, блок пороговых уровней напряжений, блок опр са и решающий блок 2. Недостатком данного устройства является ограниченная область функ щональных возможностей, так как устройство обрабатьшает ограниченный класс сигналов, формируемых на основе мажоритарно Декодируемых ко дов. Наиболее близким к предлагаемом является устройство для приема изб точных сигналов, содержащее приемник, вход которого является входом устройства, выход приемника соединен с входом блока памяти, первый выход которого соединен с первым входом форю1рователя управляющих сигналов и через пороговый селектор - с входом первого декодера, первьд выход которого соединен с п вым входом элемента ИЛИ, второй вы ход - с входом первого регистра и первым входом второго декодера, вы ход второго декодера соединен с первым входом блока регистров, пер выход которого соединен с вторым входом элемента ИЛИ, вторые выход вход подключены соответственно к второму входу и к выходу формирова ля управляющего сигнала, вторые вы ходы блока памяти соединены через формирователь импульса с соответству ющими первыми входами блока сумматор второй вход которого подключен к выходу первого регистра, выходы блока сумматоров соединены с соответствующими входами третьего деко ра, первые выходы которого соединены с cooтвeтcтвyющи M входами второго регистра, выход которого соединен с вторым входом второго декодера,второй выход третьего декодера соединен с третьим входом элемента ИЛИ, выход которого является выходом устройства. Известное устройство обладает высокой оперативностью приема сообщений З . Однако известному устройству свойственен недостаток, для выявления которого рассмотрим геометрическую модель процесса обработки составного сигнала с избьпочностью. Изображенная па фиг.2 область соответствует части области сигнальных точек, каждая из которых определяет аналоговый сигнал на выходе аналогового демодулятора известного устройства. В частности, изображены сигнальные точки, которые в одном случае (если они расположены левее линии ЛВ - прием в целом) отождествляются с разрешенной кодовой комбинацией { , а в другом (если они находятся правее линии АВ, а процедура приема - прием в целом) - с разрешенной кодовой комбинацией Ч 2 Ломанкая линия 1-2-3-4-5-6-7-8 есть граница областей отождествления сигнальных точек с разрешенными кодовыми комбинациями Y, и Yp при посимвольном приеме. Как известно, процедура посимвольного приема вк.пючает две операции . Первая операция реализуется в так называемой первой решающей схеме, состоящей из аналогового демодулятора (на выходе его формируются сложные аналоговые сигналы Х) и однопорогового квантизатора (аналогоцифрового преобразователя), на выходе которого формируется двоичная кодовая комбинация Y, Вторая операция - декодирование комбинации Y в ближайшую разрешенную двоичную кодовую комбинацию Y , Она реализуется с помощью декодера, исправляющего ошибки. Рассмотрим некоторые частные случаи. Будем считать, что передавалась двоичная кодовая комбинация V , 1. Выходной аналоговый сигнал демодулятора Х(. С помощью первой решающей схемы (однопорогового селектора) сигнал X, отождествляется с 3 двоичной кодовой комбинацией VJ которая декодером преобразуется в разрешенную кодовую комбинацию Y. Прием, в целом зак.п очается в сравнении расстояний между аналоговым сигналом и BceivOi используемыми в системе разрешенными кодовыми кoмбинaция {и с последующим принятием решения в пользу той из разре шейных комбина1р1й, для которой укаванное расстоя-ние наименьшее. При приеме в целом сигнальная точка Х отождествляется с ближайшей разрешенной кодово й комбинацией Т (точки, расположенные левее АВ,находятся ближе к V. а точки, которы расположены правее линии АВ, - ближе к Yg ) Можно заключить, что посимвольный прием приводит к ошибочному решению, а прием в целом для данного - к безошибочному решению. Отметим, что, хэьшингово расстояние меззду д и ij равно Л-1 если об нечетно если Об четно максимальному удалению двоичной ком бинации Y-J от своей разрешенной комбинации 2,На выходе аналогового демодулятора формируется сигнал 2 который квантизатором (т.е. однопо роговым селектором) преобразуется в комбинацию 2 J отождествляемую декодером с . Тогда можно заключит что посимвольное решение безошибоч Заметим, что хэммингово расстояние меяэду 2 и Y 2 максимально равно t, 3.Выходным сигналом аналоговог демодулятора является Х. При поси вольной обработке он преобразуется соответственно в и в Y, что также соответствует безошиЗочному решению. Хэммингово расстояние меж ду Y, и YI равно t, I :Анализ рассмотренных случаев позволяет сделать следующ 1е выводы в области отождествления калсцой разрешенной комбинации имеютс.я двои ные комбинации, удаленные -от разрешенных на максимально возможное (в пределах исправляющей способност кода) расстояние равное tj посимвольное решение только в случае, когда указанное расстояние равно 5 именно t, может быть или ошибочным (случай 1) или безошибочным (случаи 2 и 3). Из данных выводов следует, что в случае, когда расстояние между выходной комбинацией порогового селектора и ей соответствующей выходной разрешенной комбинацией декодера равно t, решение посимвольной процедуры неоднозначно и с помощью алгоритма, реализуемого в известном устройстве, необходимо сформировать другую разрешенную кодовую комбинацию, с помощью которой и разрешается указанная неоднозначность. Если же расстояние между указанными комбинациями меньше t, то алгоритм, связанный с формированием второй разрешенной комбинацией, применять не имеет смысла, так как в этом выходная комбинация (первая) с высокой степенью достоверности соответствует переданной. Теперь рассмотрим основные моменты обработки избыточн1.1Х сигналов в известном устройстве: а)если выходной аналоговьй сигнал демодулятора есть Х, то на выходе однопорогового квантизатора формируется разрешенная двоичная кодовая комбинация Yo , что фиксируется декодером, обнаруживающим ош11бки. В данном случае ошибки отсутствуют и разрешенная кодовая комбинация Yo выдается через элемент ИЖ на выход известного устройства б)выходной аналоговый сигнал соответствует сигнальной точке Xg (фиг.2). В этом случае на выходе квантизатора фop rapyeтcя двоичная кодовая комбинация YI, не являющаяся разрешенной. Поэтому через декодер, обнаруживающий ошибки, Yg подается в декодер, исправляющий ошибки. Выходная разрешенная кодовая комбинация Yg декодера, исправляющего omii6КИ; записывается в блок регистров памяти. В известном устройстве не сразу анализируют тот факт, что является Y2 переданной или нет. .г Прежде выполняют следующие операции. С помощью двоичного регистра, решающего блока и сумматора по модулю два из Xg и V фop иpyют двоичную кодовую комбинацию Ytt В случае, когда является разрешенной комбинац,ией,она через декодер, обнаруж11ваю1 Д1й oimi6 ки, и элемент ИЛИ вьщается на выход

устройства. В протигзном случае YU/ с помощью декодера, исправляющего ошибки, преобра.зуют в разрешенную двоичнуро кодовую комбинацию, например, YD/ . Далее Yot записывают в блок регистров памяти. В известном устройстве не сразу анализируют тот факт, что является Y . переданной или и ет 5

в)сигнал Хр таков, что ему соответствует двоичная кодовая комбинация Ч р . В этом случае кратность г о11П1бки5 которая перевела Y J р ; равна 1 г t. Это наиболее вероятная ситуация при обработке составнЕ 1х сигналов с избыточностью, формируемых на основе длинных и сверхдлинных , для которых макст-п 1альная кратность исГ1равлтяемых ошибок t 2. Алгоритм обработ си соответствует алгоритму u,S. В этом случае передатиюй (с наиболыией вероятностью) будет являться первая выходная комбинац1-1Я декодера, исправляющего ошибки,

г)сигналу Х./Хл соответствует

УV I /

двоичная кодовая комбинациях т,е, имеет место тот случай,когда кратность оил-1бкиравна г t. Ив этом случае в известном устройстве реализуется алгоритм n.S что является целесообразным.

Следовательно, в известном устL

роистве в случае ситуации по п, D. принятие решения является излишне длительным. Достаточно установить, что г t, и тогда выходная разрешенная комбинация декодера, исправляющего ошибки, будет являться переданной (вероятность этого события велика).

Таким образом, в известном устройстве в наиболее часто встречающихся ситуациях формируют вторую двоичную разрешенную кодовую комбинацию, что не является необходимы При этом функционирует декодер, исправляю1Щ-1Й ошибки, формирователь импульса (решаюш 1Й блок), являющиеся достаточно сложны ш устройствами. Это вызывает увеличение вероятности ошибочного приема составного сигнал .с избыточностью в результате увеличения вероятности сбоя в декодере, исправляющем ошибки, или в решающем блоке, что является недостатком изв.естного устройства.

Цель изобретения - повышение помехоустойчивости приема составных сигналов с избыточностью за счет уменьшения вероятности сбоя в декодере, исправляющем ошибки, и в решающем блоке путем исключения из процесса обработки сигналов указан} ых блоков в наиболее часто встречающихся ситуациях.

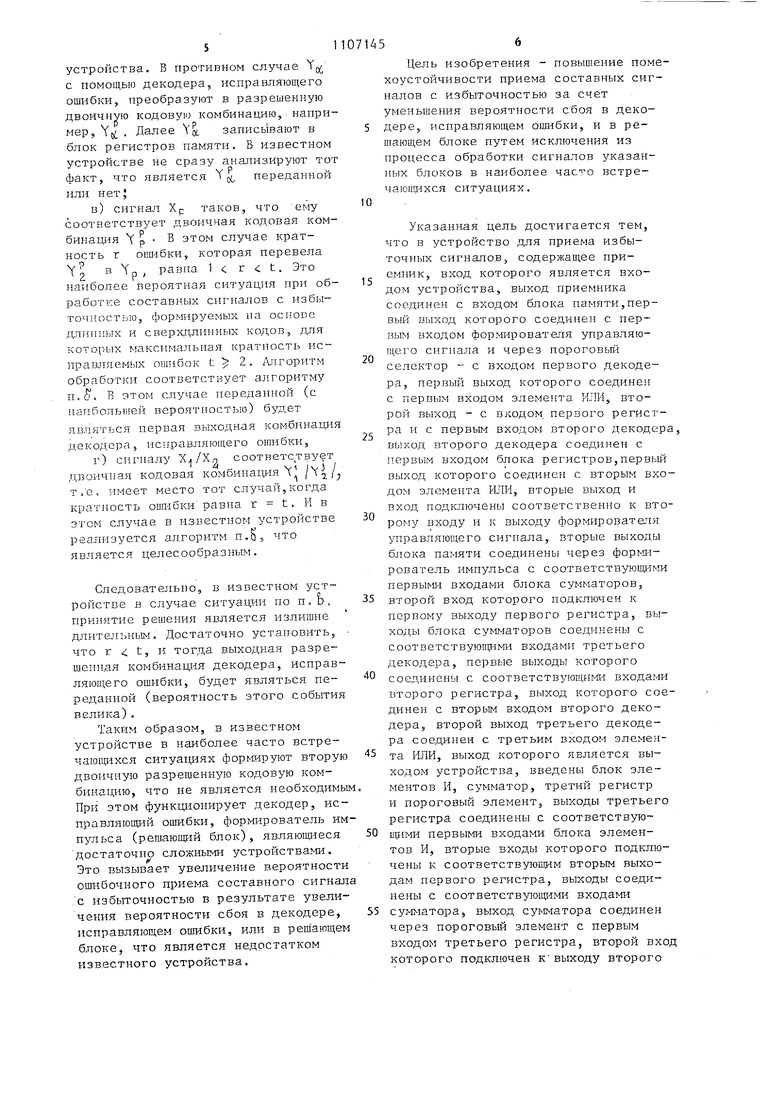

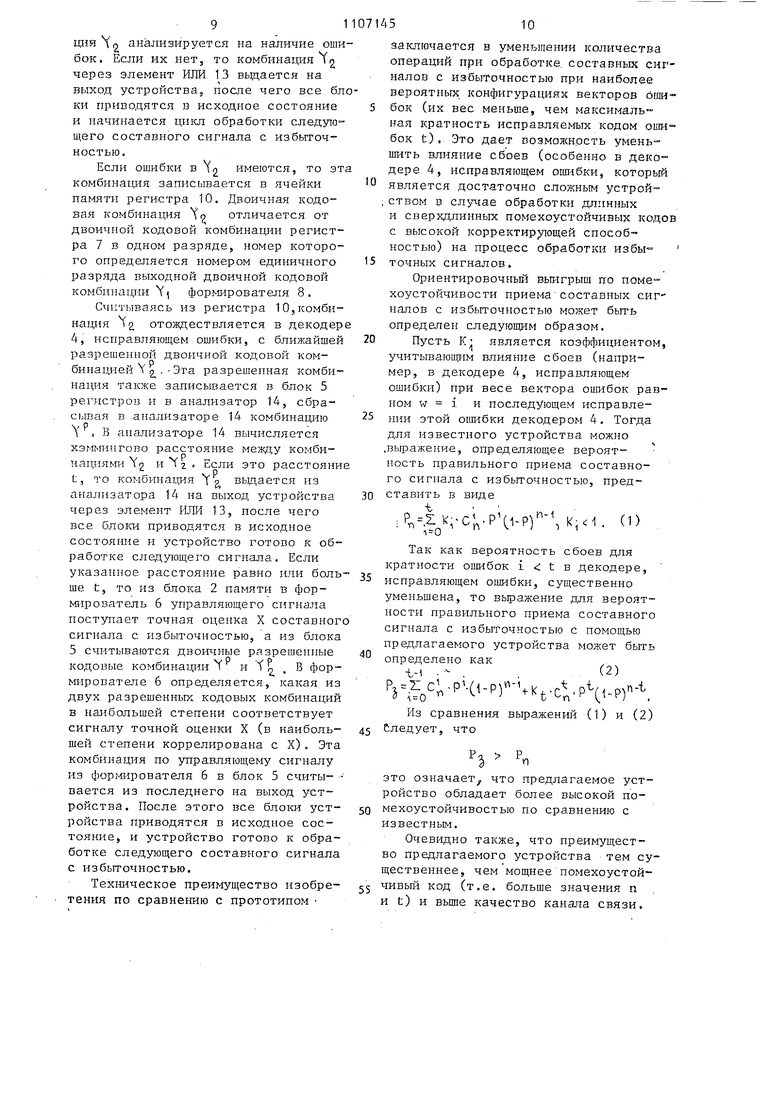

Указанная цель достигается тем, что в устройство для приема избыточных сигналов, содержащее приемник, вход которого является входом устройства, выход приемника соединен с входом блока памяти,первый выход которого соединен с первым входом формирователя управляюш.его сигнала и через пороговый селектор - с входом первого декодера, первый выход которого соединен с первым входом элемента ИЛИ, второй выход - с входом, первого регистра и с первым входом второго декодер выход второго декодера соединен с первым входом блока регистров,первый выход которого соединен с вторым входом элемента ИЛИ, вторые выход и вход подключены соответственно к второму входу и к выходу формирователя управляющего сигнала, вторые выходы блока памяти соединены через формирователь импульса с соответствуюш 1ми первыми входами блока сумматоров, второй вход которого подключен к первому выходу первого регистра, выходы блока сумматоров соединены с соответствующими входами третьего декодера, первые выходы которого соединены с соответствующими входами второго регистра, выход которого соединен с вторым входом второго декодера, второй выход третьего декодера соединен с третьим входом элемента ИЛИ, выход которого является выходом устройства, введены блок элементов И, сумматор, третий регистр и пороговый элемент, выходы третьего регистра соединены с соответствую11Ц5МИ первь№1И входами блока элементов И, вторые входы которого подключены к соответству1ош 1м вторым выходам первого регистра, выходы соединень с соответствутащими входами сумматора, выход сумматора соединен через пороговый элемент с первым входом третьего регистра, второй вход которого подключен квыходу второго декодера, а выход соединен с четвертым входом элемента ИЛИ. На фиг,1 представлена структурн схема устройства для приема избыто ных сигналов| на фиг.2 - геометрическая модель, поясняющая работу устройства. Устройство содержит приемник 1 (аналоговый демодулятор), блок 2 памяти, пороговый селектор 3, декодер 4, исправляющий оиибки,блок регистров, формирователь 6 управляющего сигнала, регистр 7, формирователь 8 импульса, блок 9 сумматоров по модулю, два, регистр 10, декодеры 11 и 12, обнаруясивающте ошибкиJ элемент ИЛИ 13 и анализатор .14, в который входят блок 15 элементов И, регистр 16, сумматор 17 и пороговьп элемент 18. Блок 5 регистров сострит из дву регистров сдвига, в которые последовательно записывают две разрешенные комбинации. По управляющему сигналу из формирователя 6 эти комбинации считываются из блока 5 в формирователь 6. По другому управляющему сигналу комбинация с одного из регистров считывается на выход устройства. Формирователь 6 управляющего си нала определяет ту из двух разреше ных комбинаций блока 5, которая в наибольшей степени коррелировала с аналоговым сигналом X. Формировате 6 выполнен на двух корреляторах и вычитателе. Формирователь 8 импульса опреде ет номер разряда минимального элементарного сигнала с выхода аналогового демодулятора 1 и ставит на его место единичный импульс. Устройство работает следующем о разом. Составной сигнал с избыточност из канала связи поступает в анало вый демодулятор 1, в котором прео разуется в выходн по совокупность разностных элементарных сигналов X (,...,Х), где п - количество элементарньк сигналов в со тавном избыточном сигнале или коли чество двоичных сигналов в кодовы комбинациях. Аналоговая комбинаци запоминается в блоке 2 памяти.Дал аналоговые сигналы Х поступают вход, порогового селектора 3, кото преобразует их в двоичные символы (1 1,п). Ути двоичные символы , образуют двоичную кодовую комбина1ЩЮ ( X,, Ч -2) 1 п) °°Р поступает на декодер 11. Если в декодере 11 не будет обнаружено ошибки, т.е. комбинациях является разрешенргой кодовой комбинацией, то она через элемент ИЛИ 13 выдается на выход устройства, после чего все блоки приводятся в исходное состояние, и устройство готово к обработке следующего входного сигнала. При обнаружении оигибок в Y она подается на вход регистра 7,где запоминается, и на вход декодера 4, в котором отождествляется с ближайшей разрешенной кодовой комбинацией Y Комбинация записывается в блок 5 регистров и в анализатор 14.В анализаторе вычисляют хэм№1нгово рас-р стояние между комбинациями и Ч ., Если это расстояние меньше кратности t исправляемой кодом о1Ш1бки, ToY выдается из анализатора через элемент ИЛИ 13 на выход устройства и все блоки приводятся в исходное состояние, и устройство готово к обработке следующего входн-ого сигнала. В противном случае из буферного блока 2 памяти аналоговые разностные сигналы параллельно считываются в формирователь 8 импульса, в котором определяется наименьший из аналоговых сигналов. На выходе формирователя 8 формируется двоичная кодовая комбинация Т, в которой eдиничнF lй символ находится в разряде с тем же номером, что и наименьший аналоговьш символ. Другие (п-1) разрядов нулевые. После этого из регистра 7 в блок 9 сумматоров по модулю два поступает двоичная кодовая комбинация Y, Номер.единич- ного разряда соответствует номеру наименьшего разностного сигнала на выходе аналогового демодулятора. Б блоке 9 сумматоров суммируются в параллельном коде двоичная кодовая комбинация и поступающая из регистра 7 кодовая комбинация являющаяся грубой оценкой составного сигнала с избыточностью. В результате суммирования на выходе блока 9 образуется двоичная кодовая комбинация YT.. Двоичная кодовая комбинация Ч2 подается в декодер 12, обнаруживающий ошибки. В декодере 12 комбинация Xn анализируется иа наличие ошибок. Если их нет, то комбинахщя g через элемент ИЛИ 13 вьщается на выход устройства, после чего все блки приводятся в исходное состояние и начинается щпсл обработки следующего составного сигнала с избыточностью.

Если ошибки в 2 имеются, то эт комбинация записывается в ячейки памяти регистра 10. Двоичная кодовая комбинация Чгр отличается от двоичной кодовой комбинации регистра 7 в одном разряде, номер которого определяется номером единичного разряда выходной двоичной кодовой комбинации У фop шpoвaтeJIЯ 8.

Считываясь из регистра 10,комбиHaujiK 2 отождествляется в декодер 4, исправляющем ошибки, с ближайшей разрешенной двоичной кодовой комбинацией Y д . Эта разрешенная комбинация также записывается в блок 5 регистров и в анализатор 14, сбрасывая в анализаторе 14 комбинацию , В анализаторе 14 вычисляется ХЭГФ1ИПГОВО расстояние между комбиV vP нациями Хо и г ьсли это расстояни

ч Р

t, ТО комбинация выдается из анализатора 14 на выход устройства через элемент ИЛИ 13, после чего все бло1да приводятся в исходное состояние и устройство готово к обработке следующего сигнала. Если указанное расстояние равно или больше t, то из блока 2 памяти в формирователь б управляющего сигнала поступает точная оценка X составног сигнала с избыточностью, а из блока 5 считываются дво1иные разрешенные кодовые комбинацииY и 2, формирователе б определяется, какая из двух разрешенных кодовых комбинаций в наибольшей степени соответствует сигналу точной оценки X (в наибольшей степени коррелирована с X). Эта комбинация по управляющему сигналу из формирователя 6 в блок 5 считывается из последнего на выход устройства. После этого все блоки устройства приводятся в исходное состояние, и устройство готово к обработке следующего составного сигнала с избыточностью.

Техническое преимущество изобретения по сравнению с прототипом

загшючается в ументэщении количества операций при обработке, составных сигналов с избыточностью при наиболее вероятных конфигурациях векторов дшибок (их вес меньше, чем максималь ная кратность исправляемых кодом ошибок t). Это дает возмолшрсть умень™ шить влияние сбоев (особенно в декоере 4, исправляющем ошибки, который является достаточно сложньгм устрой™ ством в слуггае обработки длинных и сверхдлинных помехоустойчивых кодов с высокой корректирующей способностью) на процесс обработки избы точных сигналов,

Ориентировочньш выигрыш по помехоустойчивости приема составных сигналов с избыточностью может быть определен следующим образом.

Пусть К- является коэффициентом, учитывающим влияние сбоев (например, в декодере 4, исправляющем ошибки) при весе вектора ошибок равном W i и последующем исправлении этой о иибки декодером 4. Тогда для известного устройства можно выражение, определяющее вероятность правильного приема составного сигнала с избыточностью, представить в виде

:p,-.ii,-c;,),i. (1) . (j

Так как вероятность сбоев для кратности ошибок i t в декодере, справляющем ошибки, существенно меньшена, то выражение для вероятности правильного приема составного игнала с избыточностью с помощью редлагаемого устройства может быть определено как

1-1 .-(2)

Р, Г ., .г ,nt/. mn-t

(-pY

П

А 0

выражений (1) и (2)

Из сравнения ледует, что

п

устройство обладает более высокой помехоустойчивостью по сравнению с известным.

Очевидно также, что преимущество предлагаемого устройства тем существеннее, чем мощнее помехоустойчивьш код (т.е. больше значения п и t) и вьше качество канала связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1218415A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU1001147A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1193713A1 |

| Устройство для приема избыточной информации | 1982 |

|

SU1032470A1 |

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1012310A1 |

| Устройство для приема и обработки избыточных сигналов | 1983 |

|

SU1152017A2 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1091210A1 |

| Устройство для декодирования избыточных кодов | 1983 |

|

SU1105927A1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНЫХ СИГНАЛОВ, содержащее приемник, вход которого является входом устройства, выход приемника соединен с входом блока памяти, первый выход которого соединен с первым входом формирователя управляющего сигнала и через пороговый селектор - с входом первого декодера, первьм выход которого соединен с первым входом элемента ИЛИ,второй выход - с входом первого регистра и с первым входом второго декодера, выход второго декодера соединен с первым входом блока регистров, первый выход которого соединен с вторым входом элемента ИЛИ, вторые выход и вход подключены соответственно к второму входу и к выходу формирователя управляющего сигнала, вторые выходы блока памяти соединены через формирователь импульса с соответствующими первыми входами блока сумматоров, второй вход которого подключен к первому выходу первого регистра, выходы блока сумматоров соединены с соответствующими входами третьего декодера, первые выходы которого соединены с соответствующими входами второго регистра, выход которого соединен с вторым входом второго декодера, второй выход третьего декодера соединен с третьим входом элемента РШИ, выход § которого является выходом устройства, отличающееся .тем, что,с целью повьшения помехоустойчивости приема сигналов, в него введены блок элементов И, сумматор, третий регистр и пороговьй элемент, выходы третьего регистра соединены с соответствующими nepBbiNiH вxoдa пi блока к элементов И, вторые входы которого подключены к соответствующим вторымвыходам первого регистра, выходы соединены с соответствующими-вхо 4 СП дами сумматора, выход сумматора соединен через пороговый элемент с первым входом третьего регистра, второй вход которого подключен к выходу второго декодера, а выход соединен с четвертым входом эле мента ИЛИ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М., Советское радио, 1968, с | |||

| Искроудержатель для паровозов | 1920 |

|

SU271A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1984-08-07—Публикация

1983-04-29—Подача