Изобретение относится к электросвязи, а именно к приемным устройствам систем передачи телеметричес:кой информации, использующих .составные сигналм с избыточностью, формиpyeNibie на основе помехоустойчивых кодов Хемминга, и низкоскоростные ( узкополосные )каналы связи высокого качества.

Известно устройство для приема сообщений, передаваемых сложными сигналами на основе избыточных кодов, cocTOHDiee из первой и второй решающих cxeM.fl.

Однако в таком устройстве недостаточно полно используется апостериорная информация о принятом сложном сигнале с избыточностью.

Наиболее близким к предлагаемому по технической сущности является Устройство для приема избыточной информации, .содержащее приемник, выход которого подключен через блок буферной памяти и через послед вательно соединенные первый пороговый селектор, декодер и блок регистров памяти к первому и второму входам блока управления выдачей информации , выход которого подключен к второму входу блока регистра памяти, блок вычитания, усилитель, второй пороговый селектор и последовательно соединенные двоичный регистр сдвига,,сумматор и третий пороговый селектор, выход которого подключен к второму йходу декодера.

(

Данное устройство обеспечивает высокую помехоустойчивость приема информации в высокоскоростных системах передачи телеметрической информации вследствие полного использования апостериорной информации о Выходных элементарных сигналах блока приемника, а также возможносте обрабатывать составные сигналы с избыточностью, формируемые на основе длинных корректирукяцих кодов (сложность устройства с ростом длины кодовых комбинаций увеличивается по закону, близкому к линейному ) 2 .

Однако, вследствие того, что технически очень сложно обеспечить стабильность амплитуд элементарных аиалоговых сигналов при длительном хранении опорного сигнала, устойчивость приема информации данным устрЛйством является низкой..

Ц Нестабильность амплитуд элементарных аналоговых сигналов, определяющих опорный сигнал, hpH прочих-равных условиях ( виде модуляции, параметрах кода, отношении сигналшум на входе устройства и т.д. ) обусловливает уменьшение среднего времени безотказной работы устройства. В данном случае под отказом

понимается ошибочный прием сообще.нчя вследствие искажения опорного .Сигнала, вызванного указанной нестабильностью .

Целью изобретения является повышение надежности и упрощение устройства.

Указанная цель достигается тем-, что в устройство для прргема избыточной информации, содержащее приемник вход которого соединен с входом устройства, выход приемника соединен непосредственно с первым входом первого блока вычитания и через первый пороговый селектор с входом первого двоичного регистра и вторым входам первого блока вычитания, выход которого через первый блок буферной памяти соединен с первыми входами первого блока усилителей, первые выходы первого блока усилителей через второй пороговый селектор соединены с вторым входом первого блока усилителей, вторые выходы которого соединены с первыми входами первого блока сумматоров, вторые входы которого соединены с выходами первого двоичного регистра, второй блок буферной памяти и декодер, введены третий, четвертый и пятый пороговые селекторы, третий и четвертый блоки буферной памяти, второй блок вычитания, второй блок усилителей, второй двоичный регистр, второй блок сумматоров и элемент ИЛИ, первый вход которюго подключен к выходу первого порогового селектора, выход первого блока сумматоров через второй блок буферной памяти соединены с первым входом второго блока вычитания и входом третьего порогового селектора, выход третьег порогового селектора соединен с вторым входом элемента ИЛИ, входом второго двоичного регистра и вторым входом второго блока вычитания, выходкоторого через третий блок буферной памяти соединен с первыми входами второго блока усилителей, первые выходы которого через четвертый пороговый селектор соединены с вторым входом второго блока усилителей , вторые выходы второго блока усилителей соединены с первыми входами второго блока сумматоров, вторые входы которого подключены к выходам второго двоичного регистра, выходаа второго блока сумматоров через последовательно соединенные пятый пороговый селектор и четвертый блок буферной памяти соединены с третьим входом элемента ИЛИ, выход которого через декодер соединен с выходом устройства.

Устройство реализует способ коррекции зоны по методу граничной компенсации.

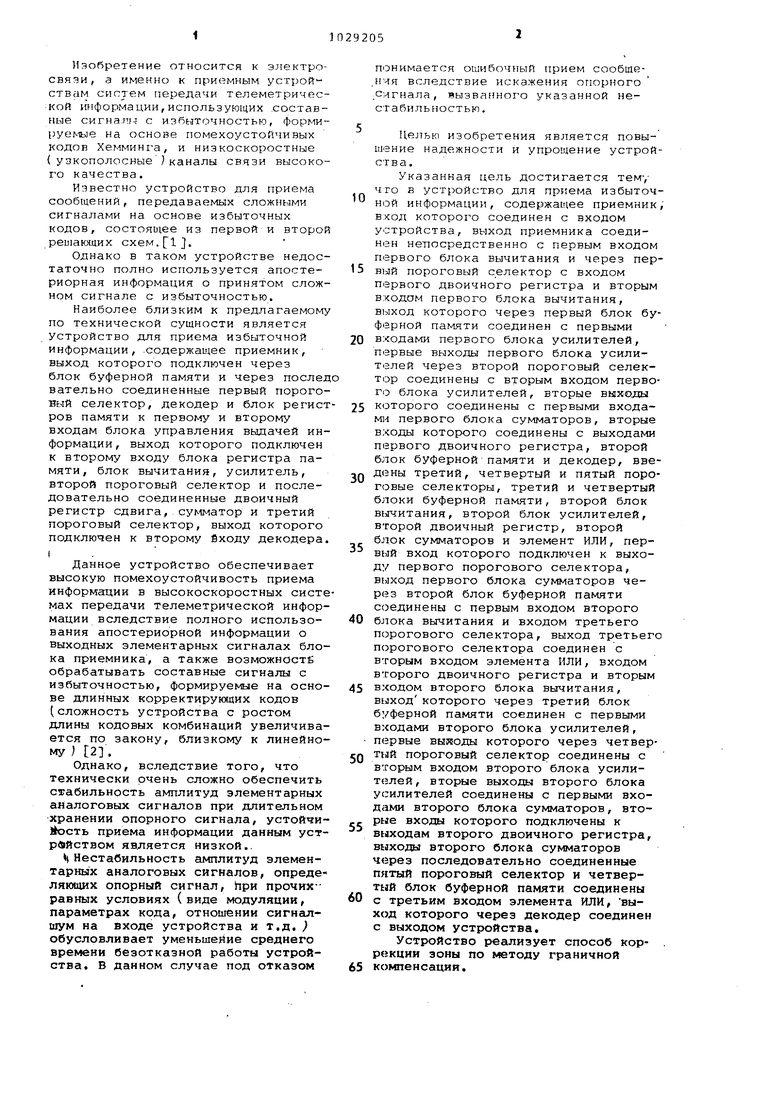

На фиг. 1 изображена структурная схема предлагаемого устройства для приема избыточной информации; на фиг, 2 - геометрически мояели, поясняющие идею функционирования данного устройства.

Физическая сущность предлагаемого устройства заключается в следующем

Г

Вершины куба (фиг. 2) соответ- ствуют двоичным кодовым комбинациям из которых 2 разрешенные. Ребра куба определяют единичные расстояния (по Хеммингу ) между соответствующими вершинами. Кодовое расстояние ( минимальное между разрешенными комбинациями А и равно трем. В виде куба изображено множество сигнальных точек, соответствующих составным аналоговым сигналам на выхо де блока приемника, формируемым на основе двоичного трехзначного кода с минимальным кодовым расстоянием 3.

Алгоритм функционирования, представляющий сущность изобретения, состоит в следующем.

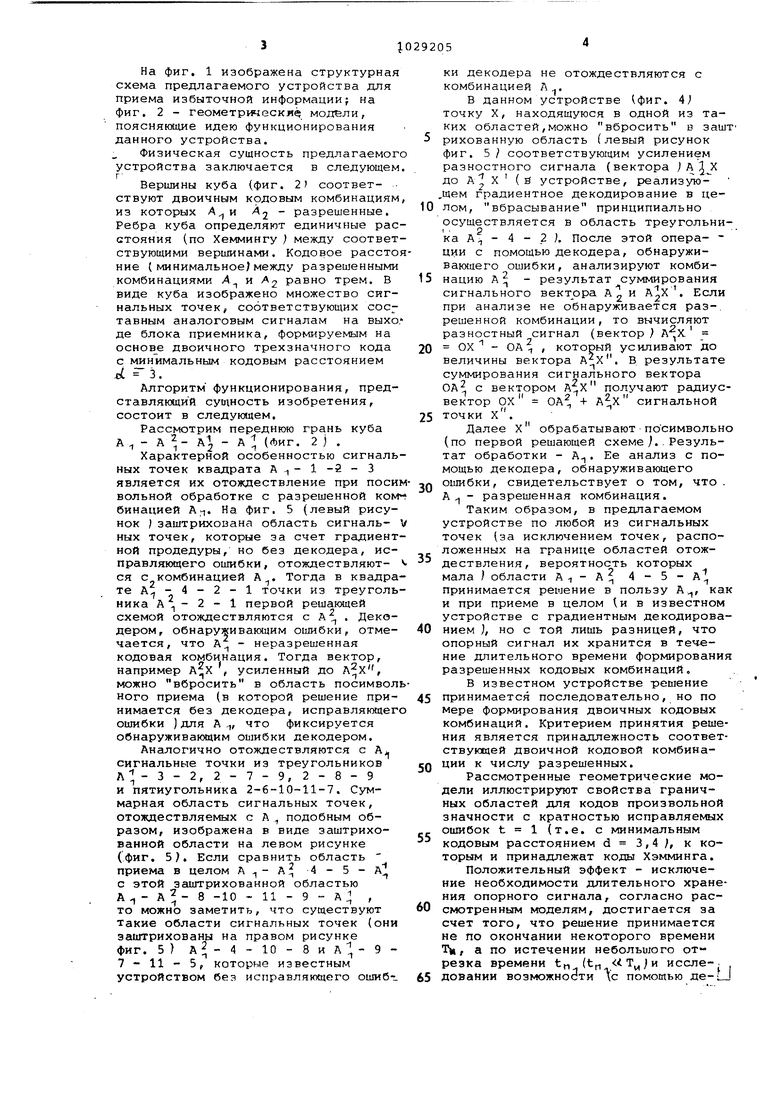

Рассмотрим переднюю грань куба А - А - А - А (Лиг. 2 ) .

Характерной особенностью сигнальных точек квадрата А - 1 -2 - 3 является их отождествление при посимвольной обработке с разрешенной ком бинацией А ч. На фиг. 5 (левый рисунок ) заштрихована область сигналь- V ных точек, которые за счет градиентной продедуры, но без декодера, исправляющего ошибки, отождествляются с комбинацией А. Тогда в квадрате А - 4 - 2 - 1 точки из треугольника А - 2 - 1 первой решающей схемой отождествляются с А . Декодером, обнаруживающим ошибки, отмечается, что А - неразрешенная кодовая комбинация. Тогда вектор, например , усиленный до , можно вбросить в область посимвольного приема (в которой решение принимается без декодера, исправляющего ошибки ) для А , что фиксируется обнаруживающим ошибки декодером.

Аналогично отождествляются с Аи сигнальные точки из треугольников , 2-7-9, 2-8-9 и пятиугольника 2-6-10-11-7. Суммарная область сигнальных точек, отождествляемых с А , подобным образом, изображена в виде заштрихованной области на левом рисунке (фиг. 5). Если сравнить область приема в целом 4-5-А с этой заштрихованной областью А -А -8-10 11-9-А; , то можно заметить, что существуют такие области сигнальных точек (они заштрихованы на правом рисунке фиг. 5) А2-4-10-8иА -97 - 11 - 5, которые известным устройством без исправлякхцего ошибг.

ки декодера не отождествляются с комбинацией Л.

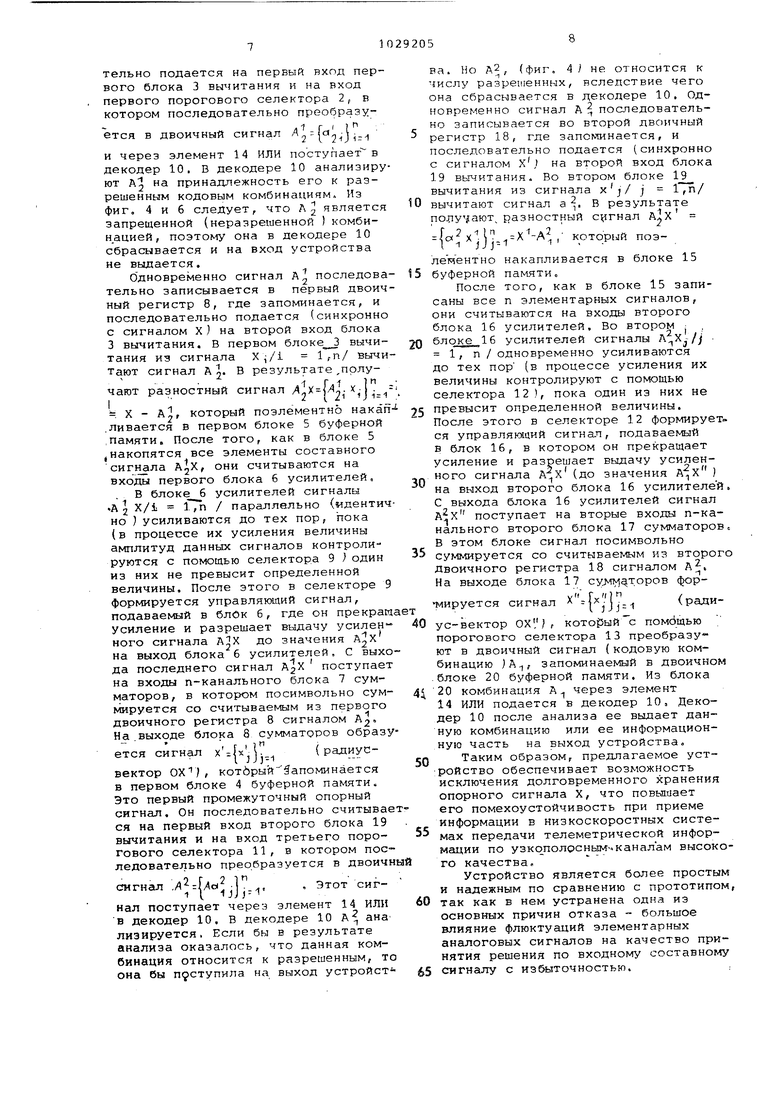

В данном устройстве (фиг. 4) точку X, находящуюся в одной из таких областей,можно вбросить в зашт

5 рихованную область (левый рисунок фиг. 5/ соответствующим усилением разностного сигнала (вектора до А X (и устройстве, реализую,щем градиентное декодирование в целом, вбрасывание принципиально

осуществляется в область треугольниI 2

ка А;, - 4 - 2 . После этой опера-

ции с помощью декодера, обнаруживающего ошибки, анализируют комбинацию А - результат суммирования сигнального вектора Ag и . Если при анализе не обнаруживается раз-. решенной комбинации, то вычисляют разностный сигнал (вектор .

0 - ох - ОА , который усиливают до величины вектора . В результате суммирования сигнального вектора ОА с вектором получают радиусвектор ох ОА + А,х сигнальной

5 точки х.

Далее х обрабатывают посимвольно (по первой решающей схеме/..Результат обработки - А. Ее анализ с помощью декодера, обнаруживакяцего

Q ошибки, свидетельствует о том, что. разрешенная комбинация.

Таким образом, в предлагаемом устройстве по любой нз сигнальных точек (за исключением точек, расположенных на границе областей отождествления, вероятность которых мала I области 4-5- А принимается решение в пользу А, как и при приеме в целом 1и в известном устройстве с градиентным декодированием ), но с той лишь разницей, что опорный сигнал их хранится в течение длительного времени формирования разрешенных кодовых комбинаций. В известном устройстве решение

5 принимается последовательно, но по Мере формирования двоичных кодовых комбинаций. Критерием принятия решения является принадлежность соответствующей двоичной кодовой комбинаQ ции к числу разрешенных.

Рассмотренные геометрические модели иллюстрируют свойства граничных областей для кодов произвольной значности с кратностью исправляег лх ошибок t 1 (т.е. с минимальным

5 кодовым расстоянием d 3,4 , к которым и принадлежат коды Хэмминга. Положительный эффект - исключение необходимости длительного хранения опорного сигнала, согласно рассмотренным моделям, достигается за счет того, что решение принимается не по окончании некоторого времени Тц, а по истечении небольшого отрезка времени t, (t Т j и исследовании возможности с помощью де-LJ

кодера, обнаруживающего оишбкиу принятия решения. Если решение не принимается, то в течение времени t (tng Т( формируется другая двоичная комбинация, анализируется и т.д. Суммарное время хранения аналогичных сигналов есть

И t

Pi I

1-1

вследствие того, что tj;; . « Т , устойчивость работы предлагаемого устройства выше по сравнению с известным. По этой причине время наработки на отказ в данном устройст -ве также больше, но технически оно проще.

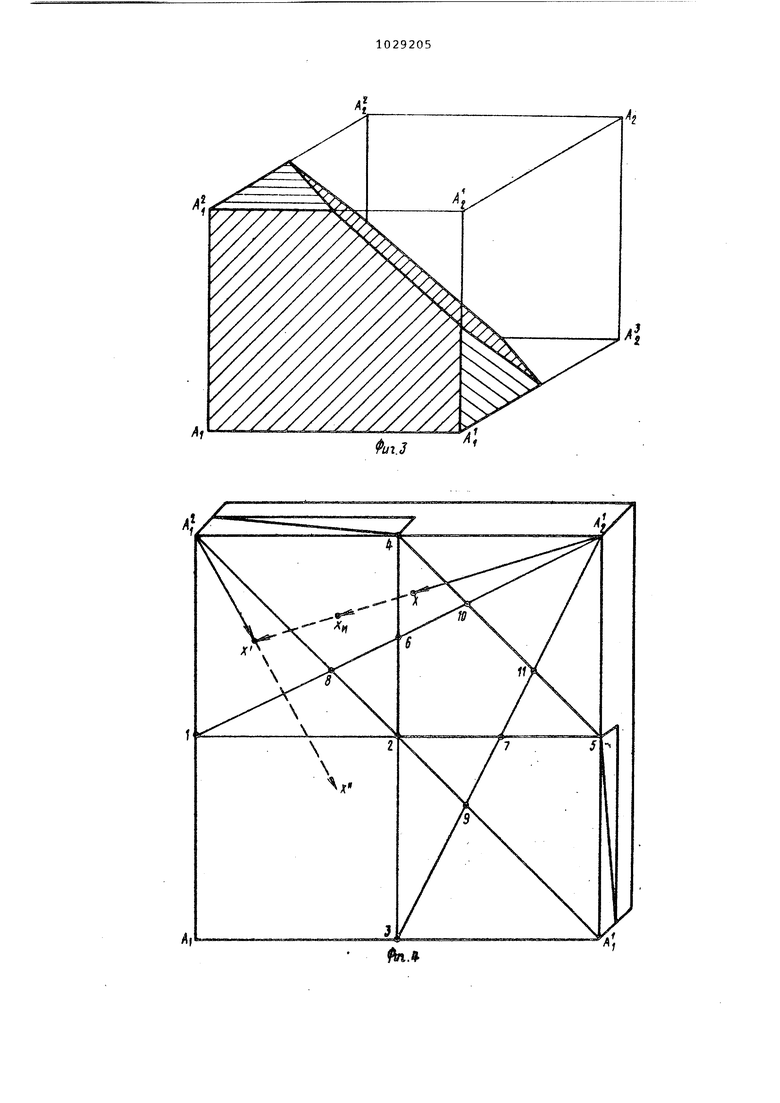

Устройство для приема избыточной информации (фиг. 1 содержит бпокиf входящие в состав известного устройства-прототипа, приемник 1, прео разующий элементарные сигналы ), входящие в состав сложного избыточi .Г )п

ного сигнала 3(t) 5i{tn. , В

аналоговые элементарные сигналы х , определяющие аналоговый составной

.

сигнал с избыточностью Х-ГлЛ.

I J1-1

Алгоритм указанного преобраэойания в приемнике 1 определяется способом приема элементарных сигналов, видом модуляции и т.п. С помощью первого порогового селектора 2, аналоговые сигналы,преобразуются в двоичные. Амплитуда единичного двоичного сигнала определяется величиной отношения сигнал-шум на входе приемника 1 и параметрами избыточного кода. С помощью первого блока 3 вычитания из величины входных элементарных аналоговых сигналов - 1,п/ блока 2 вьгчитают соответствующие двоичные сигналы {выходные для блока 2 ) aji. В результате получают разностные сигналы r-ji , (одие сигнал А X rOX-0 2 i .

В блоке 4 буферной памяти хранится аналоговый сигнал AjX, который в данный блок записывается параллельно, а считывается последовательно (со скоростью во много раз превышающей скорость модуляции ), БлагоЙ ря этому время хранения составногсх аналогового сигнала в блоке 4 майо. В блоке 5 буферной памяти хранится аналоговый сигнал , который поступает в блок 6 Усилителей, содержащий п одноразрядных усилителей элементарных сигналов (аналоговых }, считываемых из блока 5. Усилн ваемые сигналы подаются на вход второго порогового селектора, а с его выхода на другой вход блока .6

усилителей. Усиленный разностн 4й сиг Нал с выходов блока 6 параллельно подается на входы блока 7 сумматоров, который содержит п одноразрядных сумматоров. С помощью данного блока осуществляется поразрядное Суммирование вектора ОА с вектором AjX . На Выходе блока 7 получают радиус-вектор ОХ ОА + .

Устройство содержит также двоичный регистр первый 8, второй пороговый селектор 9 и декодер 10. Режим функционирования блока 10 отличается от режима функционирования аналогичного блока известного устройства. В известном устройстве

декодер исправляет ошибки (отождествляет двоичные кодовые комбинации с разрешенными комбинациямиj. Поэтому декодер известного устройства пред- .

Q ставляет собой сложное логическое устройство. -В предлагаемом устройстве декодер 10 лишь обнаруживает ошибки {проверяет - является ли данная двоичная комбинация разрешенной или нет ), вследствие чего представляет собой своеобразный .Е.ешифратор несло ное устройство). С помощью данного блока в новом устройстве проверяют принадлежность к разрешенным кодовым комбинациям

поочередно А , А и А.

Блок управления и синхронизации на фиг, 1 не изображен, так как он не определяет сущности изобретения .

5 Дополнительно в устройство введены третий, четвертый и пятый поЕюговые селекторы 11, 12 и 13, устроенные также, как и пороговые селекторы 2 и 9, с помощью которых

0 также элементарные аналоговые сигналы преобразуются в двоичные; элемент ИЛИ 14, третий блок 15 буферной памяти} второй блок 16 усилителей, содержащий п одноразрядных уси

5 лителей аналоговых элементарных

(:игналов второй блок 17 сумматоров, содержащий п одноразрядных сумматоров второй двоичный регистр 18, вто рой блок 19 вычитания и четвертый

- блок 20 буферной памяти.

Устройство работает следующим образом.

На вход устройства поступает составной сигнал с избыточностью, сфор, 1/1ированный на основе комбинации А

двоичного трехзначного кода с минимальным кодовым расстояние м, трем (фиг. 4 и б-Г 5{t))j. .

(столь короткий код выбран исключигел|зно из-за простоты и наглядности излЬжения работы устройства ), С погжэщьго приемника 1 сигнал S(t; пре- образуют в составной сигнал

- , п

-i iJi-1 Сигнал X последовательно подается на первый вход первого блока 3 вычитания и на вход первого порогового селектора 2, в котором последовательно преобразу-) г I ; П ется в двоичный сигнал i iJ i-i и через элемент 14 ИЛИ поступает в декодер 10, В декодере 10 анализиру ют Aj на принадлежность его к разрешенным кодовым комбинациям. Из фиг, 4 и 6 следует, что Ag является запрещенной (неразрешенной ) комбин,ацией, поэтому она в декодере 10 сбрасывается и на вход устройства не вьадается. Одновременно сигнал А последова тельно записывается в первый двоич ный регистр 8, где запоминается, и последовательно подается (синхронно с сигналом X) на второй вход блока 3 вычитания. В первом блоке 3 вычитания из сигнала 1гП/ вычи тают сигнал А j. В результате ,получают разностный сигнал 4т. х j I / (. /1 J Ц X - А, который поэлементно накап .ливается в первом блоке 5 буферной памяти. После того, как в блоке 5 накопятся все элементы составного сигнала AjX, они считываются на входы первого блока 6 усилителей, В блоке б усилителей сигналы А 2 X/i l7n / параллельно (идентич но } усиливаются до тех пор, пока (в процессе их усиления величины амплитуд данных сигналов контролируются с помощью селектора 9 ) один из них не превысит определенной величины. После этого в селекторе 9 формируется управляюший сигнал, подаваемый в блок 6, где он прекращ усиление и разрешает выдачу усиленного сигнала до значения на выход блока 6 усилителей. С выхо да последнего сигнал AjX поступает на входы п-канального блока 7 сумматоров, в котором посимвольно суммируется со считываемым из первого двоичного регистра 8 сигналом А2. На.выходе блока 8 сумматоров образу (раД УСется сигнал X -) вектор ОХ ) , кот6рый : апоминается в первом блоке 4 буферной памяти. Это первый промежуточный опорный сигнал. Он последовательно считывае ся на первый вход второго блока 19 вычитания и на вход третьего порогового селектора 11, в котором пос ледовательмо преобразуется в двоичн r{-1jj,.1 сигнал .(А , Этот сигнал поступает через элемент 14 ИЛИ в декодер 10. В декодере 10 А ана лизируется. Если бы в результате анализа оказалось, что данная комбинация относится к разрешенным, то она бы П9ступила на выход устройств ва. Но А2, (фиг. 4 I не относится к числу разрешенных, вследствие чего она сбрасывается в декодере 10, Одновременно сигнал А последовательно записывается во второй двоичный регистр 18, где запоминается, и последовательно подается (синхронно с сигналом Xj на второй вход блока 19 вычитания. Во втором блоке 19 вычитания из сигнала xj/ j вычитают сигнал а 2, в результате разностный Alx о Х. 1. , который поэлементно накапливается в блоке 15 буферной памяти. После того, как в блоке 15 записаны все п элементарных сигналов, они считываются на входы второго блока 16 усилителей. Во втором усилителей сигналы . 1, п / одновременно усиливаются до тех пор (в процессе усиления их величины контролируют с помощью селектора 12), пока один из них не превысит определенной величины. После этого в селекторе 12 формируется управлякяций сигнал, подаваемый в блок 16, в котором он прекращает усиление и разрешает выдачу усиленного сигнала (до значения ) на выход второго блока 16 усилителей. С выхода блока 16 усилителей сигнал поступает на вторые входы п-канального второго блока 17 сумматоровВ этом блоке сигнал посимвольно суммируется со считываемым из второго Двоичного регистра 18 сигналом На выходе блока 17 су пи1 т;оров формируется сигнал PiJi-i (радиус-вектор ОХ ,1, который с помбщью порогового селектора 13 преобразу ют в двоичный сигнал { кодовую комбинацию )А,. запоминаемый в двоичном блоке 20 буферной памяти. Из блока 20 комбинация А,, через элемент 14 ИЛИ подается в декодер 10, Декодер 10 после анализа ее выдает данную комбинацию или ее информационную часть на выход устройства. Таким образом, предлагаемое устройство обеспечивает возможность исключения долговременного хранения опорного сигнала X, что повышает его помехоустойчивость при приеме информации в низкоскоростных системах передачи телеметрической информации по узкополосным-каналам высокого качества. Устройство является более простым и надежным по сравнению с прототипом, так как в нем устранена одна из основных причин отказа - большое влияние флюктуации элементарных аналоговых сигналов на качество принятия решения по входному составному сигналу с избыточностью.

Данное устройство наиболее целесообразно использовать в системах . передачи телеметрической информации об объектах или процессах, имеющих важное технологическое значение,

параметры ( характеристики ) которых изменяются во времени чрезвычайно медленно, вследствие чего для передачи информации о них в общем тракте отводится узкая полоса частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема избыточной информации | 1981 |

|

SU978373A1 |

| Устройство для приема избыточной информации | 1982 |

|

SU1032470A1 |

| Устройство для приема и передачи избыточных сигналов | 1981 |

|

SU976466A1 |

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1001145A1 |

| Адаптивное устройство для приема избыточной информации | 1981 |

|

SU1012310A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU1001147A1 |

| Устройство для приема избыточных сигналов | 1983 |

|

SU1107145A1 |

| Некогерентный приемник | 1981 |

|

SU1003370A1 |

| Устройство для приема избыточной информации | 1988 |

|

SU1557578A2 |

| Устройство для приема и градиентного декодирования избыточных сигналов | 1983 |

|

SU1152016A1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА ИЗБЫТОЧНОЙ ИНФОРМАЦИИ, содержащее Приемник, вход которого соединен с входом устройства, выход приемника соединен непосредственно с первым входом первого блока вычитания и через первый пороговый селектор с входом первого двоичного регистра и вторым входом первого блока вычитания, выход которого через первый блок бу- ферной памяти соединен с первыми входами первого блока усилителей, первые выходы первого блока усилителей через второй пороговый селектор соединены с вторым входом первого блока усилителей, вторые выходы которого соединены с первыми входами первого блока сумматоров, вторые входы которого соединены с выходс1ми первого двоичного регистра, второй блок буферной памяти и декодер, от личающееся тем, что, с целью повышения надежности и упрощения устройства , в него введены третий, четвертый и пятый пороговые селекторы, третий и четвёртый блоки буферной памяти, второй блок вычйтания, второй блок усилителей, второй двоичный регистр, второй блок сумматоров и элемент ИЛИ, первый вход которого подключен к выходу--первого порогового селектора, выход первого блока сумматоров через второй блок буферной памяти соединен с первым входом второго блока вычитания и входом третьего порогового селектора, выход третьего порогового селектора соединен с вторым входом элемента ИЛИ, входом второго двоичного регистра и вторым входом второго блока вычитания, выход которого через третий блок буферной памяти соединен с первыми входами второго блока усилителей, первые выходы которого четвертый пороговый селектор соединены с вторым . входом второго -блока усилителей, вторые выходь второго блока усилителей соединены с первыми входаки второго блока сумматоров, вторые входы которого подключены к выходам ю ;о ю второго двоичного регистра, выходы второго блока сумматоров через последовательно соединенные пятый порого вый селектор и четвертый блок буфер«ой памяти соединены с третьим вхог. дом элемента ИЛИ, выход которого через декодер соединен с выходом устройства.

Й/7.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бородин Л.Ф | |||

| Введение в теорию помехоустойчивого кодирования | |||

| М | |||

| , Советское радио, 1968, с.271 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для приема избыточнойиНфОРМАции | 1979 |

|

SU824263A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1983-07-15—Публикация

1981-12-29—Подача