1

Изобретение относится к автоматике и вычислительной технике.

Известны устройства для кодирования сообщений с исправлением симметрических ошибок типа замещения символов, содержащие двоичный регистр сдвига, сумматоры и переключатели 1. Однако во многих случаях применения устройств автоматики вероятности повреждения различных символов в каналах связи неодинаковы, т.е. имеют место несимметрические ошибки. В этих случаях применение известных устройств неэффективно, так как использование специализированных кодирующих устройств для несимметричных каналов приводит к увеличению быстродействия и скорости передачи информации. Наиболее близким к изобретению техническим решением является устройство для кодирования сообщений с исправлением одиночных несимметрических ошибок, содержащее вычислительный блок, первый вход которого соединен с выходом блока управления, вход блока управления является входом устройства 2. Мощности кодов, реализуемых этим устройством, сравнительно малы, а их корректирующие возможности - «изки. Устройство позволяет строить коды, исправляющие только одиночные или две соседние несимметрические ошибки.

Целью изобретения является повышение достоверности информации. В описываемом устроистве это достигается тем, что в него введены блок банка слов, блок д-х регистров, блок памяти и блок результата, причем входы и выходы блока банка слов, блока д-х регистров и блока памяти соединены с тремя выходами и вторым, третьим и четвертым входами вычислительного блока, второй выход блока памяти через блок результата соединен с пятым входом вычислительного блока, четвертый выход которого является выходом устройства.

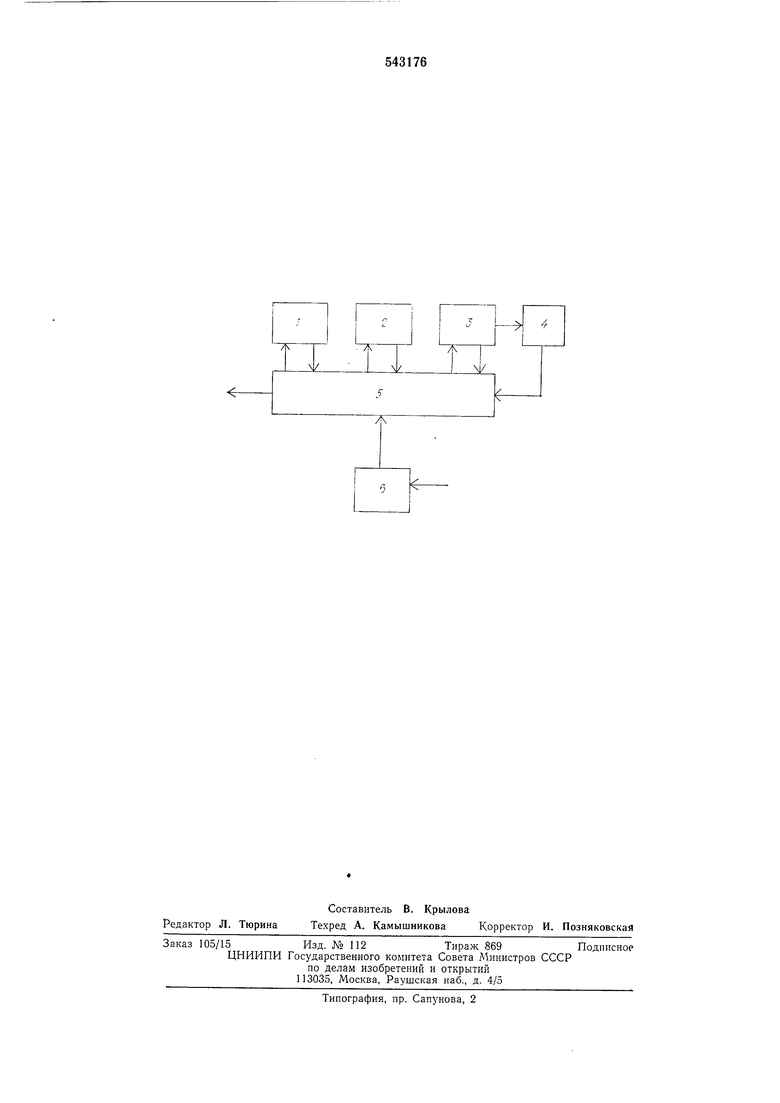

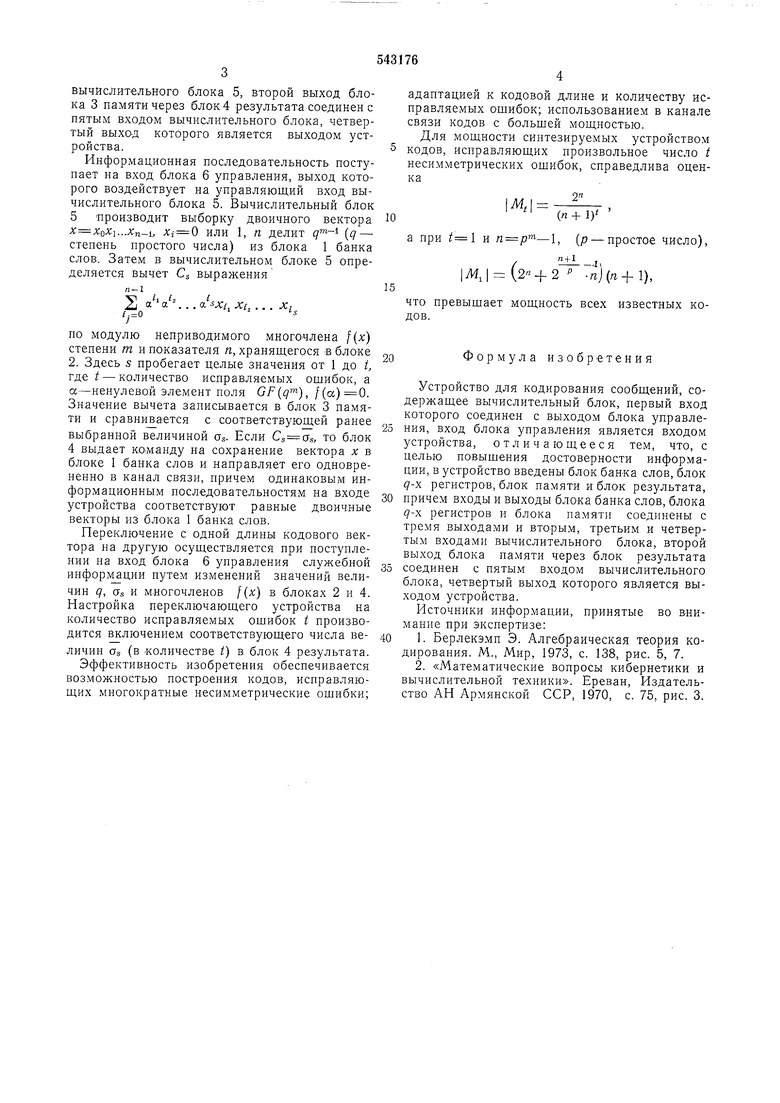

На чертеже представлена блок-схема описываемого устройства.

Оно содержит блок 1 банка слов, предназначенный для хранения кодовых слов, блок 2 д-х регистров, где хранятся неприводимые -х многочлены, служащие для представления конечного тюля, блок 3 памяти, в котором записываются результаты анализа векторов. Эти результаты сравниваются с выбранными заранее значениями соответствующих параметров в блоке 4 результата. Все кодирующие операции осуществляются вычислительным блоком 5, а функционирование устройства в целом обеспечивается блоком 6 управления. Первый вход вычислительного блока 5 соединен с выходом блока 6 управления, вход которого является входом устройства. Входы и выходы блока 1 банка слов, блока 2 д-х регистров, блока 3 памяти соединены соответственно с тремя выходами и вторым, третьим и четвертым входами

вычислительного блока 5, второй выход блока 3 памяти через блок 4 результата соединен с пятым входом вычислительного блока, четвертый выход которого является выходом устройства.

Информационная последовательность поступает на вход блока 6 управления, выход которого воздействует на управляющий вход вычислительного блока 5. Вычислительный блок 5 производит выборку двоичного вектора ...Xn--i, или 1, п делит д (q - степень простого числа) из блока 1 банка слов. Затем в вычислительном блоке 5 определяется вычет Cs выражения

2 я я ... Х, . , . Xi

i.o

по модулю неприводимого многочлена f(x) степени m и показателя п, храняидегося в блоке 2. Здесь .S пробегает целые значения от 1 до /, где t - количество исправляемых ошибок, а а,-ненулевой элемент поля GF(™), /(сб)0. Значение вычета записывается в блок 3 памяти и сравнивается с соответствующей ранее выбранной величиной as. Если , то блок 4 выдает команду на сохранение вектора х в блоке I банка слов и направляет его одноврененно в каиал связи, причем одинаковым информационным последовательностям на входе устройства соответствуют равные двоичные векторы из блока 1 банка слов.

Переключение с одной длины кодового вектора на другую осуществляется при поступлении иа вход блока 6 управления служебной информации путем изменений значений величин q, Os и многочленов f(x) в блоках 2 и 4. Настройка переключающего устройства на количество исправляемых ошибок t производится включением соответствующего числа величин 0S (в -количестве t) в блок 4 результата.

Эффективность изобретения обеспечивается возможностью построеиия кодов, исправляющих многократные несимметрические ошибки;

адаптацией к кодовой длине и количеству исправляемых ошибок; использованием в канале связи кодов с большей мощностью.

Для мощности синтезируемых устройством кодов, исправляющих произвольное число t несимметрических ошибок, справедлива оценка

on

I Л --- ,

(«+)

а при 1 и , (р - простое число),

/l±L.i,

|Ж,(2«+2 -njin+l),

что превыщает мощность всех известных кодов.

Формула изобретения

Устройство для кодирования сообщений, содержащее вычислительный блок, нервый вход которого соединен с выходом блока управлеВИЯ, вход блока управления является входом устройства, отличающееся тем, что, с целью повышения достоверности информации, в устройство введены блок банка слов, блок q-x регистров, блок памяти и блок результата,

причем входы и выходы блока банка слов, блока q- регистров и блока памяти соединены с тремя выходами и вторым, третьим и четвертым входами вычислительного блока, второй выход блока иамяти через блок результата

соединен с пятым входом вычислительного блока, четвертый выход которого является выходом устройства.

Источники информации, принятые во внимание при экспертизе:

1. Берлекэмп Э. Алгебраическая теория кодирования. М., Мир, 1973, с. 138, рис. 5, 7.

2. «Математические вопросы кибернетики и вычислительной техиики. Ереван, Издательство АН Армянской ССР, 1970, с. 75, рис. 3.

f A

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования сообщений | 1974 |

|

SU543177A1 |

| Запоминающее устройство с исправлением ошибок | 1984 |

|

SU1226536A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Устройство декодирования с исправлением ошибок | 1985 |

|

SU1293855A1 |

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

| Устройство для исправления ошибок | 1986 |

|

SU1387202A2 |

| Устройство кодирования и вычисления синдромов помехоустойчивых кодов для коррекции ошибок во внешней памяти ЭВМ | 1989 |

|

SU1656689A1 |

Авторы

Даты

1977-01-15—Публикация

1974-12-11—Подача