1

Изобретение относится к радиотехнике н может использоваться для разделения во времени двух последовательностей случайных импульсов.

Известно устройство, содержащее генератор тактовых импульсов, который опрашивает элементы, линии задержки, триггеры, логические схемы И и ИЛИ 1.

Однако в известном устройстве импульсы иа выходах запаздывают относительно импульсов, поступающих на входы, на время до одного периода следования импульсов тактового генератора.

Наиболее близким техническим решением к изобретсиию является устройство для синхронизации случайных импульсов, содерл ащее первый триггер, вход которого соединен с выходом первой линии задержки, а единичный выход через первый элемент И соединен с одним из входов элемента ИЛИ, и второй триггер, вход которого соединен с выходом второй линии задержки, а единичный выход - с одним из входов второго элемента И 2.

Однако известное устройство обладает недостаточно высокой точностью синхронизации при записи и считывании информации.

Цель изобретения - иовышение точности синхронизации при записи - считываиии информации.

Для этого в предлагаемое устройство для

синхронизации случайных импульсов введены первый и второй формирователи, первый и второй ииверторы, и схема совпадения, ири этом к входам схемы совпаденпя подключены

соответственно выход элемента ИЛИ через последовательно соединенные первый формирователь и первый инвертор, нулевой выход первого триггера - через последовательно соединениые второй элемент И, второй формнрователь и второй инвертор, а единичные выходы иервого и второго триггеров - иеиосредственно, при этом выход схемы совпаденпя соединен с другим входом элемента ИЛИ, выходы первого и второго формирователей - с входами соответствующих линий задержки, а нулевой выход второго триггера - с вторым входом первого элемента И.

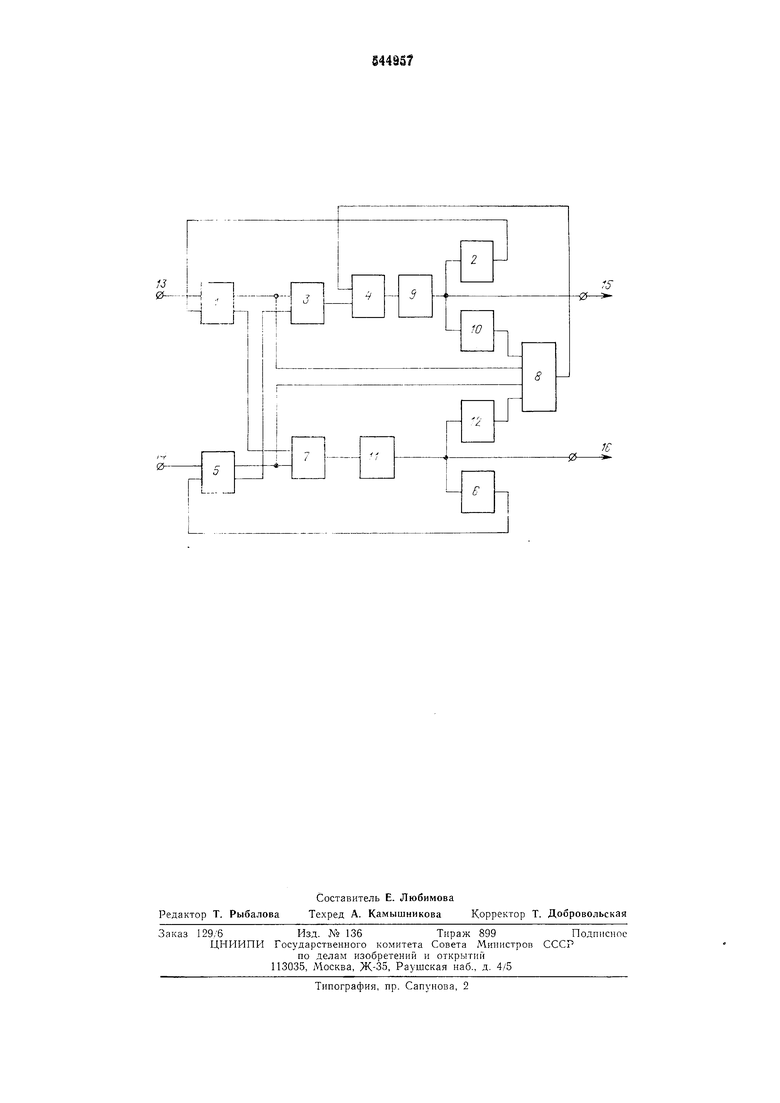

На чертеже нриведена структурная электрическая схема устройства.

Устройство для синхронизации случайных импульсов содержит первый триггер 1, вход которого соединен с выходом иервой линии задержки 2, а единичный выход через первый элемент PI 3 соединен с входом элемента

ИЛИ 4, и второй триггер 5, вход которого соединен с выходом второй линии задержки 6, а единичный выход - с входом второго элемента И 7, а также схему совпадения 8, к входам которой подключены соответственно

выход элемента ИЛИ 4 через иоследовательно

соединенные первый формирователь 9 и первый инвертор 10, нулевой выход триггера 1 - через последовательно соединенные второй элемент И 7, второй формирователь 11 и инвертор 12, а единичные выходы первого и второго триггеров 1 и 5 - непосредственно. Выход схемы совпадения 8 соединен с одним из входов элемента ИЛИ 4, выходы первого и второго формирователей 9 и 11 - с входом соответствующей лннпп задержки 2 п 6, а нулевой выход второго триггера 5 - с одним из входов первого элемента И 3, причем входы первого и второго триггеров 1, 5 являются входами 13 и 14 устройства, а выходы первого и второго формирователей 9, 11 - выходами 15 и 16 устройства.

Устройство работает следующим образом.

При поступлении импульса на вход 13 раньше, чем на вход 14, триггер 1 устанавливается в положение «1. Потенциалы с единичного выхода триггера 1 и нулевого выхода триггера 5 поступают на первый элемент И 3, с выхода которого через элемент ИЛИ 4 - на вход первого формирователя 9. С выхода формирователя 9 через первый инвертор 10 поступает запрет на работу схемы совпадения 8, и потенциал, кроме того, пройдя первую линию задержки 2, возвращает первый триггер в исходное состояпие. При поступлении импульса на вход 13 раньше, чем на вход 12 симметричный канал устройства работает аналогично.

При одновременном появлении импульсов на входах 13 и 14 устройства приоритетным является имиульс на входе 13. Потенциалы с нулевых выходов первого и второго триггеров 1 и 5 запрещают работу первого и второго элементов PI 3, 7. Одновременно потенциалы с единичных выходов первого и второго триггеров поступают на входы схемы совпадения 8. Так как формирования импульсов не происходит, то первый и второй инверторы 10 и 12 разрешают работу схемы совпадения 8, и через элемент ИЛИ 4 запускается первый формирователь 9. После формирования импульса на выходе 15 первый триггер обнуляется и работает другой канал через второй элемент И 7.

При появлении импульса иа входе 14 во время формирования импульса на выходе 15 происходит запоминание вторым триггером 5 импульса, пришедшего на вход 14, и после

того, как первый триггер 1 устанавливается е исходное состояние, начинается формирование импульса на выходе 16. С появлением импульса на входе 13 во время формирования

импульса на выходе 16 происходит запоминание первым триггером импульса, пришедшего на вход 13, и после того, как второй триггер устанавливается в исходное состояние, начинается формирование импульса на выходе 15.

Таки.м образом, синхронизация случайных импульсов производится логически без временной прпвязки к импульсам тактового генератора, а уменьшение временной задержки между входными и выходными импульсами -

за счет уменьшения времени прохождения импульсов через устройство.

Формула изобретения

Устройство для синхронизации случайных

импульсов, содержащее первый триггер, вход которого соединеп с выходом первой лииии задержки, а единичный выход через первый элемент И соединен с одним из входов элемента ИЛИ, и второй триггер, вход которого

соединен с выходом второй линии задержки, а единичный выход - с одним из входов второго элемента И, отличающееся тем, что, с целью повышения точностн синхронизации при записи-считывании информации, введены

первый и второй формирователи, первый и второй инверторы, и схема совпадения, при этом к входам схемы совпадения подключены соответственно выход элемента ИЛИ через последовательно соединенные первый формирователь и первый инвертор, пулевой выход первого триггера - через последовательно соединенные второй элемент Pi, второй формирователь и второй инвертор, а единичные выходы первого и второго триггеров - пепосредственпо, при этом выход схемы совпадения соединеп с другим входом элемента ИЛИ, выходы первого и второго формирователей - с входами соответствующих липий задержки, а нулевой выход второго триггера - с вторым входом первого элемента И.

Источники информации, принятые во внимание при экспертизе:

1. Патент Франции JY 2112751, кл. Н ОЗК 5/00, 1972.

2. Авт. св. К° 224898, кл. G 06F 1/04, 1967.

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов по переднему и заднему фронту входного импульса | 1973 |

|

SU455468A1 |

| Формирователь импульсов | 1979 |

|

SU813733A1 |

| Устройство для моделирования процесса появления отказов в двоичном элементе | 1973 |

|

SU474011A1 |

| Устройство передачи и приема информации | 1991 |

|

SU1793454A1 |

| Преобразователь время-код | 1991 |

|

SU1785073A1 |

| Формирователь импульсов | 1979 |

|

SU839034A1 |

| Логический селектор импульсов по длительности | 1976 |

|

SU650224A1 |

| Формирователь импульсов | 1981 |

|

SU1045371A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU764112A1 |

Авторы

Даты

1977-01-30—Публикация

1975-01-28—Подача