(54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНО-ШЕСТИДЕСЯТИРИЧНЫЙ КОД

1

Изобретение относится к области автоматики и цифровой вычислительной техники и может быть использовано при построении двоично-десятичных преобразователей.

Известен двоично-десятичный преобразователь, содержащий входной регистр, информационные входы которого подключены к входным шинам, генератор импульсов, выходной сумматор, выходы которого соединены с выходными шинами, дешифратор, переключатель эквивалентов, один из выходов которого соединен с управляющим входом выходного сумматора, элемент И, соединенный входами с генератором тактовых импульсвв и дешифратором, дешифратор нуля, связанный с выходами входного регистра, последовательно соединенные блок анализа, формирователь адреса и накопитель, дешифратор, подключенный входами к накопителю, а выходами - к блоку анал.иза и формирователю адреса, переключатель эквивалентов, связанный с выходным регистром и формирователем адреса, соединенным с выходом элемента И, причем входы блока анализа соединены с выходами входного регистра, а выходы накопителя - со входами выходного сумматора 1.

Недостаток этого преобразователя состоит в большом количестве и неполной загрузке оборудования, так как в накопителе необходимо хранить весовые коэффициенты для каждого типа преобразования. Например, для преобразования двоичного кода в двоично-десятичный требуются одни весовые коэффициенты, а для преобразования двоичного кода в двоично-десятично-щестидесятиричный - другие, а одновременно может осуществляться только один тип пре10 образования.

Таким образом, в данном преобразователе расширение функциональных возможностей достигается за счет увеличения емкости

,, накопителя.

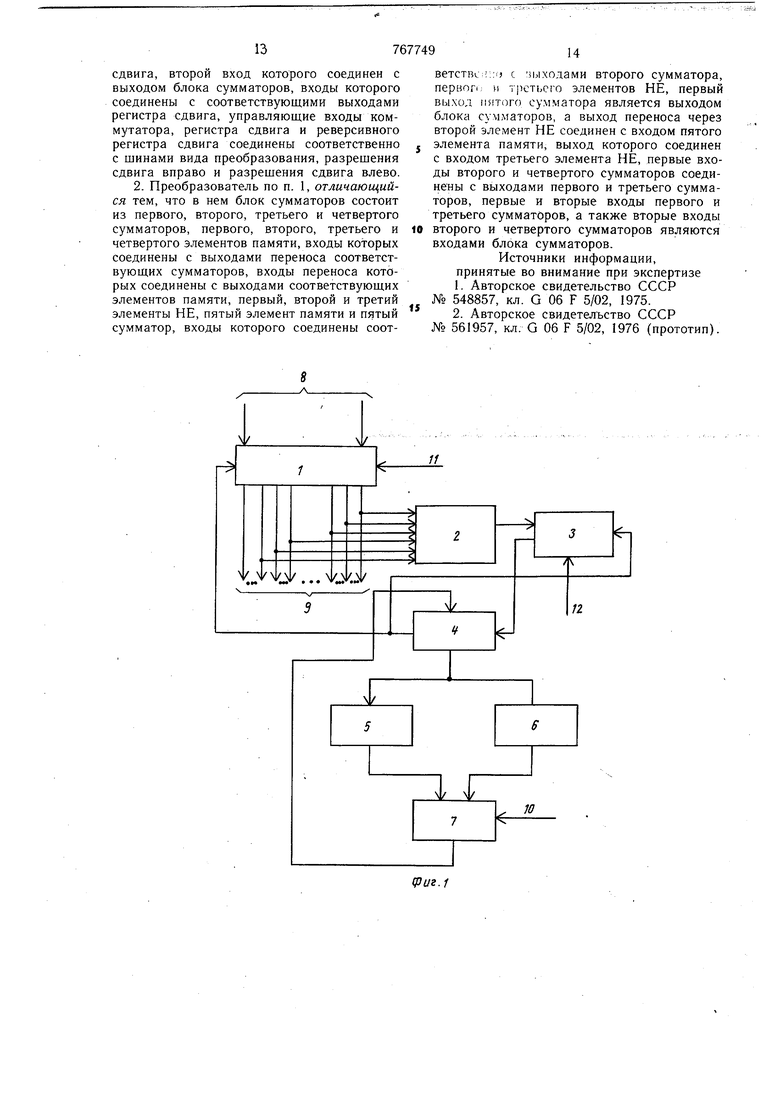

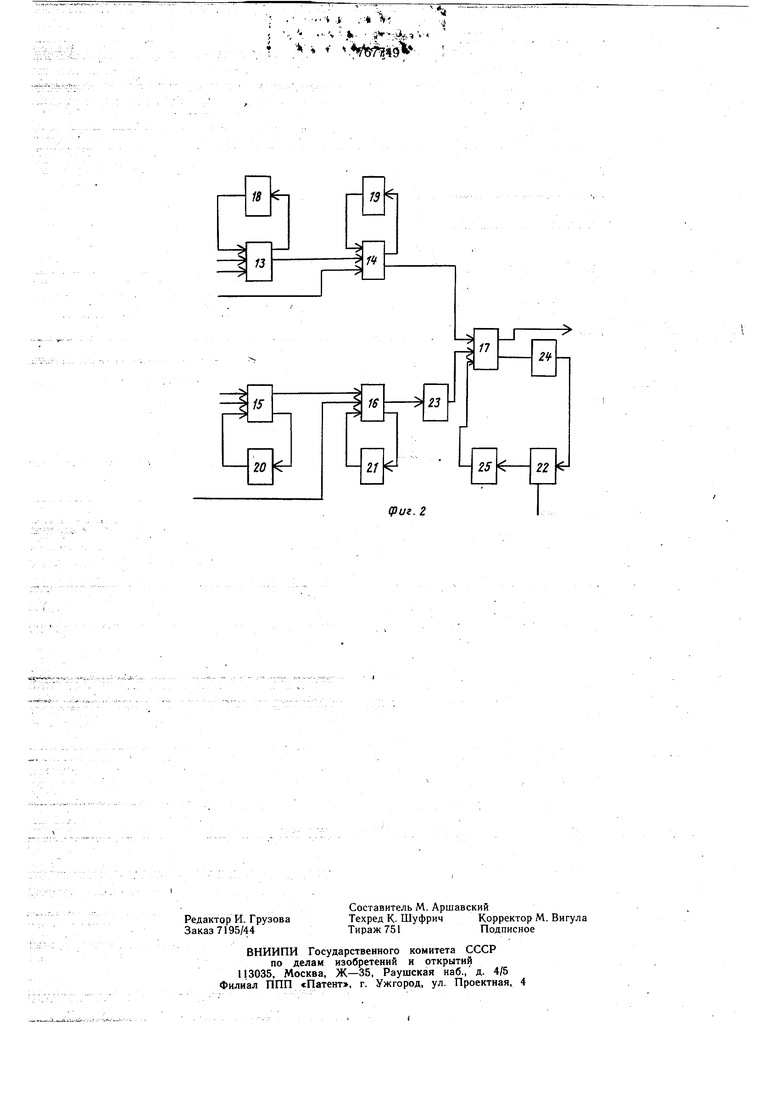

Наиболее близким к изобретению по технической сущности и схемному решению является преобразователь двоичного кода в двоично-десятично-шестидесятиричный код, содержащий регистр сдвига, информационные входы которого и его выходы соединены соответственно с входными и выходными шинами преобразователя, корректируемую тетраду, дешифратор коррекции и блок коррекции 2. Недостаток этого преобразователя заключается в возможности преобразования двоичного кода в двоично-десятично-шестидесятиричный код времени или угла только в том случае, когда вес младшего разряда двоичного кода равен весу младшего разряда выходного кода. Цель изобретения - расширение класса решаемых задач, заключающееся в обеспечении преобразования с масштабированием. Поставленная цель достигается за счет того, что в преобразователь двоичного кода в двоично-десятично-шестидесятиричный код содержащий регистр сдвига, информационные входы которого и его выходы соединены соответственно с входными и выходными шинами преобразователя, корректируемую тетраду, дешифратор коррекции и блок коррекции, введены блок сумматоров, реверсивный регистр сдвига и коммутатор, информационные входы которого соединень с выходами дешифратора коррекции и блока коррекции, а выход коммутатора соединен с информационным входом корректируемой тетрады, вход которой связан с выходом реверсивного регистра сдвига. Информационный выход корректируемой тетрады соединен со входами дешифратора коррекции и блока коррекции, а выход старшего разряда корректируемой тетрады - со входом,регистра сдвига и с первым входом реверсивного регистра сдвига, второй вход которого соединен с выходом блока сумматоров, входами связанного с соответствующими выходами регистра сдвига. Управляющие входы коммутатора, регистра сдвига и реверсивного регистрэ сдвига подключены соответственно к шинам вида преобразования, разрешения сдвига вправо и разрешения сдвига влево. Кроме того, блок сумматоров состоит из первого, второго, третьего и четвертого сумматоров, первого, второго, третьего и четвертого элементов памяти, входы которых соединены с выходами переноса соответствующих сумматоров, входы переноса которых соединены с выходами соответствуюших элементов памяти, первый, второй и третий элементы НЕ, пятый элемент памяти и пятый сумматор, входы которого связаны соответственно с выходами второго сумматора, первого и третьего элементов НЕ. Первый выход пятого сумматора является выходом блока сумматоров, а выход переноса через второй элемент НЕ соединен с входом пятого элемента памяти, выход которого подключен к входу третьего элемента НЕ. Первые входы второго и четвертого сумматоров соединены с выходами первого и третьего сумматоров, первые и вторые входы первого и третьего сумматоров, а также вторые входы второго и четвертого сумматоров являются входами блока сумматоров. Блок-схема предлагаемого преобразователя приведена на фиг. 1; блок-схема одного ИЗ вариантов построения блока сумматоров - на фиг. 2. Преобразователь кодов содержит регистр 1 сдвига, блок 2 сумматоров, реверсивный регистр 3 сдвига, корректируемую тетраду 4, дешифратор 5 коррекции, блок 6 коррекции, коммутатор 7, входные шины 8, выходные шины 9, шины 10 вида преобразования, шину 11 разрешения сдвига вправо, шину 12 разрешения сдвига влево. Блок сумматоров содержит (см. фиг. 2) сумматоры 13-17, элементы 18-22 памяти (например, триггеры), элемер}ты НЕ 23--25. Соответствующие выходы регистра 1 сдвига подключены к первым входам сумматоров 14, 16 и к входам сумматоров 13, 15 выходы суммы которых соединены со вторыми входами сумматоров 14, 16 соответственно, причем между выходами PJ входами переноса сумматоров 13-16 включены элементы 18-21 памяти соответственно, а выход, переноса сумматора 17, связанного входами с выходом суммы сумматора 14 и через элемент . НЕ 23 с выходом сумматора 16, подключен к входу элемента НЕ 24, соединенного через элемент 22 памяти и элемент НЕ 25 с входом переноса сумматора 17, выход которого связан с входом реверсивного регистра 3 сдвига. Предлагаемый преобразователь работает следующим образом. Сначала производится установка в исходное состояние, затем входной двоичный код по шине 8 поступает в регистр 1 сдвига. Для выполнения преобразования методом сдвига и коррекции записанный в регистр 1 сдвига двоичный код умножается на угловой вес единицы младшего разряда, который определяется по формуле If 360°0000 АУ«: где /С - угловой вес единицы младшего разряда входного двоичного кода; п-- количество разрядов во входном двоичном коде. Например, если входной двоичный код имеет двадцать разрядов, т. е. tt 20, то угловой вес единицы его младшего разряда равен К 1,2359619140625. Тогда двоичный код количества секунд измеренного угла определяется следующим образом:Л /С-В, где А - двоичный код количества секунд измеренного угла; В - входной двоичный код. Угловой вес единицы младшего разряда представляется в следующем виде: /С 1 + 0,2359619140625 1 + 0,01403808509375 1 + -1 - (0,015625-0,0015869140625) -0,0015869140625) - 1 +-f - |t+ + (0,001953125 - 0,0003662109375) Г+ + -|г-- + -0,0003662109375 1 + --|4+ gj- (0,000244140625 + + 0,0001220703125) 1 + Тогда двоичный код количества секунд измеряемого угла определяется по формуле Л (1 + + ) В Е( Умножение .двоичного кода числа на коэффициент j-ft эквивалентно сдвигу кода числа на 1г ра зрядов вправо, т. е. в сторону младших разрядов, поэтому умножение для получения значения величины А заменяется алгебраическим суммированием входного кода с кодами, сдвинутыми на -я. разрядов. f Пусть, например, число В 10000001111000111000 в двоичном коде, что соответствует углу 182°39 21 657561. В результате алгебраического суммирования двоичного кода числа В со сдвинутыми на 2, 6, 9, 12. 13 разрядов вправо кодами этого же числа получается число А. .10000001111000111000 100000011110001110 10000001111 10100010100111010101 10000001111000 ч-10000001 1000000 10000100111001 10100010100111010101 10000100111001 10100000100010011100 Получившееся количество секунд А 657564 на 3 больше истинного значения. Причиной ошибки является отбрасывание при суммировании младших разрядов сдвинутых двоичных кодов. Для уменьшения ошибки отбрасывания, которая при наихудшем сочетании нулей и единиц во входном двоичном коде не превышает 3 , необходимо производить суммирование с учетом старших отбрасываемых разрядов. Например, при суммировании с двумя старшими отбрасываемыми разрядами величина ошибки не превышает 1 . i , 4 10000001111000 100000 + 10000001111000 И ГЮп 100000011 10:: 1010001010011101010100 1000000111100011 1000000111 100000011 1000010011101101 1010001010011101010100 1000010011101111 1010000010001001100111 После записи входного двоичного кода в регистре 1 сдвига управляюшим сигналом, поступающим по шине 11, разрешается сдвиг содержимого регистра вправо, а на выходе блока 2 сумматоров, входы которого связаны с выходами нулевого, второго, шестого, девятого, двенадцатого и тринадцатого разрядов регистра сдвига, формируется младший разряд суммы. Коды положительных и отрицательных чисел суммируются отдельно на сумматорах 13, 14 и 15, 16 соответственно. Получившиеся в результате сложения переносы запоминаются на элементах 18-21 памяти. Операция вычитания заменяется сложением уменьшаемого с дополнительным кодом вычитаемого. Дополнительный код двоичного числа равен обратному коду, увеличенному на единицу. На входы сумматора 17 поступает прямой код уменьшаемого с выхода сумматора 14 и обратный код вычитаемого с вь1хода элемента НЕ 23, на вход которого он подается с выхода сумматора 16. Добавление единицы к обратному коду вычитаемого осуществляется подачей единичного потенциала на вход переноса сумматора 17 с выхода элемента НЕ 25, инвертирующего выходной сигнал элемента 22 памяти, перенос на вход которого поступает с выхода сумматора 17 через элемент НЕ 24. Через время, необходимое для формирования младшего разряда алгебраической суммы, производится сдвиг содержимого регистра 1 сдвига и реверсивного регистра 3 сдвига на 1 разряд вправо. При этом младший разряд суммы переписывается в реверсивный регистр 3 сдвига, а в блоке 2 сумматоров производится формирование следующего разряда суммы сложением 1, 3, 7, 10, 13, 14 разрядов входного кода. При сложении учитываются сигналы переноса, поступаюшие с выходов элеменов 18-21 памяти на входы переноса сумматоров 13-16. Элемент 22 памяти подключен через элементы НЕ 24, 25 к суммаору 17, на вход переноса которого поступает важды проинвертированный сигнал переноа от предыдущего суммирования. При сдвиге содержимого регистров 1 и 3 торой разряд суммы записывается в реверсивный регистр 3 сдвига, а на выходе блока 2 сумматоров формируется следующий разряд. Процесс суммирования заканчивается за п+ттактов, где tt- количество разрядов входного двоичного кода, ttt- количество дополнительных разрядов регистра 1 сдвига, необходимых для уменьшения ошибки, возникающей при отбрасывании младших разрядов сдвинутых кодов.

После окончания суммирования сигналом, поступаюшим по шине. 12, разрешается сдвиг содержимого реверсивного регистра 3 сдвига влево, т. е. информация из него выводится старшими разрядами вперед в корректируемую тетраду 4 для осуществления преобразования двоичного кода количества секунд в двоично-десятично-щестидесятиричный код градусов, минут и секунд методом сдвига и коррекции.

Метод сдвига и коррекции для преоб Уазбвания двоичного кода в двоично-десятичный заключается в том, что исходное двоичное число последовательно умножается на 2 (путем сдвига на 1 разряд в сторону старших разрядов), т. е. выводится из реверсивного регистра 3 сдвига в корректируемую тетраду 4 старшими разрядами вперед. Содержимое корректируемой тетрады 4 после каждого сдвига сравнивается с определенными числами в дешифраторе 5 коррекции и блока 6 коррекции, которые формируют скорректированные коды, записываемые вновь в корректируемую тетраду 4 через коммутатор 7, если содержимое тетрады превышает некоторое фиксированное число. Для получения двоично-десятичного кода десятков минут и секунд в блоке 6 коррекции производится сравнение записанного в корректируемой тетраде кода с числом два. Если содержимое тетрады больще этого числа, то производится коррекция путем добавления числа 5 к корректируемому коду. В дешифраторе 5 коррекции содержимое корректируемой тетрады 4 сравнивается с числом 4 и в случае превыщения осуществляется коррекция путем добавления числа :3 к корректируемому коду, т. е. происходит преобразование двоичного кода в двоично-десятичный.

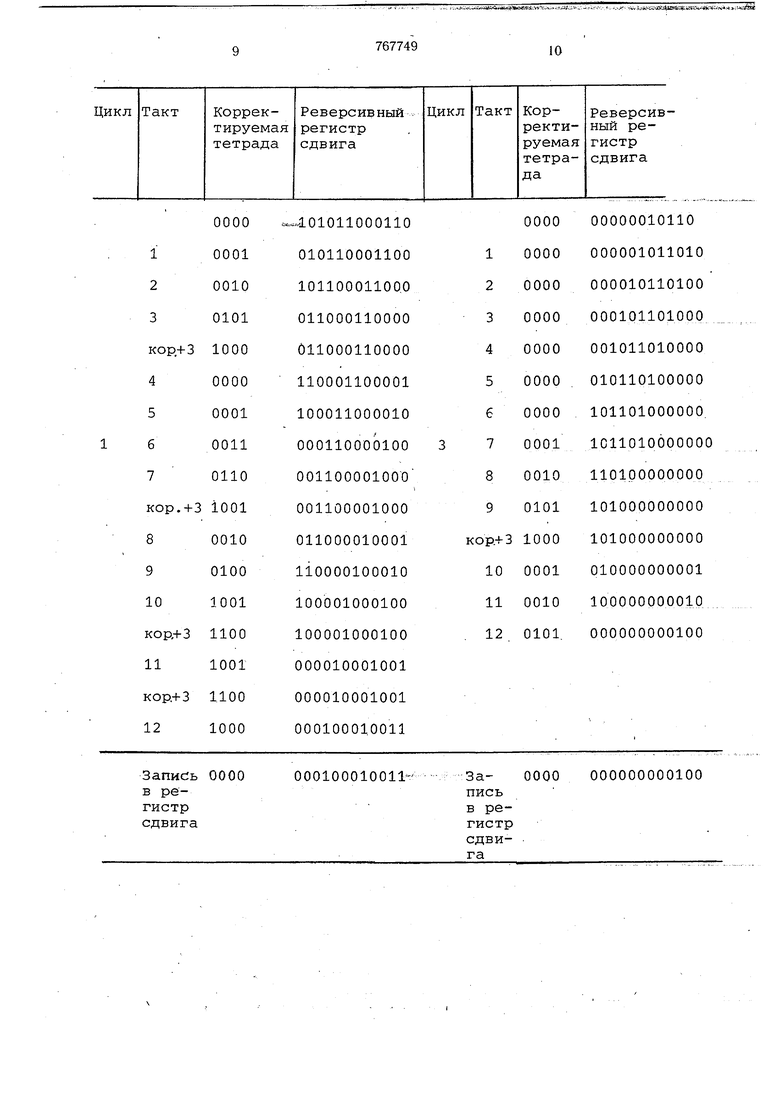

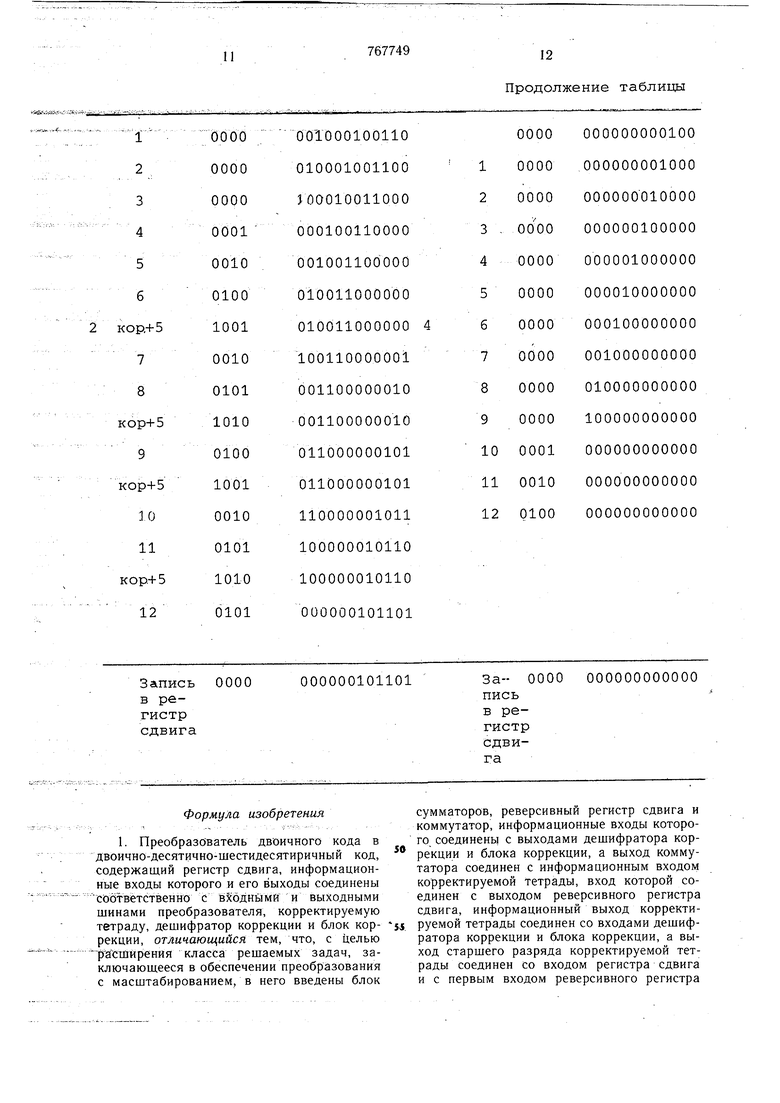

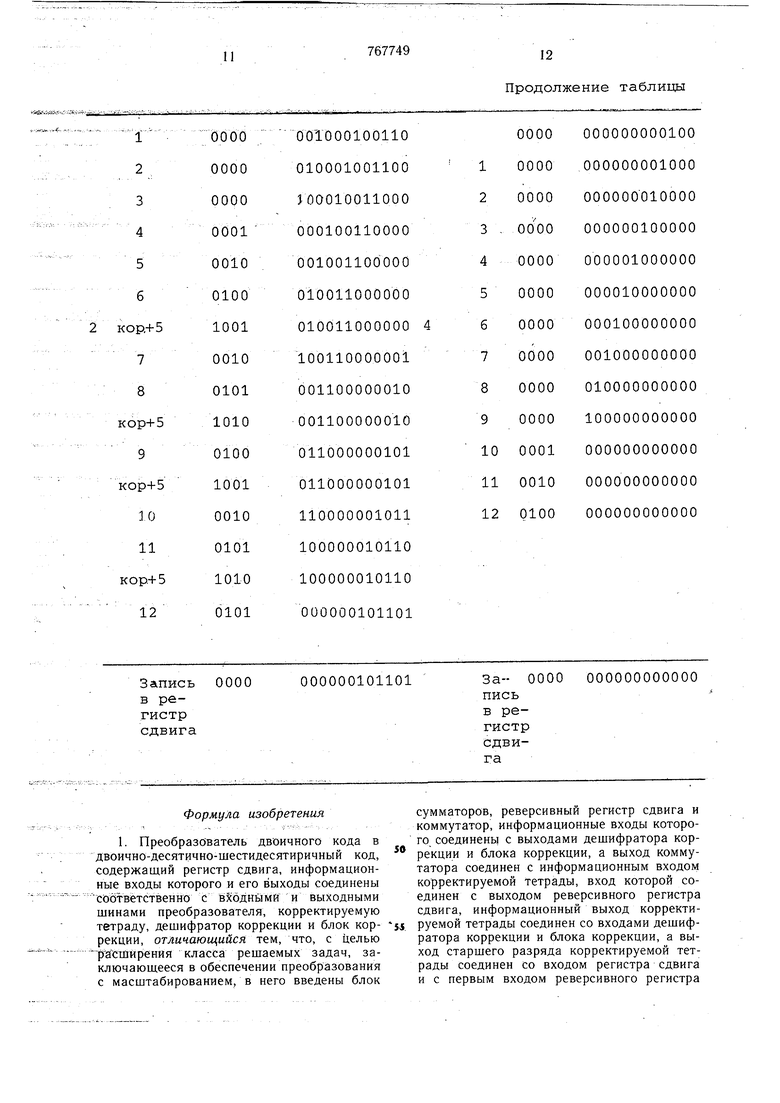

В таблице приведен пример преобразования двоичного кода, количества секунд 101011000110, которому соответствует угол 4558 в двоично-десятично-щестидесятиричном коде.

В течение первых трех тактов производится сдвиг из реверсивного регистра 3 сдвига в корректируемую тетраду 4, при этом в освобождающиеся при сдвиге разрядыпереписывается содержимое корректируемой

тетрады 4. После третьего такта осуществляется коррекция и содержимое корректируемой тетрады 4 увеличивается на 3. В первом цикле преобразования получается двс ично-десятичный код единиц секунд,

поэтому под действием управляющего сигнала, поступающего по щине 10, коммутатор 7 пропускает информацию только с выхода дешифратора 5 коррекции.

После двенадцатого такта, когда из реверсивного регистра 3 сдвига переписался

последний разряд двоичного кода количества секунд, управляющими сигналами, поступающими по шинам 10, 12, закрывается коммутатор 7 и запрещается сдвиг в реверсивном регистре 3, а содержимое тетрады 4 последовательным кодом переписывается в регистр 1.

После этого начинается следующий цикл преобразования; в котором формируется двоично-десятичный код десятков секунд.

Этот цикл также состоит из 12 тактов, только коммутатор 7 открыт для информации, поступающей с выхода блока 6 коррекции. Преобразование заканчивается за 4 цикла, в регистре 1 сдвига сформировалось число 0100 0101 0101 1000, соответствующее углу

4558, записанное в двоично-десятичном коде.

Число циклов преобразования определяется разрядностью входного двоичного кода. Для двадцатиразрядного двоичного

входного кода требуется, например, 7 циклов. Преобразование двоичного кода в двоичНо-десятичный в предлагаемом устройстве осуществляется поступающим по шине 10 управляющим сигналом, который открывает коммутатор 7 только для сигналов с выхода

дешифратора 5 коррекции, при этом последовательный двоичный код Может поступать на вход корректируемой тетрады 4, а параллельный - записываться в реверсивный регистр 3 сдвига.

Преобразование -двоичного кода коли- . чества секунд времени выполняется аналогично преобразованию двоичных кодов количества секунд угла,

Предлагаемый преобразователь кодов позволяет осуществить преобразование двоичного кода в двоично-десятичный и двоичного кода времени или угла в двричнодесятично-шестидесятиричный код, но по сравнению с преобразователем 2 его функции расширены за счет возможности преобразования двоичного кода угла или времени в тех случаях, когда «вес единицы младщего разряда входного двоичного кода не равен «весу единицы младшего разряда двоично-десятично-шестидесятиричного кода.

Продолжение таблицы

Формула изобретения

сумматоров, реверсивный регистр сдвига и коммутатор, информационные входы которого соединены с выходами дещифратора коррекции и блока коррекции, а выход коммутатора соединен с информационным входом корректируемой тетрады, вход которой соединен с выходом реверсивного регистра сдвига, информационный выход корректируемой тетрады соединен со входами дешифратора коррекции и блока коррекции, а выход старшего разряда корректируемой тетрады соединен со входом регистра сдвига и с первым входом реверсивного регистра

сдвига, второй вход которого соединен с выходом блока сумматоров, входы которого соединены с соответствующими выходами регистра сдвига, управляющие входы коммутатора, регистра сдвига и реверсивного регистра сдвига соединены соответственно с шинами вида преобразования, разрешения сдвига вправо и разрешения сдвига влево. 2. Преобразователь по п. 1, отличающийся тем, что в нем блок сумматоров состоит из первого, второго, третьего и четвертого сумматоров, первого, второго, третьего и четвертого элементов памяти, входы которых соединены с выходами переноса соответствующих сумматоров, входы переноса которых соединены с выходами соответствующих элементов памяти, первый, второй и третий элементы НЕ, пятый элемент памяти и пятый сумматор, входы которого соединены соответствс: ::) с выходами второго сумматора, первого и третьего элементов НЕ, первый выход питого сумматора является выходом блока сумматоров, а выход переноса через второй элемент НЕ соединен с входом пятого

элемента памяти, выход которого соединен с входом третьего элемента НЕ, первые входы второго и четвертого сумматоров соединены с выходами первого и третьего сумматоров, первые и вторые входы первого и третьего сумматоров, а также вторые входы

второго и четвертого сумматоров являются входами блока сумматоров.

Источники информации, принятые во внимание при экспертизе

№ 561957, кл. G 06 F 5/02, 1976 (прототип).

,-.V. ,:.. .;

, ,. Ч . jv--yji.,,4 ,

Авторы

Даты

1980-09-30—Публикация

1978-12-04—Подача