(54) УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ МНОГОРАЗРЯДНЫХ

ЧИСЕЛ

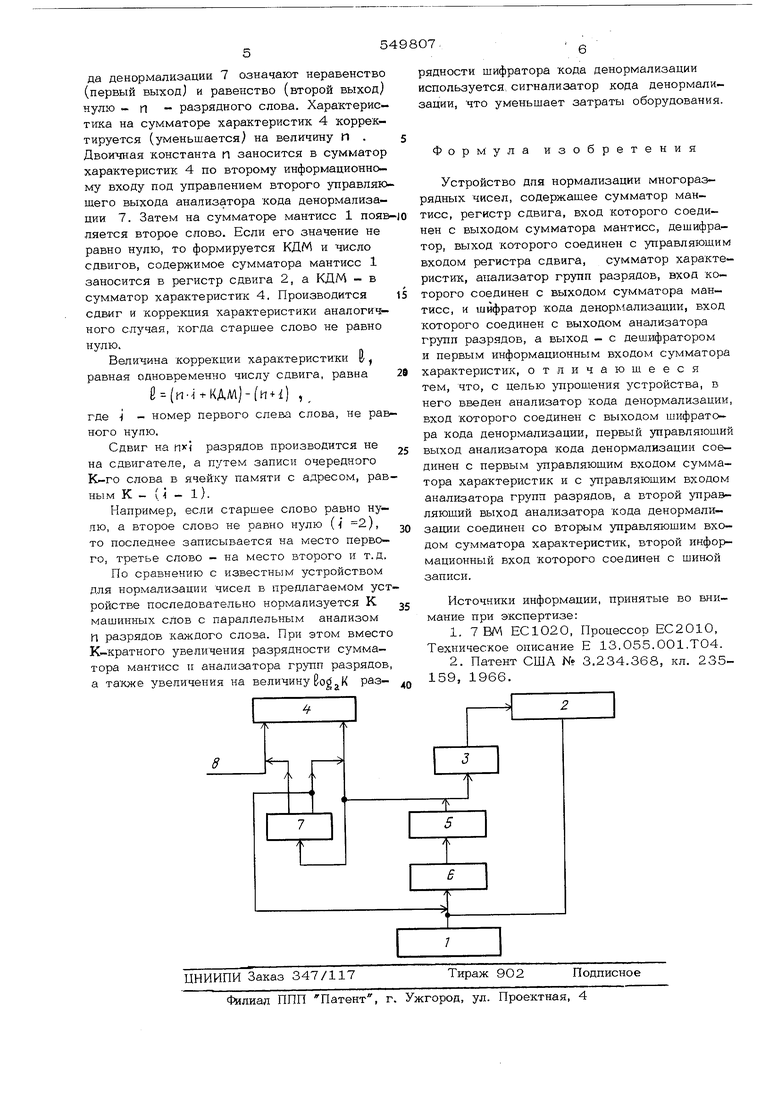

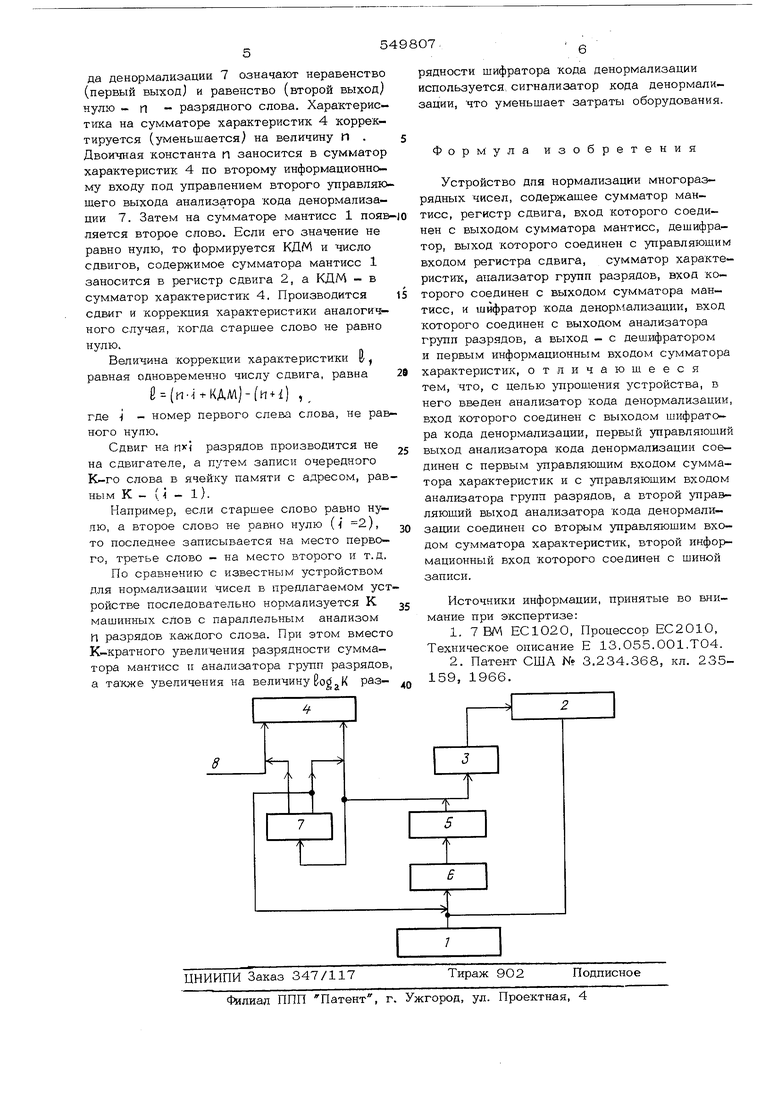

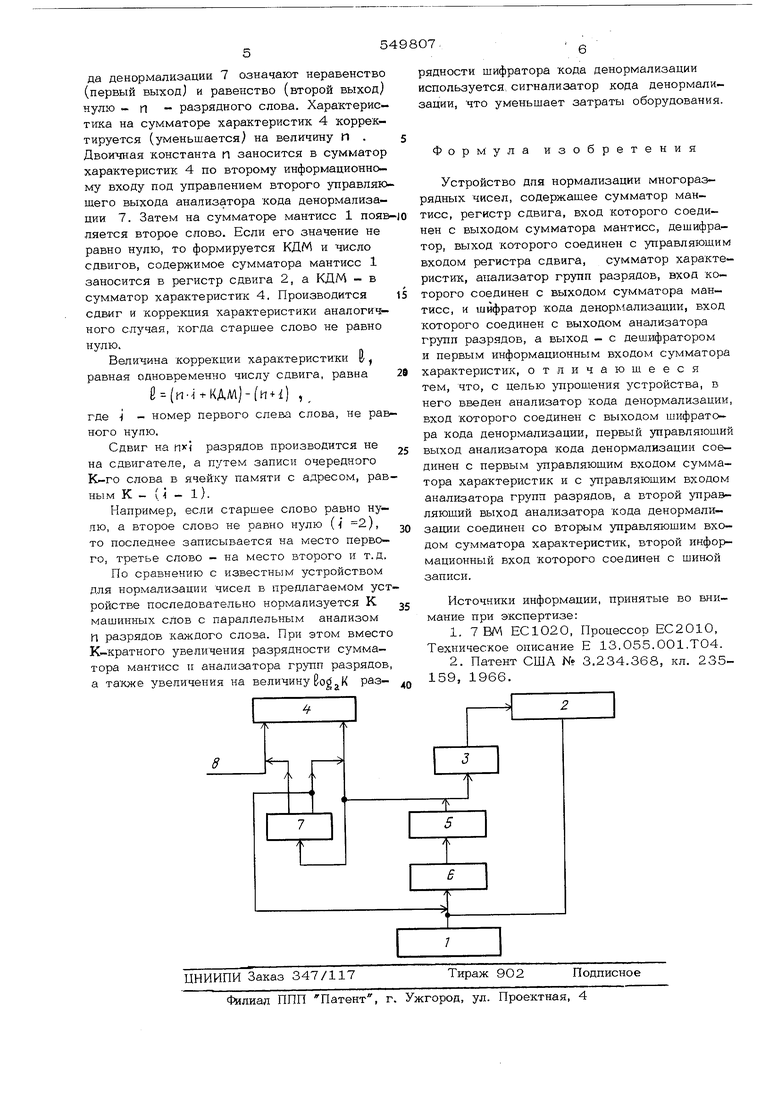

шифратора 3, сумматора характеристик 4, шифратора кода денормализации 5, анализатора групп разрядов б и анализатора кода денормализации 7, шины записи 8.

Выход сумматора мантисс 1 соединен с информационным входом регистра сдвига 2, управляющий вход которого соединен с выходом дешифратора 3. Первый информационный вход сумматора характеристик 4 соединен с выходом шифратора 5. Вход шифратора 5 соединен с выходом анализатора груп разрядов 6. Выход шифратора 5 соединен со входом дешифратора 3 и входом анализатора кода денормализации 7.

Первый управляющий выход анализатора кода денормализации 7 соединен с первым управляющим входом сумматора характеристик 4 и с управляющим входом анализатора групп разрядов 6. Второй управляющей выхо анализатора кода денормализации 7 соединен со вторым управляющим входом сумматора мантисс 4. Второй информационный вход сумматора мантисс 4 соединен с шиной записи 8.

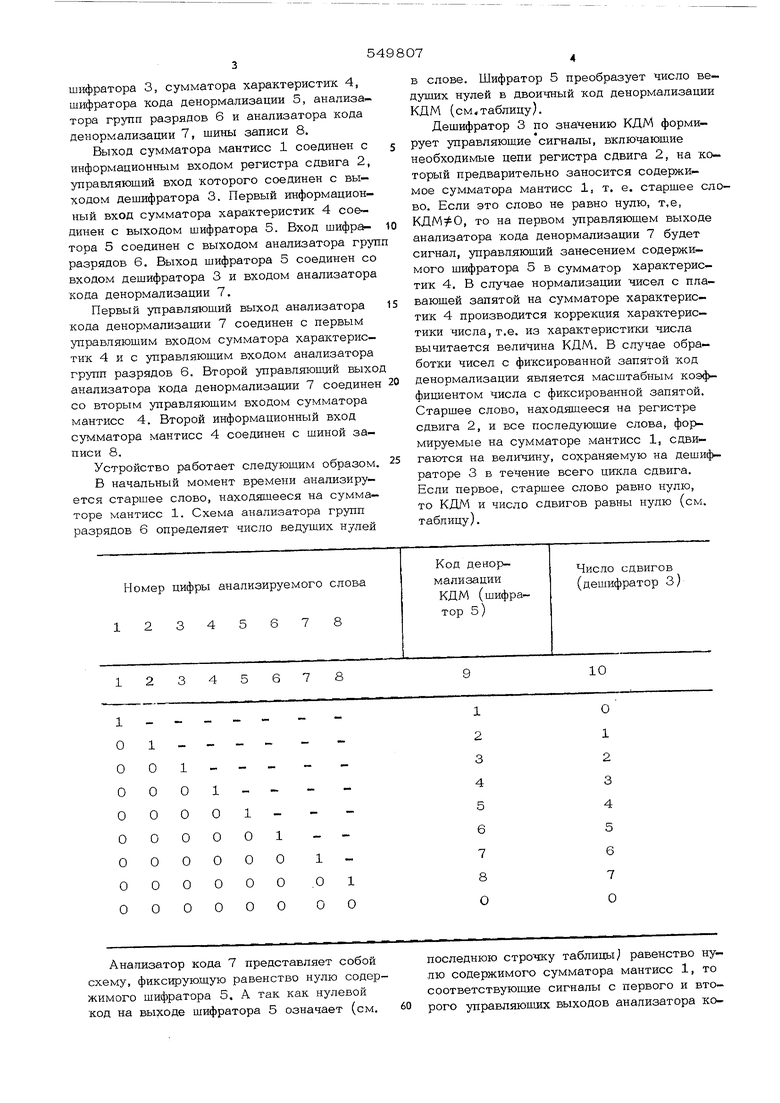

Устройство работает следующим образом. В начальный момент времени анализируется старшее слово, находящееся на сумматоре мантисс 1. Схема анализатора групп разрядов 6 определяет число ведущих нулей

в слове. Шифратор 5 преобразует число ведуших нулей в двоичный код денормализации КДМ (см.таблицу).

Дешифратор 3 по значению КДМ формирует управляющие сигналы, включающие необходимые цепи регистра сдвига 2, на который предварительно заносится содержимое сумматора мантисс 1, т. е, старщее слво. Если это слово не равно нулю, т,е, , то на первом управляющем выходе анализатора кода денормализации 7 будет сигнал, управляющий занесением содержимого щифратора 5 в сумматор характеристик 4. В случае нормализации чисел с плавающей запятой на сумматоре характеристик 4 производится коррекция характеристики числа, т.е. из характеристики числа вычитается величина КДМ. В случае обработки чисел с фиксированной запятой код денормализации является масштабным коэффициентом числа с фиксированной запятой. Старщее слово, находящееся на регистре сдвига 2, и все последующие слова, фор мируемые на сумматоре мантисс 1, сдвигаются на величину, сохраняемую на дешифраторе 3 в течение всего цикла сдвига. Если первое, старшее слово равно нулю, то К.ДД и число сдвигов равны нулю (см. таблицу).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нормализации чисел | 1980 |

|

SU953636A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Преобразователь форматов данных | 1985 |

|

SU1418909A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

Анализатор кода 7 представляет собой схему, фиксирующую равенство нулю содержимого шифратора 5. А так как нулевой код на выходе шифратора 5 означает (см.

последнюю строчку таблицы) равенство нулю содержимого сумматора мантисс 1, то соответствующие сигналы с первого и второго управляющих выходов анализатора кода денормализации 7 означают неравенство (первый выход) и равенство (второй выход) нулю - п - разрядного слова. Характеристи-ка на сумматоре характеристик 4 корректируется (уменьшается) на величину П . Двоичная константа п заносится в сумматор характеристик 4 по второму информационному входу под управпением второго управляю щего выхода анализатора кода денормализа- ции 7. Затем на сумматоре мантисс 1 появ ляется второе слово. Если его значение не равно нулю, то формируется КДМ и число сдвигов, содержимое сумматора мантисс 1 заносится в регистр сдвига 2, а КДМ - в сумматор характеристик 4. Производится сдвиг и коррекция характеристики аналогичного случая, когда старшее слово не равно нулю. Величина коррекции характеристики §, равная одновременно числу сдвига, равна 6 ()-(мЧ) , где - номер первого слева слова, не рав ного нулю. Сдвиг на разрядов производится не на сдвигателе, а путем записи очередного К-го слова в ячейку памяти с адресом, рав ны мК- () - 1). Например, если старшее слово равно нулю, а второе слово не равно нулю ( 2), то последнее записывается на место первого, третье слово - на место второго и т.д. По сравнению с известным устройством для нормализации чисел в предлагаемом уст ройстве последовательно нормализуется К машинных слов с параллельным анализом П разрядов каждого слова. При этом вместо К-кратного увеличения разрядности сумматора мантисс и анализатора групп разрядов, а также увеличения на величину Во.К раз- рядности шифратора кода денормализации используется сигнализатор кода денормализации, что уменьшает затраты оборудования. Формула изобретения Устройство для нормализации многоразрядных чисел, содержащее сумматор мантисс, регистр сдвига, вход которого соединен с выходом сумматора мантисс, дешифратор, выход которого соединен с управляющим входом регистра сдвига, сумматор характеристик, анализатор групп разрядов, вход которого соединен с выходом сумматора мантисс, и шифратор кода денормализации, вход которого соединен с выходом анализатора групп разрядов, а выход - с дешифратором и первым информационным входом сумматора характеристик, отличающееся тем, что, с целью т1рощения устройства, в него введен анализатор кода денормализации, вход которого соединен с выходом шифратора кода денормализации, первый управляющий выход анализатора кода денормализации соединен с первым управляющим входом сумматора характеристик и с управляющим входом анализатора групп разрядов, а второй управляющий выход анализатора кода денормализации соединен со вторым управляющим входом сумматора характеристик, второй информационный вход которого соединен с шиной записи. Источники информации, принятые во внимание при экспертизе: 1.7 ВМ ЕС1020, Процессор ЕС2010, Техническое описание Е 13.055.О01.Т04. 2.Патент США N 3,234.368, кл. 235159, 1966.

Авторы

Даты

1977-03-05—Публикация

1975-02-28—Подача