(21)3977743/24-24

(22)19.11.85

(46; 23.08.«8. иол. № 31

(71)Институт кибернетики i им. В.М.Глушкова

(72)В.П.Боюн, Б.Н.Малиновский, В.Е.Реуцкий и М.Е.Урсу

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 717755, кл. Н 03 М 7/12, 1977.

Авторское свидетельство СССР 1092490, кл. Н 03 М 7/12, 1982.

(54)ПРЕОБРАЗОВАТЕЛЬ ФОРМАТОВ ДАННЫХ

(57)Изобретение относится к цифровой вычислительной технике и может

чисм Характеристика V

быть использовано при построении ycTi ройств согласования ЭВМ с различными форматами данных. Целью изобретения является расширение класса решаемых задач за счет обеспечения возможности преобразования в формат данных с шестнадцатиричным основанием, Для этого в преобразователь форматов данных, содержащий счетчик порядка 1, блок сдвига 2, триггер знака 3, коммутатор мантиссы 8 и блок управления 9, дополнительно введены дешифратор нулевой характеристики 4, элемент ИЛИ-НЕ 5, элементы ИЛИ 6, 7, 2 ил, 2 табл.

Мантисса

с &

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь форматов данных | 1985 |

|

SU1290535A1 |

| Преобразователь форматов данных | 1982 |

|

SU1092490A1 |

| Преобразователь форматов данных | 1986 |

|

SU1466012A1 |

| Преобразователь форматов данных | 1989 |

|

SU1686701A1 |

| Преобразователь форматов данных | 1986 |

|

SU1476615A1 |

| Преобразователь форматов данных | 1989 |

|

SU1728971A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

оо со о со

1

1

Фил1

1

Изобретение относится к цифровой вьмислительной технике и может быть использовано при построении устройс согласования ЭВМ с различными форматами представления данных.

Цель изобретения - расширение класса решаемых задач за счет обеспчения возможности преобразования в формат данных с шестнадцатиричным основанием.

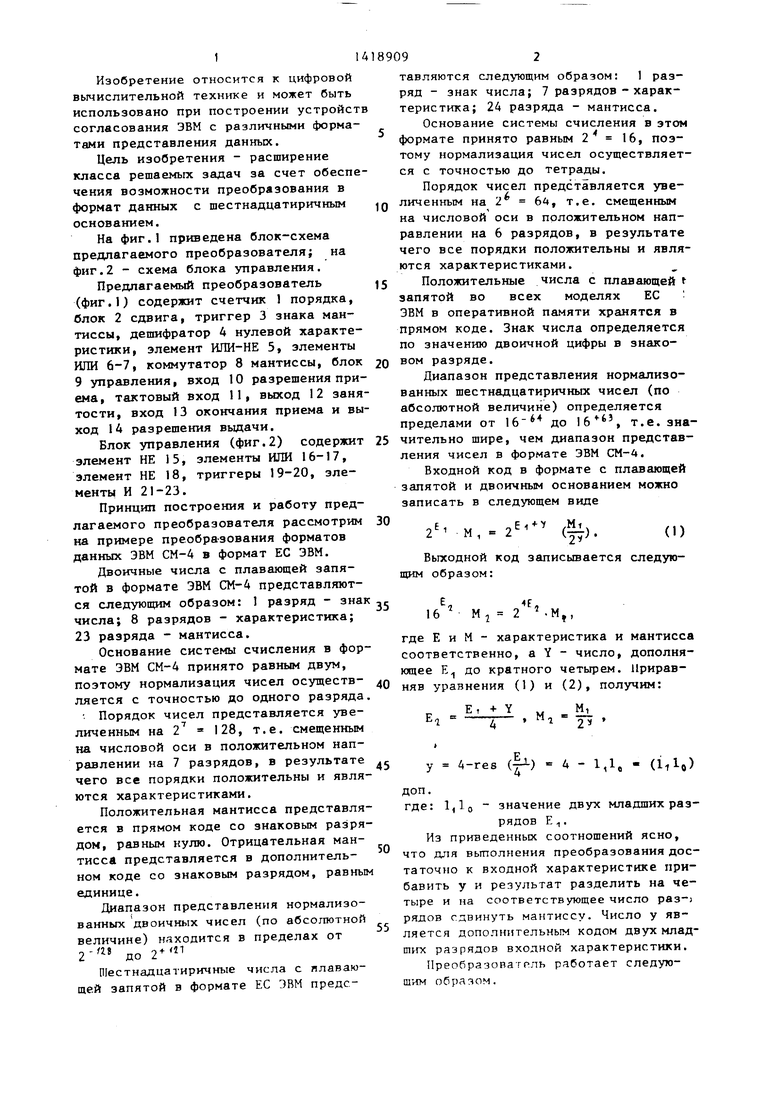

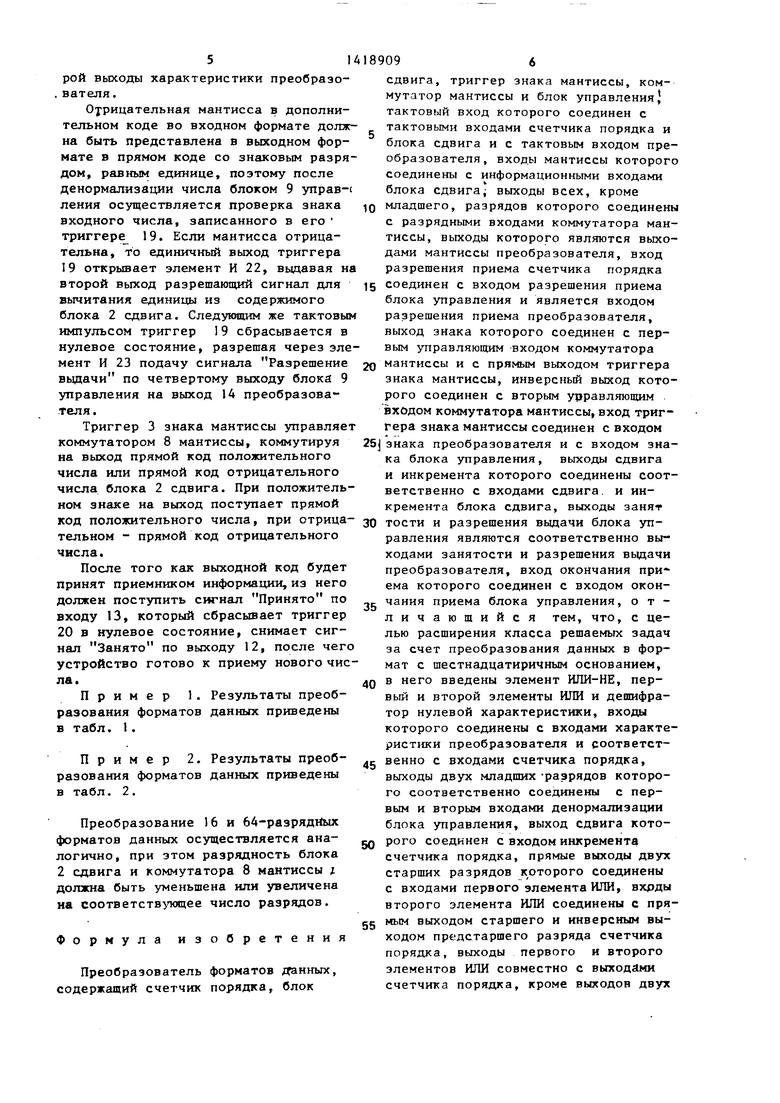

На фиг.1 приведена блок-схема предлагаемого преобразователя; на фиг.2 - схема блока управления. Предлагаемый преобразователь (фиг.1) содержит счетчик 1 порядка, блок 2 сдвига, триггер 3 знака мантиссы, дешифратор 4 нулевой характеристики, элемент ИЛИ-НЕ 5, элементы ИЛИ 6-7, коммутатор 8 мантиссы, бло 9 управления, вход 10 разрешения приема, тактовый вход 11, выход 12 зантости, вход 13 окончания приема и вход 14 разрешения выдачи.

Блок управления (фиг.2) содержи элемент НЕ 15, элементы ИЛИ 16-17, элемент НЕ 18, триггеры 19-20, элементы И 21-23.

Принцип построения и работу предлагаемого преобразователя рассмотрим на примере преобразования форматов данных ЭВМ СМ-4 в формат ЕС ЭВМ.

Двоичные числа с плавающей запятой в формате ЭВМ СМ-4 представляются следующим образом: 1 разряд - зна числа; 8 разрядов - характеристика; 23 разряда - мантисса.

Основание системы счисления в формате ЭВМ СМ-4 принято равным двум, поэтому нормализация чисел осуществляется с точностью до одного разряда Порядок чисел представляется увеличенным на 2 128, т.е. смещенным на числовой оси в положительном нап- равлении на 7 разрядов, в результате чего все порядки положительны и являются характеристиками.

Положительная мантисса представляется в прямом коде со знаковым разрядом, равным нулю. Отрицательная мантисса представляется в дополнительном коде со знаковым разрядом, равнь единице.

Диапазон представления нормализованных двоичных чисел (по абсолютной величине) находится в пределах от

2-/Z8 до

Шестнадцатиричные числа с плавающей запятой в формате ЕС ЭВМ предс

0

5

0

тавляются следующим образом: 1 разряд - знак числа; 7 разрядов - характеристика; 24 разряда - мантисса.

Основание системы счисления в этом формате принято равным 2 16, поэтому нормализация чисел осуществляется с точностью до тетрады.

Порядок чисел представляется увеличенным на 2 б4, т.е. смещенным на числовой оси в положительном направлении на 6 разрядов, в результате чего все порядки положительны и являются характеристиками.

Положительные числа с плавающей запятой во всех моделях ЕС ЭВМ в оперативной памяти хранятся в прямом коде. Знак числа определяется по значению двоичной цифры в знаковом разряде.

Диапазон представления нормализованных шестнадцатиричных чисел (по абсолютной величине) определяется пределами от 16 до 16, т.е. зна- 5 чительно шире, чем диапазон представления чисел в формате ЭВМ СМ-А.

Входной код в формате с плавающей запятой и двоичным основанием можно записать в следующем виде

2

М,

,

(). 2

(1)

Выходной код записывается следующим образом:

М,

f,

м

t

4 j.gg

где Е и М - характеристика и мантисса соответственно, а Y - число, дополняющее Е до кратного четырем. Приравняв уравнения (1) и (2), получим:

Е, + Y

М,

Mi 24

Ф

4 1,1с (l.le)

4 j.gg

доп.

где:

IJo 0

5

значение двух младших разрядов Е.

Из приведенных соотношений ясно, что для вьтолнения преобразования достаточно к входной характеристике прибавить у и результат разделить на четыре и на соответствующее число раз-) рядов сдвинуть мантиссу. Число у является дополнительным кодом двух млад- шргх разрядов входной характеристики.

Иреобразоватпль работает следующим образом.

3l

При подключении входного кода на входы устройства и подаче сигнала Разрешение приема по входу 10 (фиг.1 осуществляется запись разрядов 1-8 характеристики в разряды 2-9 счетчика 1 порядка, в разряд 1 счетчика 1 порядка при этом записьшается ноль. Нулевой разряд (знак числа) и разряды 9-31 мантиссы записываются соответственно в триггер 3 знака и в 2А-раз- рядный блок 2 сдвига.

Одновременно сигнал с выхода элемента ИЛИ-НЕ 5 устанавливает в соответствующее состояние триггер неявного старшего (восьмого) разряда блока 2 сдвига. Если мантисса положительна и характеристика ненулевая, то триггер неявного старшего (восьмого) разряда устанавлршается в единичное состояние. Если же характеристика равна нулю, а также если мантисса отрицательна, то триггер неявного старшего (восьмого) разряда устанавливается в нулевое состояние.

Сигнал Разрешение приема, поступающий также в блок 9 управления по четвертому входу устанавливает триггер 20 в единичное состояние, который, подготавливает блок 9 управления к работе и выдает по третьему выходу сигнал Занято на выход 12 преобразователя, предупреждая источник входной информации о занятости устройства.

Знак мантиссы по выходу совпадает со знаком входного числа, поэтому однозначно передается с прямого выхода триггера 3 знака мантиссы на выход.

В счетчик 1 порядка добавляются от одной до трех единиц с одновременным сдвигом вправо (уменьшением) мантиссы, которая становится денормали- зованной.

Значения восьмого и девятого разрядов с выхода счетчика 1 порядка по даются соответственно на первый и второй входы блока 9 управления (фиг. 2) .. Ненулевое состояние этих разрядов через элемент ИЛИ 17 и через элемент И 21 дает разрешение на первый выход блока 9 управления для добавления единии в счетчике 1 порядка и сдвигов (без знака) блока 2 сдвига, которые осуществляются под воздействием тактовых импульсов по входу 1) до тех пор, пока восьмой и девятый разряды счетчика 1 порядка не станут равными нулю, количество.воз094

можных добавлений единиц с одновременными сдвигами равно 0-3. При сдвигах мантиссы вправо в случае нулевого состояния триггера 3 знака мантиссы (фиг.1) на вход старшего (восьмого) разряда мантиссы поступают нули, а в случае един1гчного состояния триггера 3 знака мантиссы - единицы.

После того как восьмой и девятый разряды счетчика 1 порядка станут равными нулю, снимается разрешающий сигнал с выхода элемента ИЛИ 17 и соответственно с первого выхода блока 9 травления, и появляется сигнал на выходе элемента НЕ 8, который поступает на входы элементов И 22 и 23, подготавливая блок 9 управления дня дальнейшей работы.

Если восьмой и девятый разряды счетчика 1 порядка сразу оказались равными нулю, тО добавление единиц в счетчик 1 порядка и сдвиги вправо регистра мантиссы не производятся.

Диапазон изменения характеристики входного числа соответствует изменению характеристики выходного числа в пределах: 0100000 - Ullllll для отрицательных и 1000000 - 1011111 для положительных порядков.

Пределы 0000000 - 0011111 для отрицательных и 1100000 - 1111111 для положительных порядков при этом не используются. Поэтому второй разряд характеристики выходного числа всегда является инверсией первого разряда характеристики выходного числа, кроме случая переполнения счетчика 1 порядка, когда характеристика входного числа имеет одно из следующих значений: 1111101, 1111110,1111111. 3 этом случае на выходе преобразователя характеристика имеет значение 1100000.

Таким образом, разряды 3-7 счетчика 1 порядка поступают прямо на выходы 3-7 преобразователя. Сигнал с прямого выхода второго разряда счетчика 1 порядка через элемент КПИ 6 поступает на первый выход преобразо вателя, а сигнал с его инверсного выхода поступает через элемент ИЛИ 7 на второй выход характеристики преобразователя. Выход переполнения счетчика 1 порядка через элементы ИЛИ 6 и 7 выдачи соответственно первого и второго разрядов характеристики подается соответственно на первый и вто51

рой выходы характеристики преобраэо- .вателя.

Оурицательная мантисса в дополнительном коде во входном формате должна быть представлена в выходном формате в прямом коде со знаковым разрядом, равным единице, поэтому после денормализации числа блоком 9 управ-( Ленин осуществляется проверка знака входного числа, записанного в его триггере 19. Если мантисса отрицательна, то единичный выход триггера 19 открывает элемент И 22, вьщавая на второй выход разрешающий сигнал для вычитания единицы из содержимого блока 2 сдвига. Следующим же тактовым импульсом триггер 19 сбрасьгеается в нулевое состояние, разрешая через элемент И 23 подачу сигнала Разрешение вьщачи по четвертому выходу блока 9 управления на выход 14 преобразователя.

Триггер 3 знака мантиссы управляет коммутатором 8 мантиссы, коммутируя на выход прямой код положительного числа или прямой код отрицательного числа блока 2 сдвига. При положительном знаке на выход поступает прямой код положительного числа, при отрицательном - прямой код отрицательного числа.

После того как выходной код будет принят приемником информации, из него должен поступить cie Han Принято по входу 13, который сбрасывает триггер 20 в нулевое состояние, снимает сигнал Занято по выходу 12, после чего устройство готово к приему нового числа.

Пример 1. Результаты преобразования форматов данных приведены в табл. 1.

Пример 2. Результаты преобразования форматов данных приведены в табл. 2.

Преобразование 16 и 64-разряд11ых форматов данных осуществляется аналогично, при этом разрядность блока 2 сдвига и коммутатора 8 мантиссы i должна быть уменьшена или увеличена на соответств тощее число разрядов.

Формула изобретения

Преобразователь форматов данных, содержащий счетчик порядка, блок

096

сдвига, триггер знака мантиссы, коммутатор мантиссы и блок управления) тактовый вход которого соединен с тактовыми входами счетчика порядка и блока сдвига и с тактовым входом преобразователя, входы мантиссы которого соединены с информационными входами блока сдвига,- выходы всех, кроме

младшего, разрядов которого соединены с разрядными входами коммутатора мантиссы, выходы которого являются выходами мантиссы преобразователя, вход разрешения приема счетчика порядка

соединен с входом разрешения приема блока управления и является входом разрешения приема преобразователя, выход знака которого соединен с первым управляющим входом коммутатора

мантиссы и с прямым выходом триггера знака мантиссы, инверсный выход которого соединен с вторым управляющим входом коммутатора мантиссы, вход триггера знака мантиссы соединен с входом

знака преобразователя и с входом знака блока управления, выходы сдвига и инкремента которого соединены соответственно с входами сдвига, и инкремента блока сдвига, выходы занят

тости и разрешения выдачи блока управления являются соответственно выходами занятости и разрешения вьщачи преобразователя, вход окончания при ема которого соединен с входом окончания приема блока управления, отличающийся тем, что, с целью расширения класса решаемых задач за счет преобразования данных в формат с шестнадцатиричным основанием,

в него введены элемент ИЛИ-НЕ, первый и второй элементы ИЛИ и дешифратор нулевой характеристики, входы которого соединены с входами характеристики преобразователя и соответственно с входами счетчика порядка, выходы двух младших -разрядов которого соответственно соединены с первым и вторым входами денормализации блока управления, выход сдвига которого соединен с входом инкремента

счетчика порядка, прямые выходы двух старших разрядов к оторого соединены с входами первого элемента ИЛИ, вхрды второго элемента ИЛИ соединены с прямь1м выходом старшего и инверсным выходом пр дстаршего разряда счетчика порядка, выходы первого и второго элементов ИЛИ совместно с выходами счетчика порядка, кроме выходов двух

714

старпшх и двух младших разрядов, являются выходами характеристики преобразователя, вход знака которого соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом дешифратора нулевой характеристики, а выход элемента ИЛИ-НЕ соединен с информационным входом старшего разПриемна регистрмантиссы и счетчик порядка О

010011101 1101 0000 0000 0000 0000 оиоо

После де- нормали- зации О

010100000 0001 1010 0000 0000 0000 0000

Выходной код О

1001000 0001 1010 0000 0000 0000 0000 13 .,§

128

Исходный

код 1 01100011 011

Прием на регистр мантиссы и счетчик порядка 1

001100011 ООП 0000 0000 0000 0000 0000

После де- нормализа- ции 1

После вычитанияединицы 1

001100000 1001 1000 0000 0000 0000 0000

001100100 1001

01 1 1 1 111 1111 1111 1111

Выходной код 1

0111001 оно

189098

ряда блока сдвига, входы последовательного прямого и обратного кодов которого соединены соответственно с прямым и инверсным выходами триггер а знака, выход иладшего разряда блока сдвига соединен с входом младшего разряда коммутатора мантиссы.

Таблица 2

0000 0000 0000 0000 0000 -13 „-1«

16

01 1 1 1 111 1111 1111 1111

1000 0000 0000 0000 0000 -13 .,-7

32 ЩВмдТМ

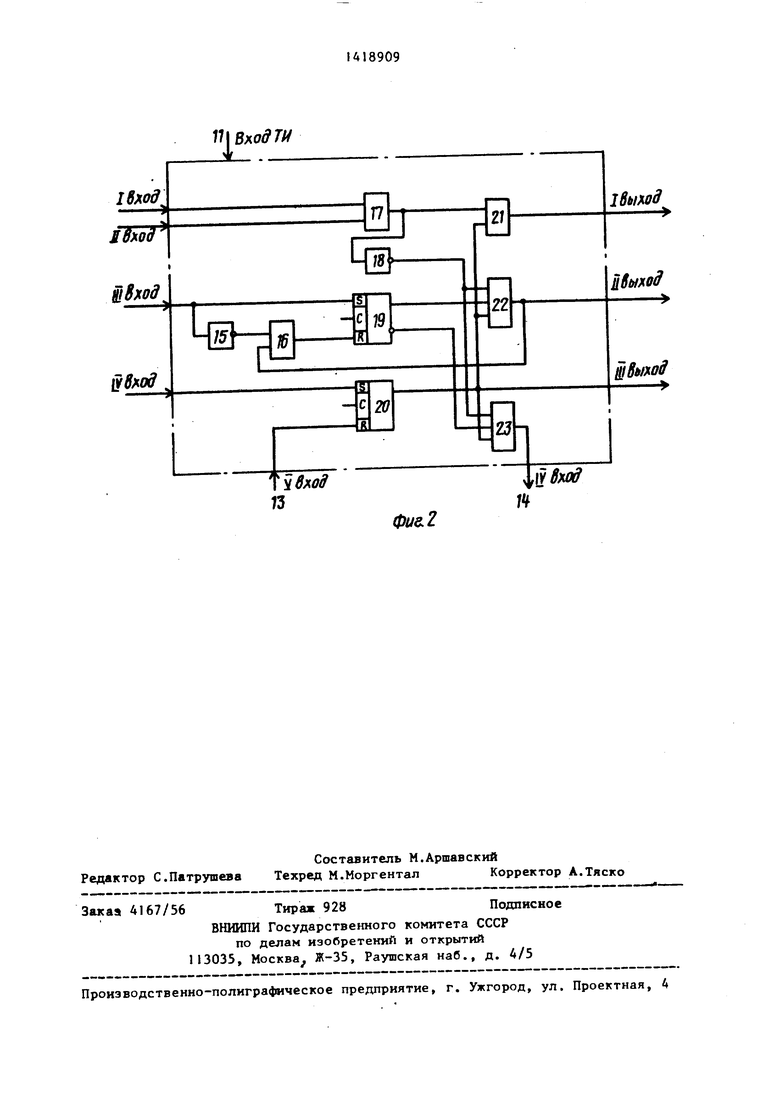

Фиг. 2

Авторы

Даты

1988-08-23—Публикация

1985-11-19—Подача