1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах автоматизироваиного управления объектами.

Известен цифровой экстраполирующий иреобразователь, содержащий нервый регистр памяти, входы которого соединены с щинами входного кода, а выходы - с соответствующими входа ми преобразователя «код - частота ;; .второй регистр памяти, реверсивный счетчик, элементы И, блок прогноза и линейный интериолятор 1.

Недостаток такого преобразователя - больИ1ие затраты оборудования на блок прогноза и линейный интерполятор.

Иаиболее близким техническим рещением к данному изобретению является цифровой экстраполятор, содержащий первый регистр, входы которого соединены с установочными входами реверсивного счетчика и с кодовым входом преобразователя, а выходы - со входом первого преобразователя «код - частота и через последовательно соединенные первый элемент И, второй регистр, подключенный ко второму преобразователю «код - частота, второй элемент И третий регистр - со входами третьего иреобразователя «код - частота, причем управляющие входы первого и второго элементов PI подключены к тактовому входу преобразователя 2.

Недостатком этого экстраполятора является ограниченная точность воснроизведения кривых выше первого порядка, перерегулирование при скачках входного сигнала, т. е. низкая точность преобразователя.

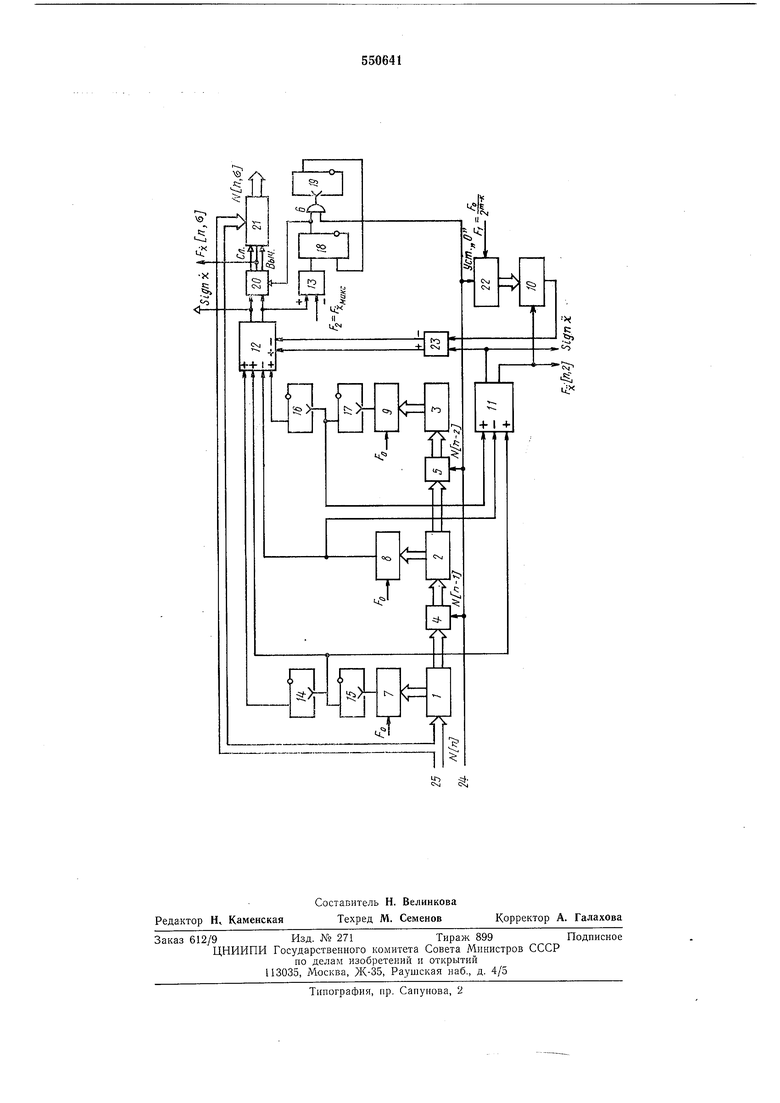

С целью повышения точности в нредлагаемый нреобразователь введены четыре триггера, первый вычислительный блок, блок синхронизации и последовательио соединеиные суммирующий счетчик, четвертый преобразователь «код - частота, блок коммутации, второй вычислительиый блок, входы которого подключены к выходу второго преобразователь «код - частота и единичным выходам первого, второго и третьего триггеров, а выходы через блок синхронизации - ко входам реверсивного счетчика, третий вычислительный блок, пятый триггер, третий элемент И, управляющий вход которого подключеи к тактовому входу нреобразователя и входу установки в нуль суммирующего счетчика, и шестой триггер, единичный выход которого нодключен к нулевому входу пятого триггера, счетные входы второго и четвертого триггеров нодсоединены к выходам соответственно первого н третьего преобразователей «код - частота, единичные выходы этих триггеров, подключенные к счетным входам иервого и третьего триггеров соответствеиио, и выход второго иреобразователя «код - частота соединены через первый вычислительный блок со входами блока коммутации и четвертого преобразователя «код - частота, причем единичный выход пятого триггера подключен к запрещающему входу блока синхронизации. На чертеже показана схема предлагаемого преобразователя. Он содержит регистры -3, элементы И , преобразователи «код - частота 7-10, вычислительные блоки И -13, триггеры 14- 19, блок синхронизации 20, реверсивный счетчик 21, суммирующий счетчик 22, блок коммутации 23, тактовый 24 и кодовый 25 входы преобразователя. Цифровой экстраполирующий преобразователь работает следующим образом. По тактовому импульсу, совпадающему во времени с моментами поступления нового значения кода, открываются элементы И 4 и 5 и происходит перепись содержимого регистра 1 в регистр 3, регистра 2 - в регистр 3, новое значение кода записывается в регистр 1. Таким образом в регистрах 1, 2 и 3 хранятся значения Л„, N-i и Nn-z соответственно. Преобразователи 7, 8 и 9 преобразуют эти коды в частотно-импульсные сигналы. Триггеры 14, 15, 16, 17 предназначены для обеспечения необходимых весовых коэффициентов. Частоты с выхода триггера 15, преобразователя «код - частота 8 и триггера 17 с весами 0,5, 1, 0,5 соответственно подаются на первый вычислительный блок И, на выходе которого формируется частота, пропорциональная второй производной, и знак второй производной. На вход k - разрядного счетчика 22, который обнуляется каждым тактовым импульсом, подается частота Р - -, в результате чего в счетчике в каждом интервале Т формируется линейно нарастающий код ,W ; , (I, 2) который подается на преобразователь «код - частота 10. В качестве опорной частоты на преобразователь 10 подается частота f;, пропорциональная второй производной, вследствие чего выходная частота этого преобразователя,,.1«, ,5/УИ-Л й-1 +0,, (3) где m - разрядность регистров 1, 2, 3, FO--опорная частота преобразователей 7, 8, 9, Блок коммутации 23 подает /пкч le на положительный или отрицательный входы второго вычислительного блока 12, на который с триггеров 14, 15, 16 и с преобразователя «код - астота 8 подаются частоты с коэффициентами 0,25, 0,5, 0,25, 1 соответственно. В результате этого на выходе вычислительного блока 12 формируется частота - - iS- N n -Nln-l + + ( + + )} ее знак signf;; . Частотпо-импульсный сигнал F,; интегрируется реверсивным счетчиком 21, в результате чего код в нем /ре я, о - + а (-i-7V + ±Nln-2 + -.,N n -Nln-l + При выполнении условия «т лг . rjra+l оШ+Аoft выражение (5) приводится к виду , ° /V n +I N n -2Nln-l + + . + + Z){ Z + .(Q) Это выражение описывает параболу второго порядка, проходящую через точки , и , в чем легко убедиться, подставляя в формулу (6) значения , а - 1, и получая , , соответственно. Постоянная преобразователей 7, 8 и 9 Т 2/7i должна быть вдвое меньше интервала квантования Т, что обеспечивается соответствующим выбором FO. Блок синхронизации 20 в зависимости от знака sign РХ переключает реверсивный счетчик 21 на сложение, либо на вычитание. Получение производиой Б виде частотно-импульсного сигнала позволяет ввести в преобразователь простую схему изменения порядка экстраполяции при скачках входного сигнала. Так как воспроизводимая величина имеет непрерывную во времени и ограниченную по модулю производную x(t), то на положительном выходе третьего вычислительного блока 13 импульсов не будет, так как в нормальном реж.име F:i F; триггеры 18 и 19 находятся в нулевом состоянии и на запрещающий вход блока синхронизации 20 подается «О. 5 При скачках входного сигнала производная резко возрастает, первый же импульс на положительном выходе вычислительного блока 13 устанавливает триггер 18 в «I, блок 20 запирает вход реверсивного счетчика 21, третий элемент И 6 открывается и тактовые импульсы проходят на счетный вход триггера 19. Первый из них устанавливает его в «I, второй сбрасывает в «О. При этом обнуляется триггер 18 и запирающий сигнал на входе блока 20 обращается в «О. К этому времени в памяти экстраполирующего преобразователя уже имеются три значения, принадлежащие одной параболе, и вновь осуществляется экстраполяция второго порядка. Таким образом, при каждом скачке входного сигнала на 27 запирается вход реверсивного счетчика 21, что обеспечивает в течение 2Г экстраполяцию нулевого порядка путем записи . в реверсивный счетчик 21. Применение данного экстраполирующего преобразователя обеспечивает более высокую точность, отсутствие перерегулирования, формирует кроме экстраполированного значения кода экстраполированные значения первой и второй производных в виде частоты следования импульсов, что позволяет существенно упростить ряд систем автоматизированного управления и, в частности, станков с программным управлением и частотно-управляемых электроприводов. Формула изобретения Цифровой экстраполирующий преобразователь, содержащий первый регистр, входы которого соединены с установочными входами реверсивного счетчика и с кодовым входом преобразователя, а выходы - со входом первого преобразователя «код-частота и через последовательно соединенные первый элемент И, второй регистр, подключенный ко второму преобразователю «код-частота, второй элемент И и третий регистр - со входами третьего преобразователя «код-частота, причем управляющие входы первого и второго элементов И подключены к тактовому входу преобразователя, отличающийся тем, что, с целью повыщения точности преобразователя, в него введены четыре триггера, первый вычислительный блок, блок синхронизации и последовательно соединенные суммирующий счетчик, четвертый преобразователь «кодчастота, блок коммутации, второй вычислительный блок, входы которого подключены к выходу второго преобразователя «код-частота и единичным выходам первого, второго и третьего триггеров, а выходы через блок синхронизации- ко входам реверсивного счетчика, третий вычислительный блок, пятый триггер, третий элемент И, управляющий вход которого подключен к тактовому входу преобразователя и входу установки в нуль суммирующего счетчика, и щестой триггер, единичный выход которого подключен к нулевому входу пятого триггера, счетные входы второго и четвертого триггеров подсоединены к выходам соответственно первого и третьего преобразователей «код-частота, единичные выходы этих триггеров, подключенные к счетным входам первого и третьего триггеров соответственно, и выход второго преобразователя «код-частота соединены через первый вычислительный блок со входами блока коммутации и четвертого преобразователя «код-частота, причем единичный выход пятого триггера подключен к запрещающему входу блока синхронизации. Источники информации, принятые во внимание при экспертизе 1.Коршунов Ю. М. Цифровые сглаживающие и преобразующие системы, М., «Энергия, 1969 г, стр. 53-55. 2.Авторское свидетельство СССР №486321 М. Кл.2 G06F 15/20, 05.04.74 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1983 |

|

SU1109899A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Устройство для цифровой обработки аналогового сигнала | 1986 |

|

SU1332335A1 |

| Преобразователь частоты в код | 1990 |

|

SU1751851A1 |

| Генератор с управляемой частотой следования импульсов | 1984 |

|

SU1193785A1 |

| Вычислительное устройство для обработки термограмм | 1984 |

|

SU1223251A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Генератор случайного процесса | 1986 |

|

SU1432515A1 |

| Система программного управления электроприводом | 1987 |

|

SU1481708A1 |

| Преобразователь частота-код | 1987 |

|

SU1515368A1 |

Авторы

Даты

1977-03-15—Публикация

1975-05-08—Подача