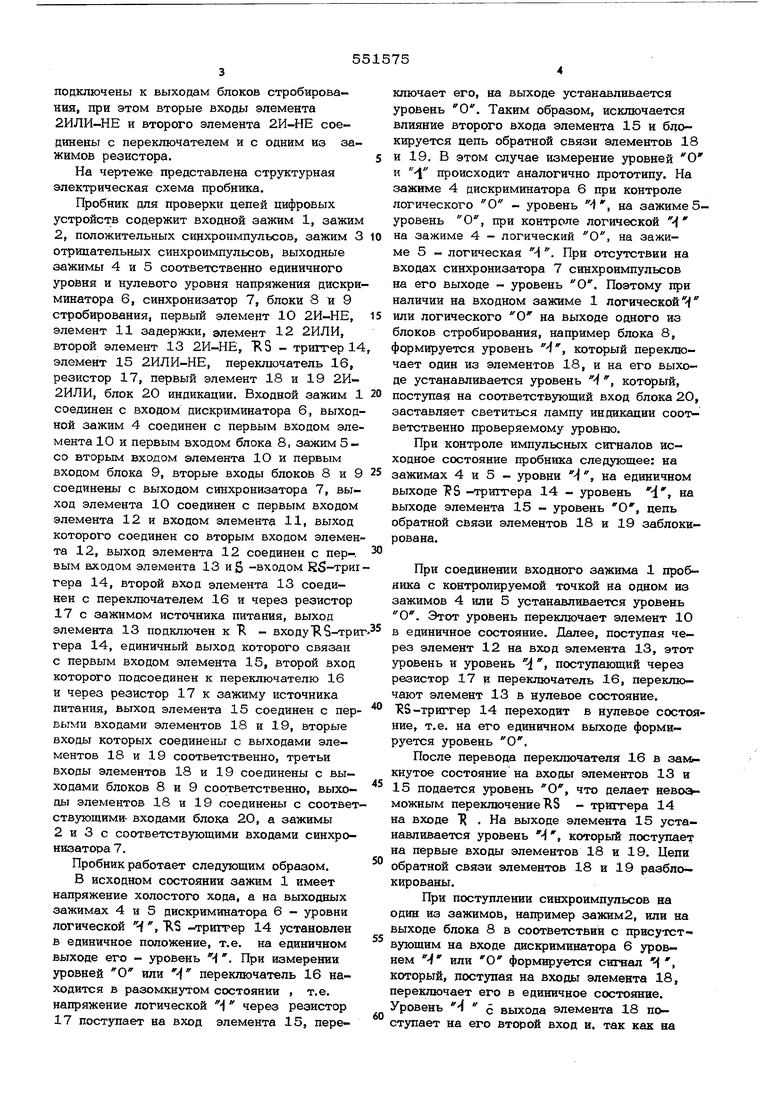

подключены к выходам блоков стробирования, при этом вторые входы элемента 2ИЛИ-НЕ и второго элемента 2И-НЕ соединены с переключателем и с одним из зажимов резистора. На чертеже представлена структурная электрическая схема пробника. Пробник для проверки цепей цифровых устройств содержит входной зажим 1, зажим 2, положительных синхроимпульсов, зажим 3 отрицательных синхроимпульсов, выходные зажимы 4 и 5 соответственно единичного уровня и нулевого уровня напряжения дискри минатора 6, синхронизатор 7, блоки 8 м 9 стробирования, первый элемент 10 2И-НЕ, элемент 11 задержки, элемент 12 2ИЛИ, второй элемент 13 2И-.НЕ, КЗ - триггер 1 элемент 15 2ИЛИ-НЕ, переключатель 16, резистор 17, первый элемент 18 и 19 2И2ИЛИ, блок 20 индикации. Входной зажим соединен с входом дискриминатора 6, выход ной зажим 4 соединен с первым входом эле мента 10 и первым входом блока 8, зажим 5со BTOpbnvi входом элемента 10 и первым входом блока 9, вторые входы блоков 8 и 9 соединены с выходом синхронизатора 7, выход элемента 10 соединен с первым входом элемента 12 и входом элемента 11, выход которого соединен со вторым входом элемен та 12, выход элемента 12 соединен с первым входом элемента 13 и S -входом RS-три гера 14, второй вход элемента 13 соединен с переключателем 16 и через резистор 17 с зажимом источника питания, выход элемента 13 подключен к Т. - входуRS-три гера 14, единичный выход которого связан с первым входом элемента 15, второй вход которого подсоединен к переключателю 16 и через резистор 17 к зажиму источника питания, выход элемента 15 соединен с пер выми входами элементов 18 и 19, вторые входы которых соединены с выходами элементов 18 и 19 соответственно, третьи входы элементов 18 и 19 соединены с выходами блоков 8 и 9 соответственно, выходы элементов 18 и 19 соединены с соответ ствующими- входами блока 20, а зажимы 2 и 3 с соответствующими входами синхронизатора 7. Пробник работает следующим образом. В исходном состоянии зажим 1 имеет напряжение холостого хода, а на выходных зажимах 4 и 5 дискриминатора 6 - уровни логической , RS -триггер 14 установлен в единичное положение, т.е. на единичном выходе его - уровень -t. При измерении уровней О или Ч переключатель 16 находится в разомкнутом состоянии , т.е. напряжение логической Н через резистор 17 поступает на вход элемента 15, переключает его, на выходе устанавливается уровень О. Таким образом, исключается влияние второго входа элемента 15 и бдокируется цепь обратной связи элементов 18 и 19. В этом случае измерение уровней О и происходит аналогично прототипу. На зажиме 4 дискриминатора 6 при контроле логического О - уровень Ч, на зажиме5уровень О, при контроле логической -i на зажиме 4 - логический О, на зажиме 5 - логическая И . При отсутствии на входах синхронизатора 7 синхроимпульсов на его выходе - уровень О. Поэтому при наличии на входном зажиме 1 логической f или логического О на выходе одного из блоков стробирования, например блока 8, формируется уровень М, который переключает один из элементов 18, и на его выходе устанавливается уровень -f , который, поступая на соответствующий вход блока 20, заставляет светиться лампу индикации соответственно проверяемому уровню. При контроле импульсных сигналов исходное состояние пробника следующее: на зажимах 4 и 5 - уровни i, на единичном выходе RS -триггера 14 - уровень i, на выходе элемента 15 - уровень О , цепь обратной связи элементов 18 и 19 заблокирована. При соединении входного зажима 1 пробника с контролируемой точкой на одном из зажимов 4 или 5 устанавливается уровень О. Этот уровень переключает элемент 10 в единичное состояние. Далее, поступая через элемент 12 на вход элемента 13, этот уровень и уровень -{ , поступающий через резистор 17 и переключатель 16, переключают элемент 13 в нулевое состояние. RS-триггер 14 переходит в нулевое состояние, т.е. на его единичном выходе формируется уровень О. После перевода переключателя 16 в зам кнутое состояние на входы элементов 13 и 15 подается уровень О, что делает нево; можным переключение 71S - триггера 14 на входе Т . На выходе элемента 15 устанавливается уровень Ч , который nocTjoiaeT на первые входы элементов 18 и 19. Цепи обратной связи элементов 18 и 19 разбло кированы. При поступлении синхроимпульсов на один из зажимов, например зажим2, или на выходе блока 8 в соответствий с присутствующим на входе дискриминатора 6 уровнем или О формируется сигнал -i , который, поступая на входы элемента 18, переключает его в единичное состояние. Уровень i S выхода элемента 18 пост5Т1ает на его второй вход и, так как на первом входе уровень И, происходит запо минание результата измерения. Если контролируемый сигнал имеет исхо ный уровень, находящийся в нецопустымых пределах, то на зажимах 4 и 5 в момент измерения этого уровня устанавливаются уровни -( , которые вызывают переключени элемента 10, элемента 12, и RS -тригге ра 14. На выходе RS - триггера 14 устанавливается уровень Ч , который переключает элемент 15. На выходе элемента 15 устанавливается уровень О, которы поступая на входы элементов 18 и 19 заблокирует цепи обратной связи. Так как в ЭТО время на выходах блоков 8 и 9 присут ствуют уровни О (синхроимпульс отсутствует), происходит установка в нулевое состояние того элемента 18 или 19, который запомнил результат измерения. При последующем изменении уровня напряжения контролируемого сигнала до величины, соответствующей логическому О или Ч, например, переключение с плохой логической -1 в хороший логический О или при переключении с плохого О в ло гическую , - триггер 14 не переключается, так как элемент 13 не переключается, на Одном из его входов уже присутствует портоянный уровень О, На выходе элементов 15 присутствует постоянный уровень О, который блокирует цепь обратной связи элементов 18 и 19. Результатат измерения элементом 18 не запоминается. Если контролируемый сигнал имеет оба уровня в допустимых пределах, то в любой момент на одном из зажимов 4 или 5 присутствует уровень О, который не вызывает переключение RS -триггера 14. На выходе элемента 15 будет постоянно присутствовать уровень Ц , который позволяет элементу 18запомнить результат измерения. Элемент 11 введен для того, чтобы исключить переключеШге -триггера 14 при переключении контролируемого сигнала из одного логического состояния в другое. так как в это время из-за переходных процессов возможны случаи кратковременного установления на зажимах 4 и 5 уровней i . Таким образом, результат измерения уровйя напряжения контролируемого сигнала запоминается в том случае, если оба уровня напряжения контролируемого сигнала имеют допустимые значения, т.е. повышается достоверность контроля. и 3 о б D е т е н и я мула Пробник для проверки цепей цифровых устройств, содержащий дискриминатор, сигхронизатор, выход которого соединен с ас-: выми входами блоков стрэбировгни;;: «т рые входы которых соединены с выхэ..а:.;: дискриминатора, и блок ин.цикап-: } тличающийся тем, что с целью повышения достоверности контроля им- пульсного сигнала в режиме внешней синхронизации, в него введены два элемента 2ИНЕ, элемент задержки, элемент 2ИЛИ, 1 5триггер элемент 2ИЛИ-НЕ, два элемента 2И-2ИЛИ, резистор и переключатель, при этом выходы дискриминатора соединены со входами первого элемента 2И-НЕ, выход которог о подключен к первому и через элемент задержки ко второму входам элемента 2ИЛИ, выход элемента 2ИЛИ подключен к S - входу и через второй элемент 2И-НЕ к 1 - входу -триггера, единичный выход которого связан через элемент 2ИЛИ-НЕ с первыми входами элементов 2И-2ИЛИ, вторые входы которых соединены с выходами этих элементов и входами блоков индикации, а третьи и четвертые входы элементов 2И-2ИЛИ подключены к выходам блоков стробирования, при этом вторые входы элемента 2ИЛИ-НЕ и второго элемента 2И-НЕ соединены с переключателем и с одним из зажимов резистора. Источники информации, принятые во внимание при экспертизе: 1.Заявка Великобритании № 1361237. QOllR 19/16, 05. 09. 72г. 2.Патент США № 3742351, QOlR 31/О2, 19. 06. 73 г. - (прототип).

JZ

| название | год | авторы | номер документа |

|---|---|---|---|

| Пробник для проверки логических устройств на микросхемах эмиттерно-связанной логики | 1983 |

|

SU1108373A1 |

| ЛОГИЧЕСКИЙ ПРОБНИК | 1991 |

|

RU2041473C1 |

| Бесконтактный переключатель | 1979 |

|

SU834912A1 |

| Логический пробник | 1986 |

|

SU1352420A1 |

| Малогабаритный цифровой твердомер | 1984 |

|

SU1359716A1 |

| Устройство для синхронизации группы преобразователей | 1984 |

|

SU1231566A1 |

| Устройство для проверки логических микросхем | 1988 |

|

SU1596291A1 |

| Дискриминатор импульсов | 1978 |

|

SU764098A1 |

| Устройство для управления встречно-параллельно включенными тиристорами | 1979 |

|

SU884144A1 |

| Устройство для синхронизации преобразователей,включаемых параллельно на общую нагрузку | 1985 |

|

SU1319182A1 |

h«

-0

77

-0

Авторы

Даты

1977-03-25—Публикация

1975-08-12—Подача