(54) ЛОГИЧЕСКИЙ ЗАПОМИНАЮЩИЙ БЛОК

чен к одним входам второго и третьего дополнительных элементов И, другие входы которых подключены к разрядным шинам, а. выходы - ко входам второго элемента памяти, выходы которого соединены с одними входали четвертого и пятого дополнительных элементов И. Один вход шестого дополнительного элемента И подключен к адресной шане, другой - к одной из управляющих шин, а выход - к другим входам четвертого и пятого дополнительных элементов И, выходы которых соединены с разрядными шинами. Инверсный выход второго элемента памяти подключен к одному входу седьмого дополнительного элемента И, другой вход которого соединен с одной из управляющих шин, а выход - с одним входом элемента ИЛИ, другой вход которого подключен к прямому выходу первого элемента памяти, а выход - к выходной ишне. Прямой выход второго элемента памяти подключен к одному входу восьмого дополнительного элемента И, другой вход которого соединен с одной из управляющих шин, а выход - с одним из входов первого элемента памяти.

Это позволяет вьиюлнять операции сложного ассоциативного поиска, что существенно расширяет область применения логического запоминающего блока.

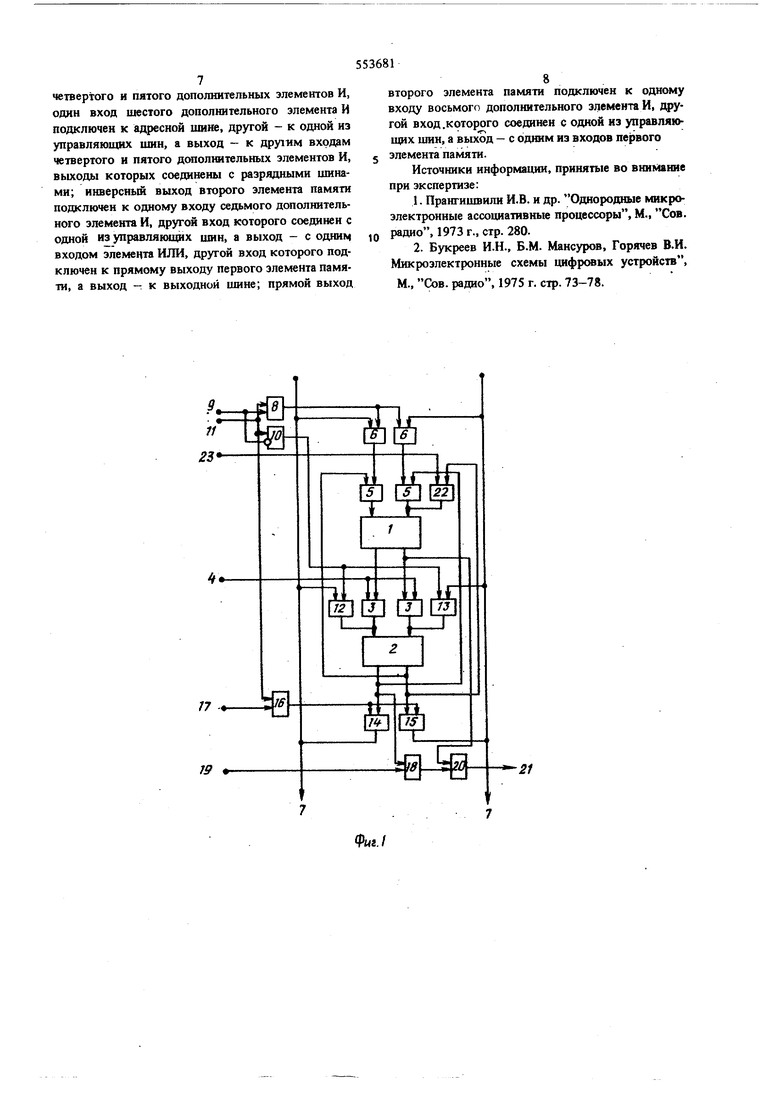

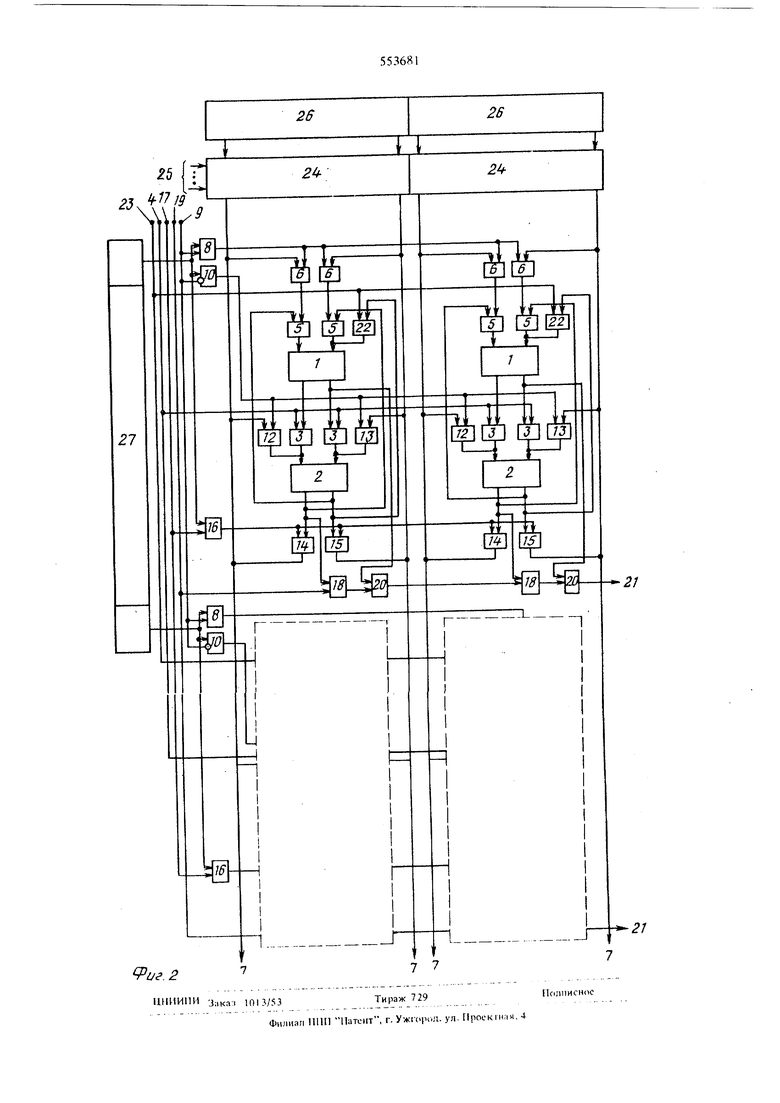

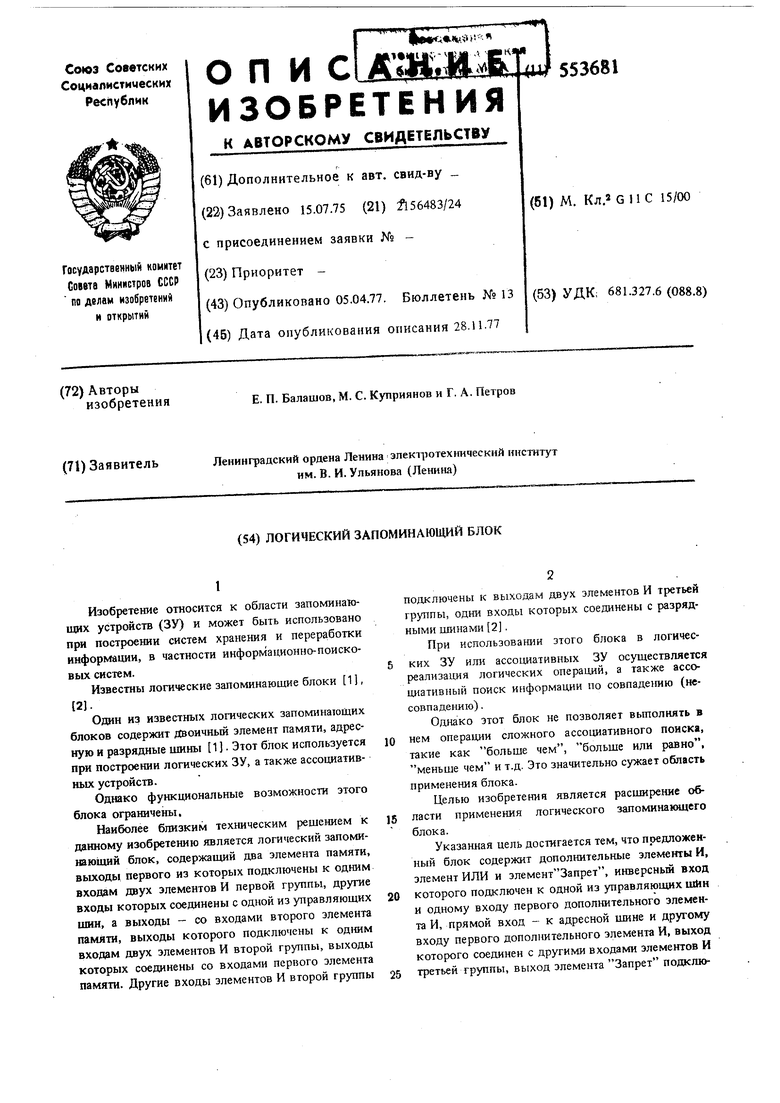

На фиг. 1 изображена функциональная схема логического запоминающего блока; на фиг. 2 структурная схема логического ЗУ с использованием логического запоминающего блока.

Логический запоминаю1дий блок содержит два элемента памяти 1 и 2. Выходы первого элемента 1 подключены к од1шм из входов двух элементов И 3 первой группы, другие входы которых соединены с управляющей шиной 4, служащей для синхронизаЩ1И. Выходы элемента памяти 2 подключены к одним входаМ двух элементов И 5 второй группы, другие входы которых соединены с выходами элементов И 6 третьей группы, входы которых соединены с разрядными шинами 7.

Один из входов первого дополнительного элемента И 8 соединен с управляющей шиной 9 и инверсным входом элемента Запрет 10, прямой вход которого и другой вход элемента И 8 соединены с адресной шиной 11 Выход элемента 8 соединен с другими входами элементов И 6. Выход элемента 10 подключен к одним входам второго 12 и третьего 13 дополнительных элементов И, другие входы которых подключены к шинам 7, а выходы - ко входам второго элемента памяти 2, выходы которого соединены с одними входами четвертого 14 и пятого 15 дополнительных элементов И. Один вход шестого дополнительного элемента И 16 подключен к шине И, другой - к управляющей шине 17, служащей для считьшания, а выход - к другим входам элементов И 15 и 14, выходы которых соединены с 1цинами7. Инверсный выход элемента памяти 2 подключен к одному входу седьмого дополнительного элемента 18, другой вход которого соединен с управляющей шиной 19, служащей дг1я сравнения, а выход - с одним входом элемента ИЛИ 20, другой вход которого подключен к прямому выходу первого элемента памяти 1, а выход - к выходной шине 21. Прямой выход элемента памяти 2 подключен к одному восьмого дополнительного элемента И 22, другой вход которого соединен с управляющей шиной 23, а выход - с.одним из входов элемента памяти 1.

Логическое ЗУ содержит (фиг. 2) управляющие блоки 24, одни входы которых соединены с настроечными шинами 25, .а другие - с выходами регистра входного слова 26. Адрес1п 1е шины логических запоминающих блоков образующих накопитель логического ЗУ, подключены к соответствующим выходам регистра адреса 27.

Рассмотрим работу логического запоминающего блока при записи и считывании информации, реализации элементарных логических операций, а также операш1Й простого и сложного поисков.

Управляющие блоки 24 функционируют также как и в обычном логическом ЗУ.

Запись информации в логический запоминающий блок может производиться как в элементы памяти, так и в элементы памяти 2. В первом случае устанавливается в единичное состояние соответствующий разряд регистра адреса 7, и подается сигнал на управляющую шину 9. Входное слово X (xi, Х2,..., Хр) с разрядных шин 7 записывается через элементы И 5 и6 в элемент памяти. Во вторам случае сигнал на управляющую Ц1ину 9 не подается. В результате на выходе элемента Запрет 10 возникает сигнал, поступающий на элементы И 12 и 13, поэтому входное слово X с разрядных шин 7 записывается в элемент памяти 2.

Для считывания информации в единичное состояние устанавливается соответствующий разряд регистра адреса 27, и подается сигнал на щину 17. В результате на выходе элемента И 16 возникает сигнал, поступающий на элементы И 14 и 15 и информация с выходов элемента памяти 2 поступает на шины 7. При хранении информации в элементах памяти 1 подается сигнал на шину 4. В результате информация переписывается в элементы памяти 2, а потом производится считывание.

Выполнение элементарных логических операций (дизъюнкции, конъюнкции, запрета и др. в режиме записи информации в элементы памяти 1 или 2 производится так же, как и в известном логическом запоминающем блоке 1 .

Реализуя логическую операцию неравнозначности или равнозначности между входным словом X (Х,Х2,..., Хп) и любым словом устройCTBav(- ,у ...,у УИЛИ целым массивом слов, можно производить простой поиск информации. Для этого набор сигналов подается на настроечные шины 25, соответствующий, например, операции неравнозначности, устанавливаются в единичное состояние соответствуюшие разряды регистра адреса 27 и подается сигнал на управляюшую шину 9. В i -ом разряде j-ro слова массива реализуется операция неравнозначности () i-N Результат операции получается в элементе памяти 1. При подаче сигнала на шину 4 результат операции переписывается в элемент памяти 2, и единичный сигнал на одной из прямых разрядных шин 7 при считывании результата операции свидетельствует о несовпаде1ши входного слова и слова, хранящегося в данной числовой линейке. Для восстановления исходной информации производится повторно операция неравнозначности ® 1гУнВыполнение операций сложного поиска рассмотрим на примере сравнения информации по числовому критерию больше чем. Для определения соотношения xj Vji необходимо выполнить логическую операвдю Zj, xi7ji. Причем х Vj имеет место только в том случае, если выполняются соотношения ИxiVii 1, Л l, 1,«fM+lИз зтих выражении следует, что для определения соотношения х yj необходимо иметь цепочку переносов для анализа значений xj и vji в каждом из разрядов кодов х и у. Данную цепочку образуют последовательно соединенные элементы И 18 и ИЛИ 20. Операция сравнения информации по числовому критерию больше чем производится следующим образом; 1)в исходном состоянии элементы памяти 1 и 2 хранят значение Vji; 2)в элементе памяти 1 реализуется логическая операция xjyjj, результат которой с прямого выхода элемента памяти 1 поступает ка один из входов элемента ИЛИ 20. 3)в элементе памяти 2 реализуется логическая операция )ciyji , и с инверсного выхода снимается результат логической операции xivjj xivvjij который подается на одипиз входов элемента И 18; 4)подается сигнал на шину 17, и сигнал на шине 21 свидетельствует о выполнении условия х У, а его отсутствие - о выполнении условия х yj . -Рассмотренная операция сравнения информации по числовому критерию больше чем может быть вьшолнена одновременно над всем объемом хранимой в устройстве информации. Результаты сравнения фиксируются на шинах 21. Для восстановления исходной информации необходимо сложить результаты логических операций, полученных в элементах памяти 1 и 2, и произвести операцию неравнозначности yii Jjn ®yii () . Это осуществляется при подаче сигнала на цшну 23, вследствие чего результат ло1ической операции xivjj поступает на единичньш вход элемента памяти 1, т.е. происходит логическое сложение с результатом логической операции xiyjj 1рсле этого подается сигнал на шину полученная логическая сумма переписывается в элемент памяти 2. Операция неравнозначности производится так же как было рассмотрено выше. Следует отметить, что рассмотренные операции, выполняемые блоком, не исчерпывают его функциональных возможностей. В нем эффективно выполняется логическая обработка массивов информации: логическое сложение, умножение, инвертироваиие матриц, упорядочение информации. Логическое сложе1ше массивов было уже использовано при вьтолнеиии операции сравнения по числовому критерию больше чем. Рассмотрим в качестве примера логическое умножение массивов информаш1И. Конъюнк шя одноименных элементов массивов и 1формации можно П х:дставить в следующем виде; jr nyir IT Следовательно, для реализации логического умножения лЧвух массивов информации необходимо в элементы памяти 1 и 2 записать инверсные значения элементов, сложить их, и полученную сумму цроинвертировать. Инвертарование производится при подаче определенного набора управляющих сигналов па настроечные шины 25. Формула изобретения Логический запоминающий блсж, содержаший два элемента памяти, выходы первого из которых подключены к одним входам двух элементов И первой группы, другие входы которых соединены с одной из управляющих щин, а выходы - со входами второго элемента памяти, -выходы которого подключены к одним входам двух элементов И второй группы, выходы которых соединены со входами первого элемента памяти, другие входы элементов И второй группы подключены к выходам двух элементов И третьей группы, одни входы которых соединены с разрядными шинами, отличающийся тем, что, с целью расширения области применения блока, он содержит допол1штельные элементы И, элемент ИЛИ в элемент Запрет, инверсный вход которого подключен к одной из управлянзших щин и одному входу первого дополнительного элемента И, прямой вход - к адресной шине и другому входу первого дополнительного элемента И, выход которого соединен с другими входами элементов И третьей группы; выход элемента Запрет подключен к од1шм входам второго и Т1 еть€го дополнительных элементов И, другие входы которых подключены к разрядным шинам, а выходы - ко входам второго элемента памяти, выходы KOToporrj соединены с одними входами

четвертого и пятого дополнительных элементов И, один вход шестого дополнительного элемента И подключен к адресной шине, другой - к одной из управляющих шин, а выход - к друшм входам четвертого и пятого дополнительных элементов И, выходы которых соединены с разрядными шинами; инверсный выход второго элемента памяти подключен к входу седьмого дополнительного элемента И, другой вход которого соединен с одной из управляющих шин, а выход - с одним входом элемента ИЛИ, другой вход которого подключен к прямому выходу первого элемента памяти, а выход - к выходной щине; прямой выход

S

второго элемента памяти подключен к одному входу восьмого дополнительного элемента И, арутон вход .которого соединен с одной из управляющих шин, а выход - с одним из входов первого элемента памяти.

Источники информации, принятые во внимаиие при экспертизе:

1.Прангипшили И.В. и др. Однородные микроэлектроиные ассош1ативные процессоры, М., Сов. радио, 1973 г., стр. 280.

2.Букреев И.Н., Б.М. Мансуров, Горячев В.И. Микроэлектронные схемы цифр(ых устройств,

М., Сов. радио, 1975 г. стр. 73-78.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональное ассоциативное запоминающее устройство | 1984 |

|

SU1191942A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Ассоциативное запоминающее устройство | 1981 |

|

SU978196A1 |

| Логическое запоминающее устройство | 1975 |

|

SU533990A1 |

| Элемент ассоциативной памяти | 1980 |

|

SU875460A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957276A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

№

Авторы

Даты

1977-04-05—Публикация

1975-07-15—Подача