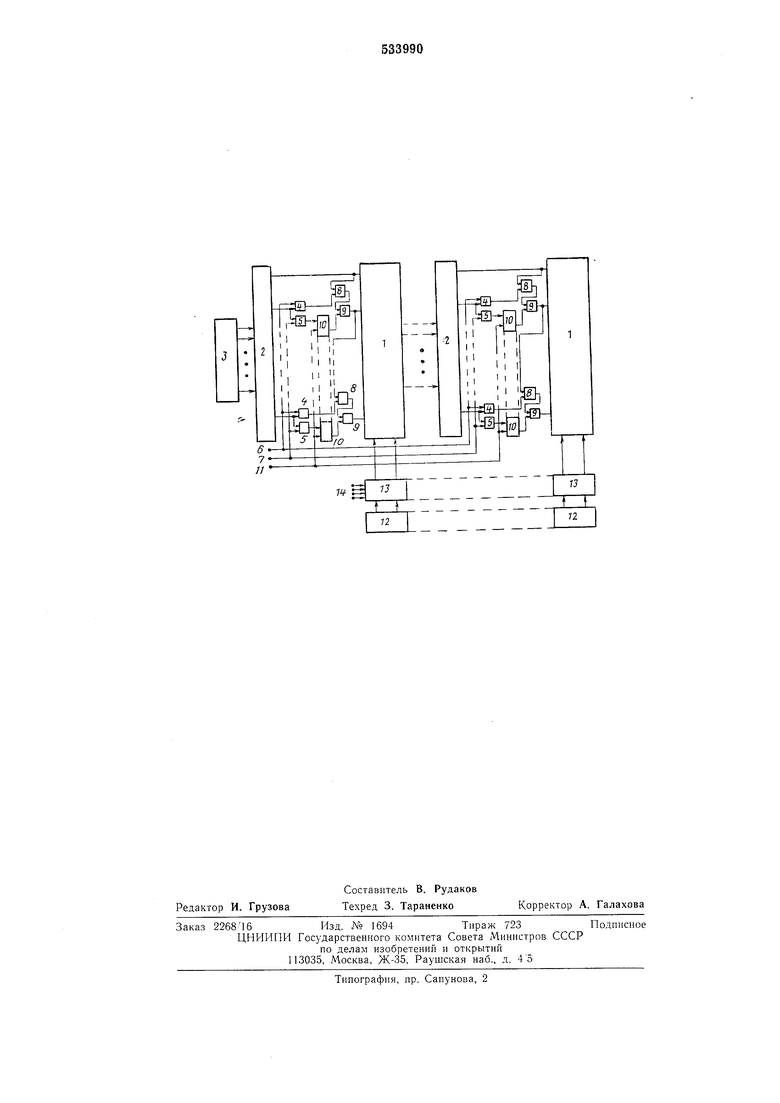

Устройство содержит блоки 1 памяти, дешифраторы 2 адреса, регистр 3 адреса. Выходы регистра адреса подключены к входам дешифраторов 2 адреса блоков 1 памяти, иервый выход дешифратора адреса - непосредствеиио к первому адресиому входу блока памяти, а каждый последуюш,ий выход дешифратора - к одним входам первого 4 и второго 5 элементов «И. Другой вход элемента «И 4 соединен с управляюшей шиной 6, другой вход элемента «И 5 - с управляюш,ей шиной 7. Выход элемента «И 4 подсоединен к одпому входу элемента «ИЛИ 8, другой вход которого подключен к предыдушему адресному входу блока памяти, а выход - к одному входу третьего элемента «И 9, выходом связанного с соответствуюш,им адресным входом блока памяти, а вторым входом - с инверсным выходом соответствуюш,его разряда дополнительного регистра 10. Единичный вход регистра 10 соединен с выходом элемента «И 5, а нулевой вход - с управляюш,ей шиной 11. Устройство содержит также регистр 12 входного слова, подключенный к одним входам блока 13 управления, другие входы которого подсоединены к управляющим шинам 14, а выходы - к разрядным входам блоков 1 памяти.

Рассмотрим работу логического запоминаюш,его устройства.

В исходном положении в регистре 12 хранится входное слово, а в каждой числовой линейке накопителя, образованного совокупностью блоков памяти, - некоторое слово массива; регистр 10 находится в нулевом состоянии.

Выполнение логических операций (например -конъюнкции, дизъюнкции, запрета) над входным словом и словом избранной числовой линейки происходит при нодаче определенного набора сигналов на шины 14 и возбуждении соответствующего адресного входа. Для выбора определенной числовой линейки на регистре 3 адреса устанавливается соответствующий код и подается сигнал на шину 7. Сигнал на выходе дешифратора 2 адреса через элемент «И 5 поступает на единичный вход соответствующего триггера регистра 10 и устанавливает его в единичное состояние. Затем подается сигнал на управляющую шину 6 и сигнал с выхода дешифратора 2 адреса через элементы «И 4, «ИЛИ 8, «И 9 поступает на адресный вход блока 1 памяти.

При выполнении логических операций между входным словом и группой слов массива

информации в первом такте подается адрес конца массива (последней числовой линейки) и сигнал на выходе дешифратора адреса при поступлении сигнала на шину 7 устанавливает соответствующий триггер регистра 10 в единичное состояние. Во втором такте подается адрес начала массива (первой числовой линейки) и сигнал соответствующего выхода дещифратора адреса возбуждает последовательно все адресные входы блоков памяти требуемого массива информации. Триггер регистра, установленный в единичное состояние в первом такте, запрещает возбуждение адресных входов вне требуемого массива информации.

Таким образом, при помощи двух команд с «-разрядным полем адреса можно обращаться к массиву объемом 2 слов.

Формула изобретения

Логическое запоминающее устройство, содержащее регистр адреса, подключенный к дещифраторам адреса, регистр входного слова, выходы которого соединены с входами блока управления, уиравляющие шины, выходы блока управления подключены к разрядным входам блоков памяти, отличающееся тем, что, с целью расширения функциональпых возможностей устройства, оно содержит дополнительные регистры и элементы «И и «ИЛИ, первый выход каждого дешифратора адреса подключен к первому адресному входу соответствующего блока памяти, а другие выходы соединены с одними входами первого и второго элементов «И, выход каждого первого элемента «И подключен к одпому входу соответствующего элемента «ИЛИ, второй вход элемента «ИЛИ соединен с предыдущим

адресным входом блока памяти, а выход - с одним входом третьего элемента «И, выход которого подключен к соответствующему адресному входу блока памяти, а другой вход - к соответствующему инверсному выходу дополнительного регистра, входы которого подключепы соответственно к выходам вторых элементов «И и к одной из управляющих шип, другие управляющие шины подключены к другим входам первого и второго элементов

«И.

Источники информации, принятые во внимание при экспертизе:

1. Авт. св. 432598, кл. G ПС 15/00, 1972. 2. Авт. св. 477464, кл. G ПС 15/00, 1974.

И

ffa-

ТЖн

Ш

T-W

ff7И

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Логическое запоминающее устройство | 1979 |

|

SU858103A2 |

| Логический запоминающий блок | 1975 |

|

SU553681A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

Авторы

Даты

1976-10-30—Публикация

1975-07-15—Подача