(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ОПЕРАТИВНОЙ ПАМЯТИ

1

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля блоков оперативной памяти, в котором выполняется двукратное обращение по каждому адресу в пределах всей емкости памяти 1.

Недостатками этого устройства являются низкое быстродействие и отсутствие контроля адресных трактов устройства.

Наиболее близко к предлагаемому устройство для контроля блоков оперативной памяти (ОЗУ), содержащее адресный и числовой регистры, накопитель, формирователи сигналов записи и считывания, местное устройство управления, входные и выходные усилители, адресные и числовые шины, причем при контроле ОЗУ предлагается поячеечная запись-считывание информации и сравнение в ЦВМ считанного результата с тем, который записывался 2.

Недостатком этого устройства является невозможность проверки цепей адресного тракта ОЗУ и встроенных буферных ОЗУ, что снижает достоверность контроля.

Цель изобретения - повышение достоверности контроля блоков оперативной памяти.

Поставленная цель достигается тем, что в устройство для контроля блоков оперативной памяти, содержащее адресный и числовой регистры, формирователи сигналов записи, входные и выходные усилители, блок местного управления и формирователи сигналов считывания, выходы которых под10ключены к одним из входов числового регистра, выходы которого соединены с одними из входов выходных усилителей и формирователей сигналов записи, другие входы которых подключены к одним из входов входных усилителей и первому выходу блока мест15ного управления, другие входы выходных усилителей соединены с вторым выходом блока местного управления и одними из входов формирователей сигналов считывания, другие входы числового регистра подключены соответственно к выходам входных усилителей и к третьему выходу блока местного управления, четвертый выход и первый вход которого соединены соответственно с входом и первым выходом адресного регистра, второй выход которого, выходы формирователей сигналов записи и другие входы формирователей сигналов считывания являются соответственно адресным выходом, выходами записи и входами считывания устройства, информационными входами и выходами которого являются соответственно другие входы входных усилителей и выходы выходных усилителей, первый выход, выходы с пятого по восьмой и второй и третий входы блока местного управления являются управляющими выходами и одними из управляющих входов устройства, введены регистр команд, элементы неравнозначности и элементы И, выходы которых подключены к одним из входов числового регистра, а входы соединены соответственно с выходами элементов неравнозначности и с первым выходом регистра команд, второй выход которого подключен к первому входу элементов неравнозначности, второй вход которых соединен с третьим выходом адресного регистра, третий выход и одни из входов регистра команд подключены соответственно к четвертому входу блока местного управления и к другим входам входных усилителей, другой вход регистра команд является другим управляющим входом устройства.

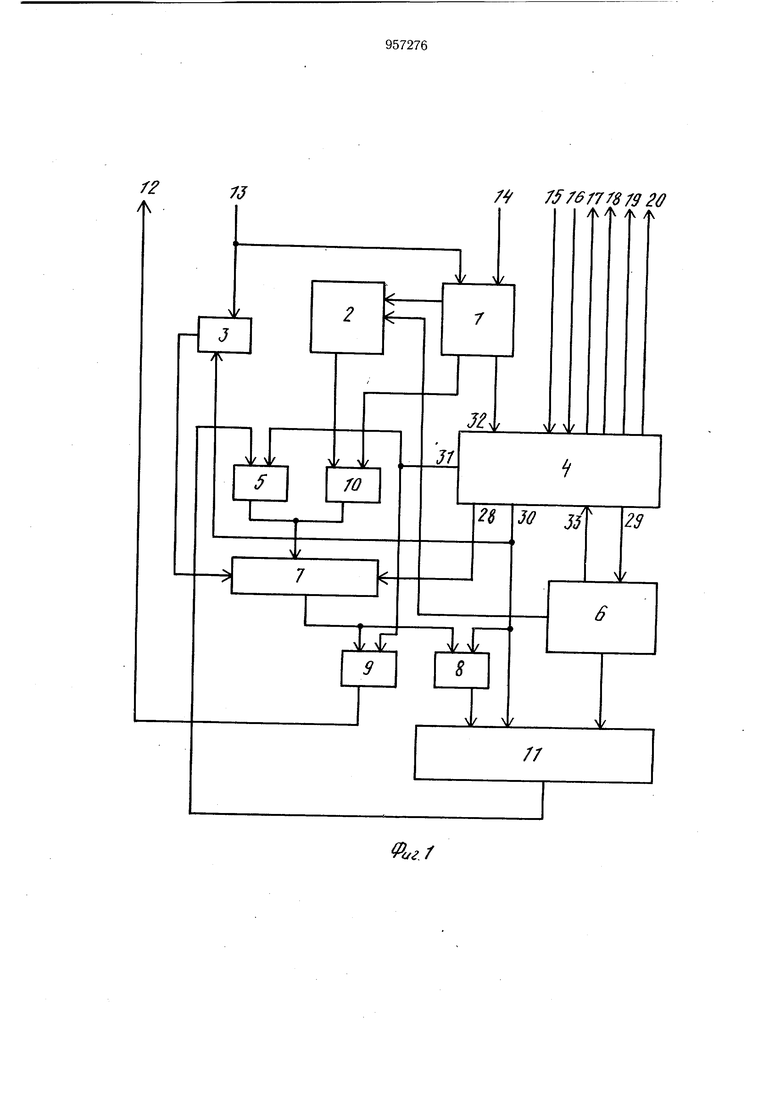

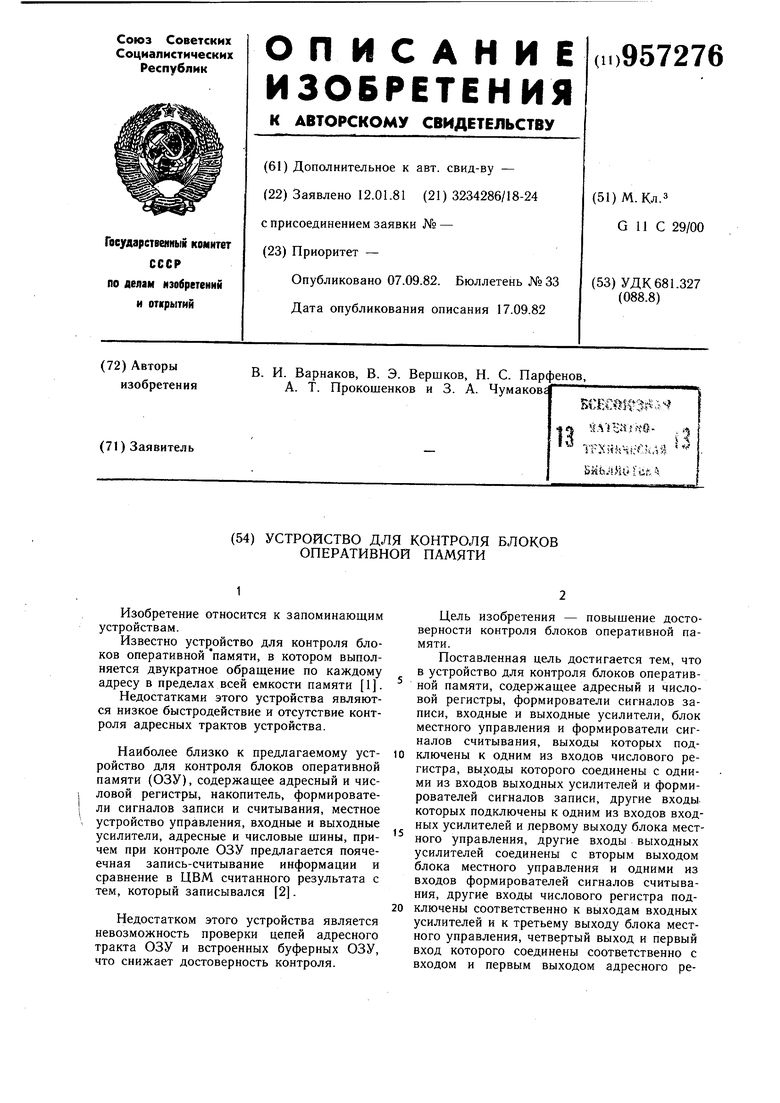

Блок местного управления содержит регистр операции, схему сравнения и дополнительные элементы И, причем первые входы первого и второго дополнительных элементов И подключены соответственно к первому и второму выходам регистра операции, третий выход которого соединен с первым входом третьего дополнительного элемента И, а четвертый выход - с первыми входами четвертого и пятого дополнительных элементов И, вторые входы которых подключены к первому входу схемы сравнения, выходы которой соединены соответственно с вторыми входами лервого, второго и третьего дополнительных элементов И, второй вход схемы сравнения, первый и второй входь регистра операции и первый вход схемы сравнения являются соответственно входами с первого по четвертый блока, выходами которого с первого по восьмой являются соответственно выходы четвертого и пятого дополнительных элементов И, пятый выход регистра операции, выход третьего дополнительного элемента И, шестой выход регистра операции, выходы первого и второго дополнительных элементов И и седьмой выход регистра операции.

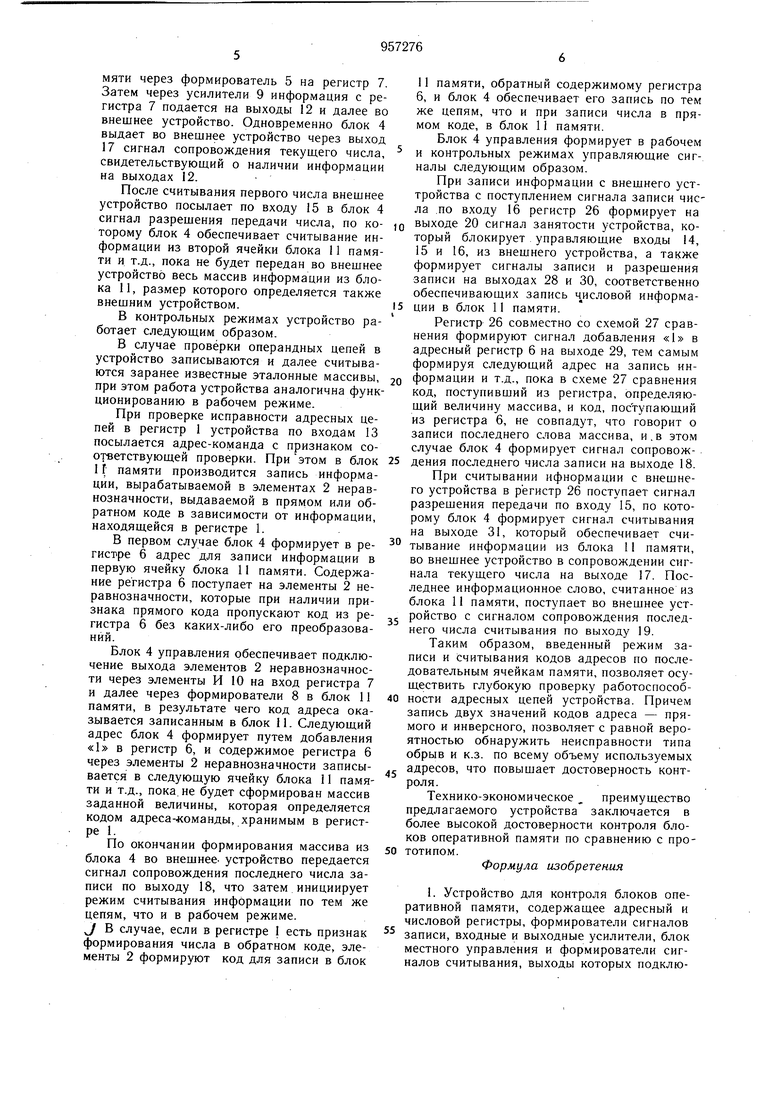

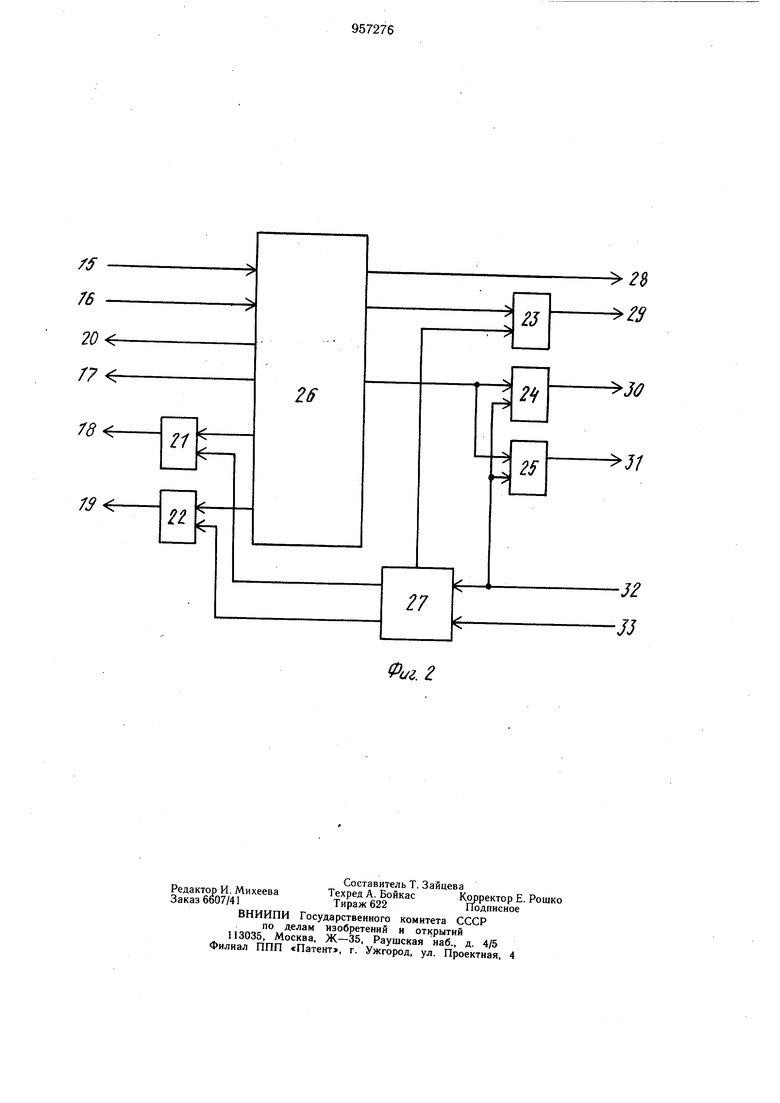

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока местного управления.

Устройство содержит регистр 1 команд, элементы 2 неравнозначности, входные усилители 3, блок 4 местного управления, формирователи 5 сигналов считывания, адресный регистр 6, числовой регистр 7, формирователи 8 сигналов записи, выходные усилители 9 и элементы И 10, контролируемый блок 11 оперативной памяти (ОЗУ), информационные выходы 12 и входы 13 устройства, управляющие входы 14 записи команд,

15 разрешения передачи числа и 16 записи числа , управляющие выходы 17 сопровождения текущего числа, 18 сопровождения последнего числа при записи, 19 сопровождения последнего числа при считывании и 20 занятости устройства.

Блок 4 местного управления содержит первый 21, второй 22, третий, четвертый 24 и пятый 25 дополнительные элементы И, регистр 26 операции и схему 27 сравнения, выходы 28-31 и входы 32 и 33.

5 Разрядность цепей элементов 2 неравнозначности равна разрядности числовой части устройства, и в случае, если разрядность адресной части меньше числовой, каждый разряд адресного регистра 6 повторяется в элементах 2 неравнозначности необходимое количество раз, т.е. в зависимости от соотношения разрядности адресной и числовой частей устройства.

Устройство может работать в рабочем и контрольных режимах.

В рабочем режиме пер-эд началом работы по входам 13 (фиг. 1) поступает адрескоманда (А-К) в сопровождении сигнала записи числа в регистр I по входу 14, в

результате чего она записывается в регистр 1. Если в А-К присутствует признак «Рабо0 та, то запись информации в блок 11 памяти производится с внешнего устройства. Запись информации производится при поступлении сигнала по входу 16, при этом блок 4 управления обеспечивает формирование адреса на запись в первую ячейку блока 11

памяти и подключение информации с входов 13 через усилитель 3 на регистр 7. После записи информации в регистр 7 производится его подключение через формирователь 8 к блоку 11 памяти и запись этой информации в блок 11 по адресу, сформированному в регистре 6.

После записи первого числа в блок 11 памяти блок 4 управления снимает сигнал занятости с выхода 20 и формирует следующий адрес путем увеличения содержимого регистра 6 на «1. С поступлением следующего слова по входам 13 в сопровождении сигнала записи числа по входу 16 блок 4 обеспечивает запись аторого слова в следующую ячейку блока 11 памяти и т.д., пока не будет записан (сформирован) массив определенной величины. Размер массива определяется внещним устройством. Считывание информации-в устройстве производится путем подачи сигнала разрешения передачи числа по входу 15 в блок 4, который

5 по этому сигналу обеспечивает обнуление регистра 6 и, таким образом, считывание информации из первой ячейки блока 11 памяти через формирователь 5 на регистр 7 Затем через усилители 9 информация с регистра 7 подается на выходы 12 и далее во внешнее устройство. Одновременно блок 4 выдает во внешнее устройство через выход 17 сигнал сопровождения текуш,его числа, свидетельствующий о наличии информации на выходах 12. После считывания первого числа внешнее устройство посылает по входу 15 в блок 4 сигнал разрешения передачи числа, по которому блок 4 обеспечивает считывание информации из второй ячейки блока 11 памяти и т.д., пока не будет передан во внешнее устройство весь массив информации из блока И, размер которого определяется также внешним устройством. В контрольных режимах устройство работает следующим образом. В случае проверки операндных цепей в устройство записываются и далее считываются заранее известные эталонные массивы, при этом работа устройства аналогична функ ционированию в рабочем режиме. При проверке исправности адресных цепей в регистр 1 устройства по входам 13 посылается адрес-команда с признаком соответствующей проверки. При этом в блок IF памяти производится запись информации, вырабатываемой в элементах 2 неравнозначности, выдаваемой в прямом или обратном коде в зависимости от информации, находящейся в регистре 1. В первом случае блок 4 формирует в регистре 6 адрес для записи информации в первую ячейку блока 11 памяти. Содержание регистра 6 поступает на элементы 2 неравнозначности, которые при наличии признака прямого кода пропускают код из регистра 6 без каких-либо его преобразований. Блок 4 управления обеспечивает подключение выхода элементов 2 неравнозначности через элементы И 10 на вход регистра 7 и далее через формирователи 8 в блок 11 памяти, в результате чего код адреса оказывается записанным в блок И. Следующий адрес блок 4 формирует путем добавления «1 в регистр б, и содержимое регистра б через элементы 2 неравнозначности записывается в следующую ячейку блока 11 памяти и т.д., пока, не будет сформирован массив заданной величины, которая определяется кодом адреса-команды, хранимым в регистре 1. По окончании формирования массива из блока 4 во внешнее, устройство передается сигнал сопровождения последнего числа записи по выходу 18, что затем инициирует режим считывания информации по тем же цепям, что и в рабочем режиме. J В случае, если в регистре 1 есть признак формирования числа в обратном коде, элементы 2 формируют код для записи в блок 11 памяти, обратный содержимому регистра б, и блок 4 обеспечивает его запись по тем же цепям, что и при записи числа в прямом коде, в блок 11 памяти. Блок 4 управления формирует в рабочем и контрольных режимах управляющие сигналы следующим образом. При записи информации с внешнего усттройства с поступлением сигнала записи числа по входу 16 регистр 26 формирует на выходе 20 сигнал занятости устройства, который блокирует управляющие входы 14, 15 и 16, из внешнего устройства, а также формирует сигналы записи и разрешения записи на выходах 28 и 30, соответственно обеспечивающих запись ч исловой информации в блок 11 памяти. Регистр 26 совместно со схемой 27 сравнения формируют сигнал добавления «1 в адресный регистр б на выходе 29, тем самым формируя следующий адрес на запись информации и т.д., пока в схеме 27 сравнения код, поступивший из регистра, определяющий величину массива, и код, поступающий из регистра 6, не совпадут, что говорит о записи последнего слова массива, и.в этом случае блок 4 формирует сигнал сопровождения последнего числа записи на выходе 18. При считывании ифнормации с внешнего устройства в регистр 26 поступает сигнал разрешения передачи по входу 15, по которому блок 4 формирует сигнал считывания на выходе 31, который обеспечивает считывание информации из блока 11 памяти, во внешнее устройство в сопровождении сигнала текущего числа на выходе 17. Последнее информационное слово, считанное из блока 11 памяти, поступает во внешнее устройство с сигналом сопровождения последнего числа считывания по выходу 19. Таким образом, введенный режим записи и Считывания кодов адресов по последовательным ячейкам памяти, позволяет осушествить глубокую проверку работоспособности адресных цепей устройства. Причем запись двух значений кодов адреса - прямого и инверсного, позволяет с равной вероятностью обнаружить неисправности типа обрыв и к.з. по всему объему используемых адресов, что повышает достоверность контроля. Технико-экономическое преимущество предлагаемого устройства заключается в более высокой достоверности контроля блоков оперативной памяти по сравнению с прототипом. Формула изобретения 1. Устройство для контроля блоков оперативной памяти, содержащее адресный и числовой регистры, формирователи сигналов записи, входные и выходные усилители, блок местного управления и формирователи сигналов считывания, выходы которых подключены к одним из входов числового регистра, выходы которого соединены с одними из входов выходных усилителей и формирователей сигналов записи, другие входы которых подключены к одним из входов входных усилителей и первому выходу блока местного управления, другие входы выходных усилителей соединены с вторым выходом блока местного управления и одними из входов формирователей сигналов считывания, другие входы числового регистра подключены соответственно к выходам входных усилителей и к третьему выходу блока местного управления, четвертый выход и первый вход которого соединены соответственно с входом и первым выходом адресного регистра, второй выход которого, выходы формирователей сигналов записи и другие входы формирователей сигналов считывания являются соответственно адресным выходом, выходами записи и входами считывания устройства, информационными входами и выходами которого являются соответственно другие входы входных усилителей и выходы выходных усилителей, первый выход, выходы с пятого по восьмой и второй и третий входы блока местного управления являются управляюндими выходами и одними из управляющих входов устройства, отличающееся тем, что, с целью повышения достоверности контроля, устройство содержит регистр команд, элементы неравнозначности и элементы И, выходы которых подключены к одним из входов числового регистра, а входы соединены соответственно с выходами элементов неравнозначности и с первым выходом регистра команд, второй выход которого подключен к первому входу элементов неравнозначности, второй вход которых соединен с третьим выходом адресного регистра, третий выход и одни из входов регистра команд подключены соответственно к четвертому входу блока местного управления и к другим входам

входных усилителей, другой вход регистра команд является другим управляющим входом устройства.

2. Устройство по п. 1, отличающееся тем, что блок местного управления содержит регистр операции, схему сравнения и дополнительные элементы И, причем первые входы первого и второго дополнительных элементов И подключены соответственно к первому и второму выходам регистра операции, третий выход которого соединен с первым входом третьего дополнительного элемента И, а четвертый выход - с первыми входами четвертого и пятого дополнительных элементов И, вторые входы которых подключены к первому входу схемы сравнения, выходы которой соединены соответственно с вторыми входами первого, второго и третьего дополнительных элементов И, второй вход схемы сравнения, первый и второй входы регистра операции и первый вход схемы сравнения являются соответственно входами с первого по четвертый блока, выходами которого с первого по восьмой являются соответственно выходы четвертого и пятого дополнительных элементов И, пятый выход регистра операции, выход третьего дополнительного элемента И, щестой выход регистра операции, выход первого и второго дополнительных элементов И и седьмой выход регистра операции.

Источники информации, принятые во внимание при экспертизе

1.Журавлев Ю. П., Акиньшина Ю. С. Системное проектирование памяти ЦВМ, М «Советское радио, 1976, с. 267, 275.

2.Журавлев Ю. П., Котелюк Л. А., Циклинский Н. И. Надежность и контро ЭВМ. М., «Советское радио, 1978, с. 199- 206 (прототип). / 7 /6Г7Г8792

-

-И

26

хя

2Ь 29

JO

Л

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Устройство для контроля ввода-вывода | 1980 |

|

SU896626A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство для ввода информации | 1987 |

|

SU1529208A1 |

| Устройство для вывода информации | 1984 |

|

SU1180876A1 |

Авторы

Даты

1982-09-07—Публикация

1981-01-12—Подача