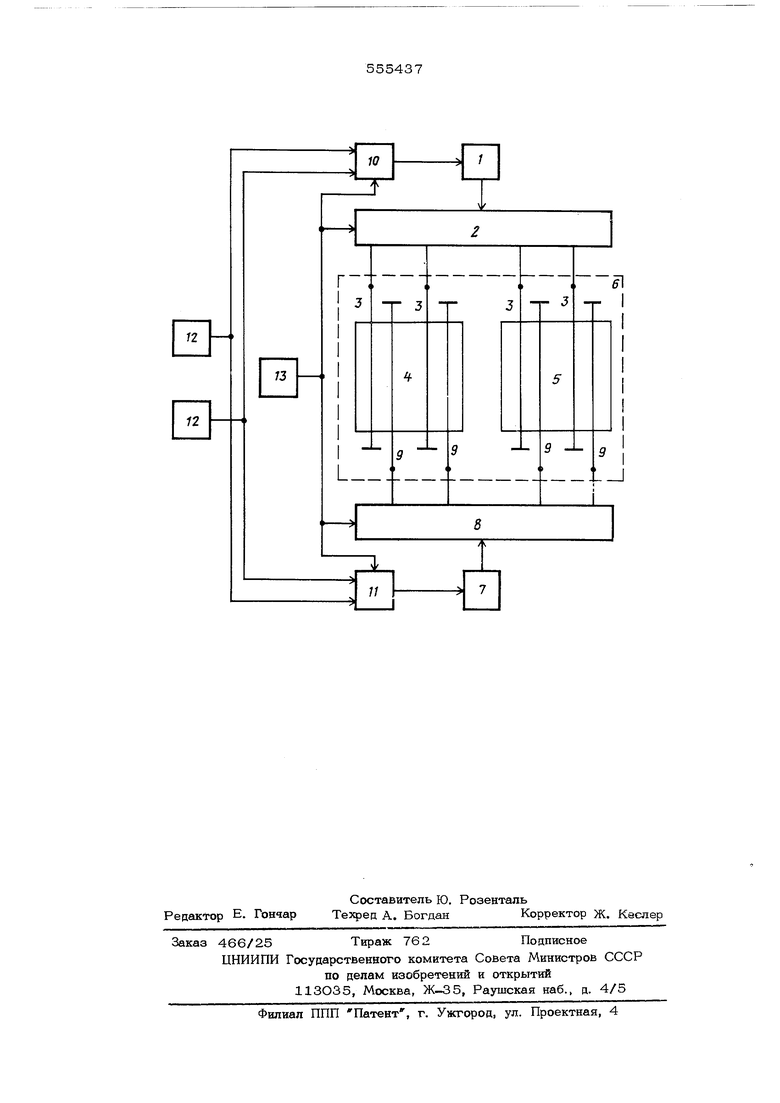

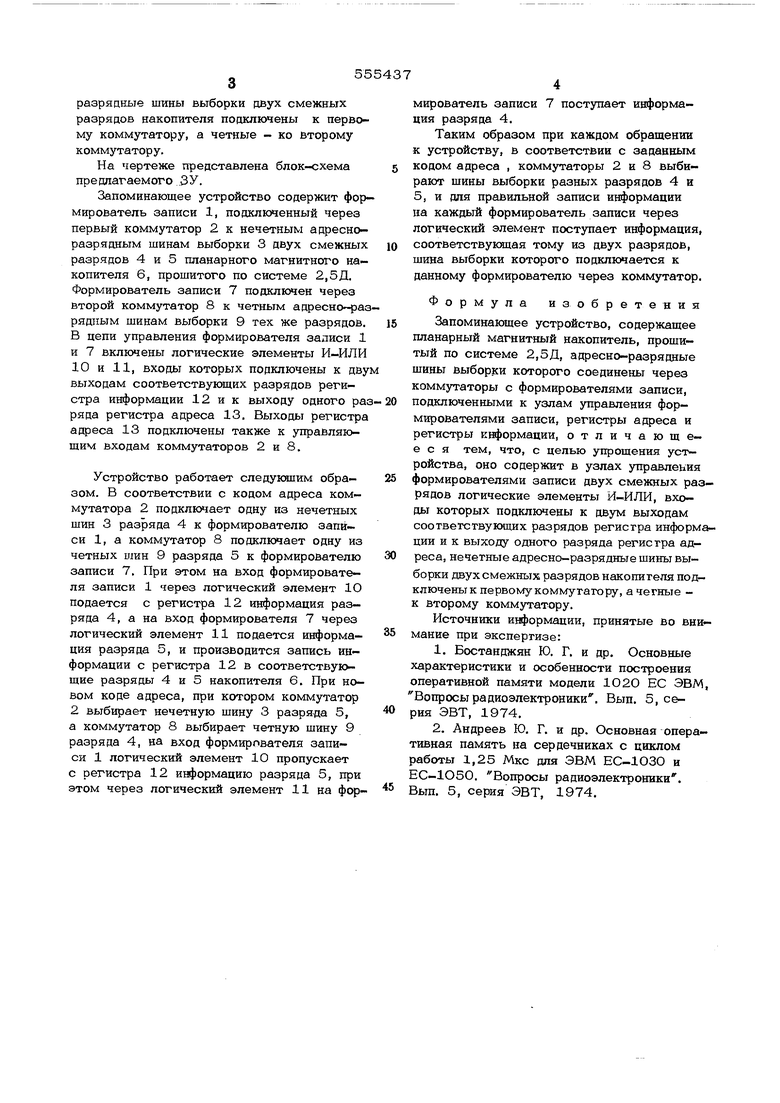

разрядные шины выборки двух смежных разрядов накопителя подключены к первому коммутатору, а четные - ко второму коммутатору. На чертеже представлена блок-схема предлагаемого .ЗУ. Запоминающее устройство содержит фор мирователь записи 1, подключенный через первый коммутатор 2 к нечетным адресноразрядным шинам выборки 3 двух смежных разрядов 4 и 5 планарного магнитнот о накопителя 6, прошитого по системе 2,5Д. Формирователь записи 7 подключен через второй коммутатор 8 к четным адресно-раз рядным шинам выборки 9 тех же разрядов. В цепи управления формирователя записи 1 и 7 включены логические элементы И-ИЛИ 10 и 11, входы которых подключены к дву выходам соответствующих разрядов регистра информации 12 и к выходу одного ра ряда регистра адреса 13, Выходы регистра адреса 13 подключены также к управляющим входам коммутаторов 2 и 8. Устройство работает следуклним образом. В соответствии с кодом адреса коммутатора 2 подключает одну из нечетных шин 3 разряда 4 к формирователю записи 1, а коммутатор 8 подключает одну из четных шин 9 разряда 5 к формирователю записи 7. При этом на вход формирователя записи 1 через логический элемент Ю подается с регистра 12 информация разряда 4, а на вход формирователя 7 через логический элемент 11 подается информация разряда 5, и производится запись информации с регистра 12 в соответствующие разряды 4 и 5 накопителя 6, При новом коде адреса, при котором коммутатор 2 выбирает нечетную шину 3 разряда 5, а коммутатор 8 выбирает четную шину 9 разряда 4, на вход формирователя записи 1 логический элемент 10 пропускает с регистра 12 информацию разряда 5, при этом через логический элемент 11 на формирователь записи 7 поступает информация разряда 4. Таким образом при каждом обращении к устройству, в соответствии с заданным кодом адреса , коммутаторы 2 и 8 выбирают щины выборки разных разрядов 4 и 5, и для правильной записи информации на каждый формирователь записи через логический элемент поступает информация, соответствующая тому из двух разрядов, шина выборки которого подключается к данному формирователю через коммутатор. Формула изобретения Запоминающее устройство, содержащее планарный магнитный накопитель, прошитый по системе 2,5Д, адресно-разрядные шины выборки которого соединены через коммутаторы с формирователями записи, подключенными к узлам управления формирователями записи, регистры адреса и регистры информации, отличающееся тем, что, с целью упрощения устройства, оно содержит в узлах управления формирователями записи двух смежных разрядов логические элементы И-ИЛИ, входы которых подключены к двум выходам соответствующих разрядов регистра информации и к выходу одного разряда регистра адреса. Нечетные адресно-разрядные шины выборки двух смежных разрядов накопителя подключены к первому коммутатору, а чегные к второму коммутатору. Источники информации, принятые во внимание при экспертизе: 1,Бостанджян Ю. Г. и др. Основные характеристики и особенности построения оперативной памяти модели 1О2О ЕС ЭВМ, Вопросы радиоэлектроники. Вып. 5, серия ЭВТ, 1974. 2.Андреев Ю. Г. и др. Основная оперативная память на сердечниках с циклом работы 1,25 Мкс для ЭВМ ЕС-1ОЗО и ЕС-1О50. Вопросы радиоэлектроники. Вып. 5, серия ЭВТ, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство типа 2,5 д | 1976 |

|

SU607278A1 |

| Магнитное запоминающее устройство | 1974 |

|

SU532132A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Накопитель для магнитного запоминающего устройства | 1976 |

|

SU588834A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU368605A1 |

| Запоминающее устройство типа 2,5 д | 1981 |

|

SU999105A1 |

| Многоуровневое запоминающее устройство | 1974 |

|

SU519759A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

Авторы

Даты

1977-04-25—Публикация

1974-12-30—Подача