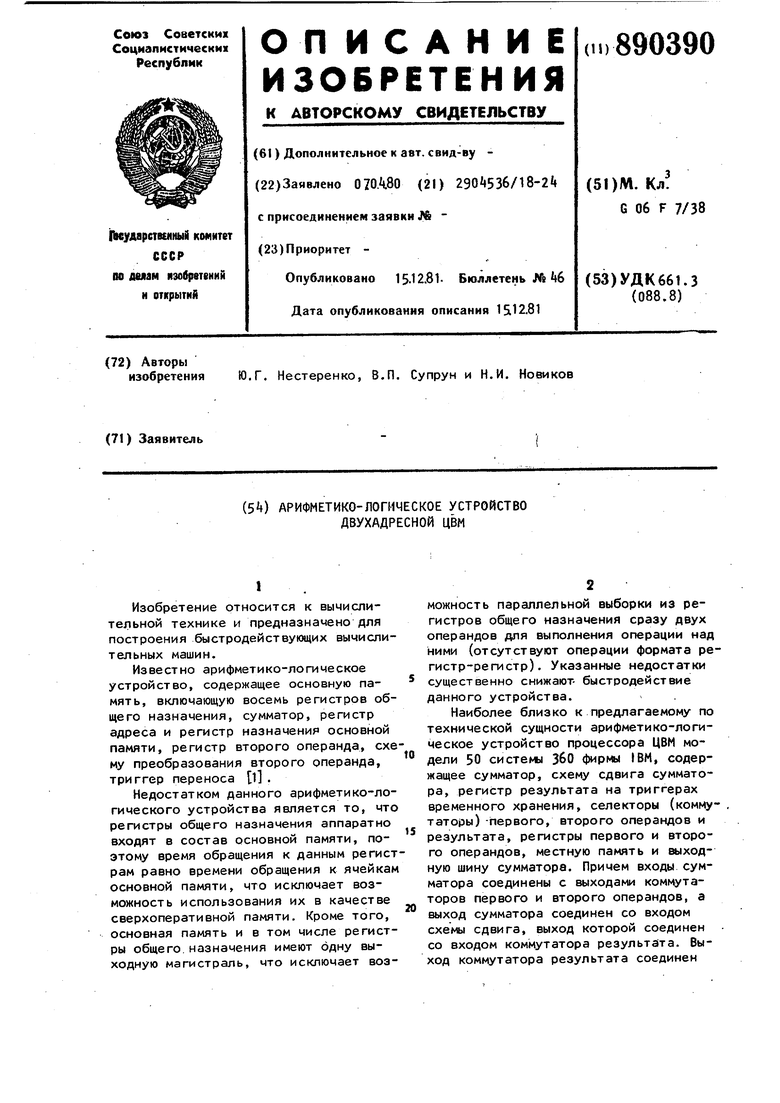

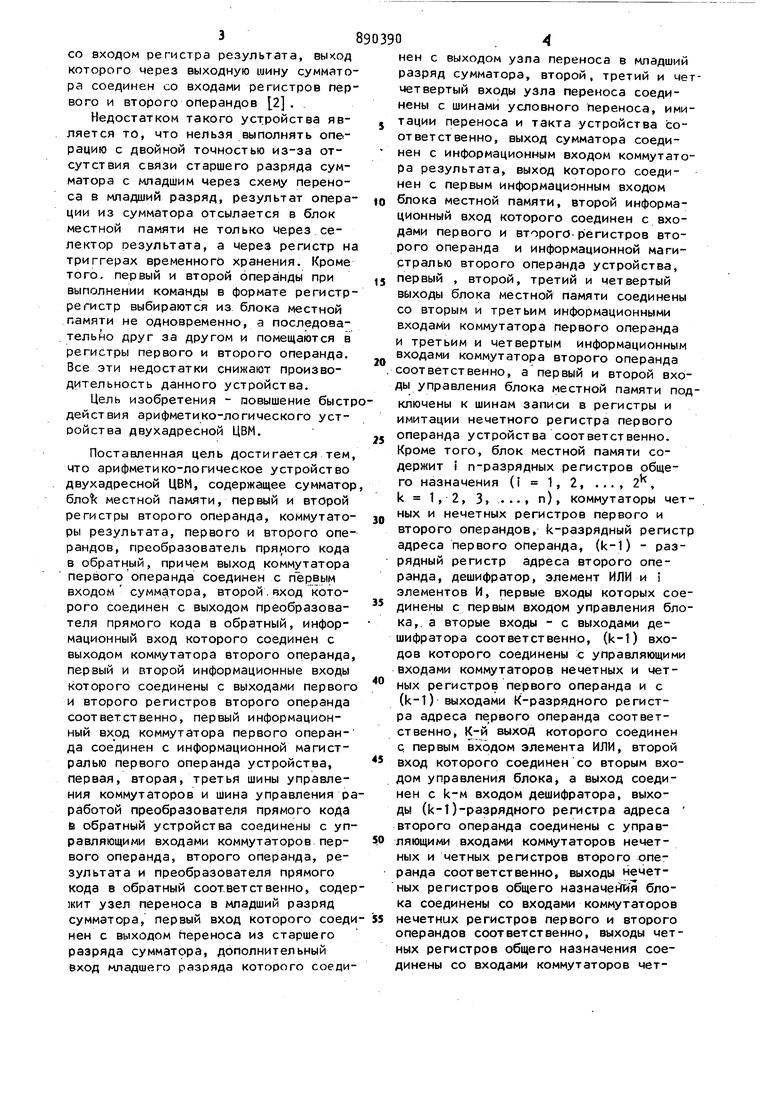

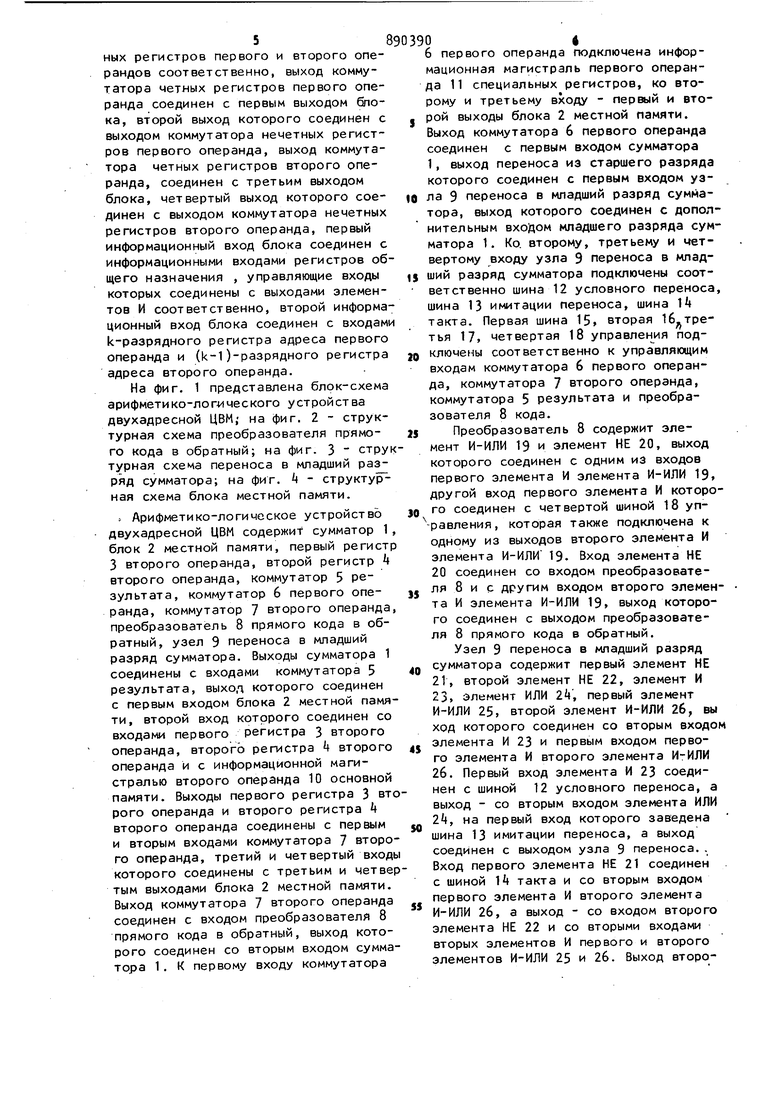

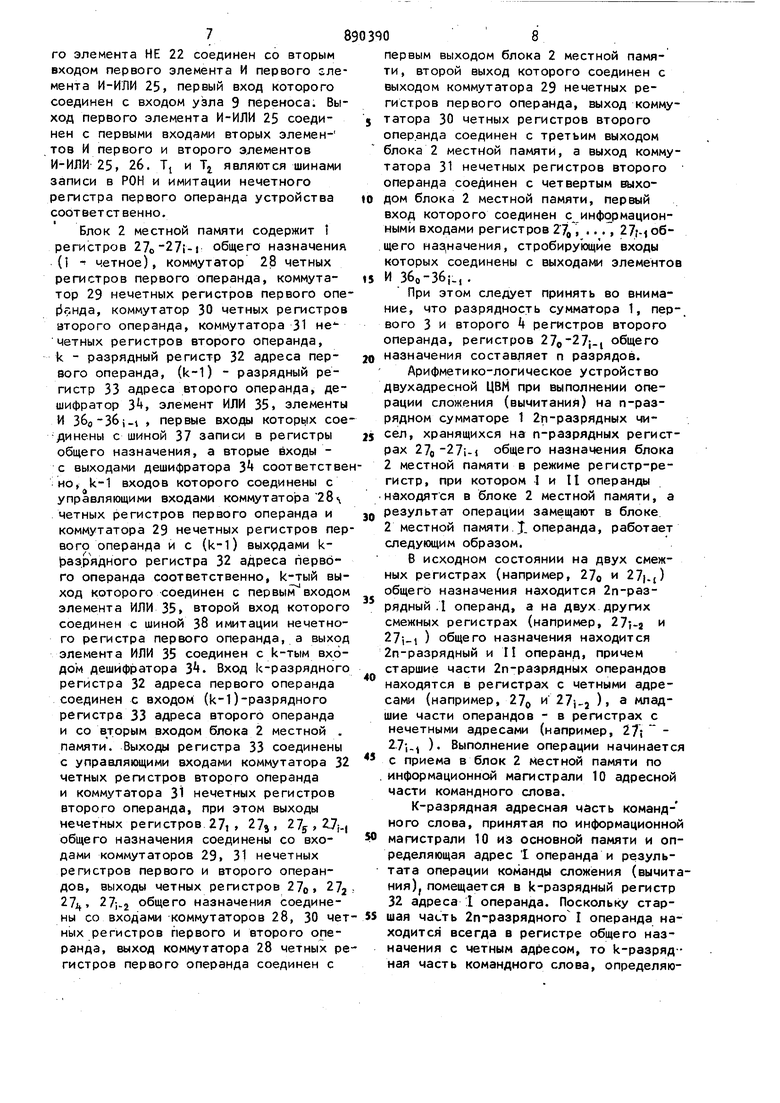

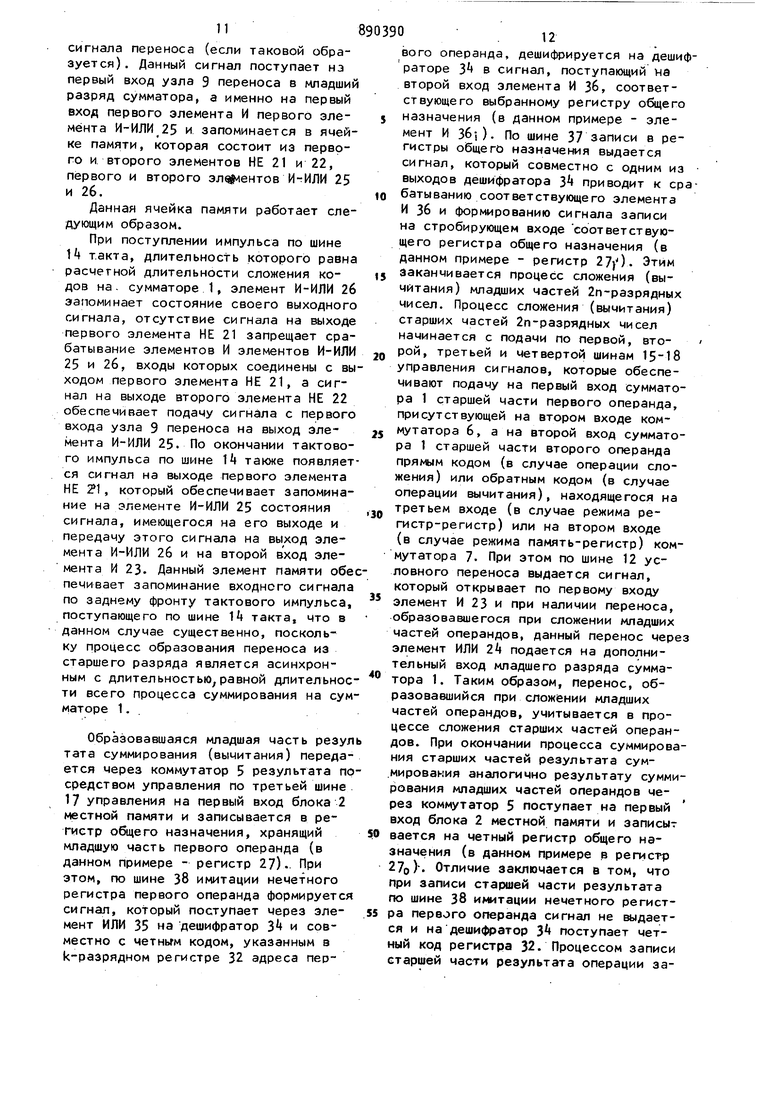

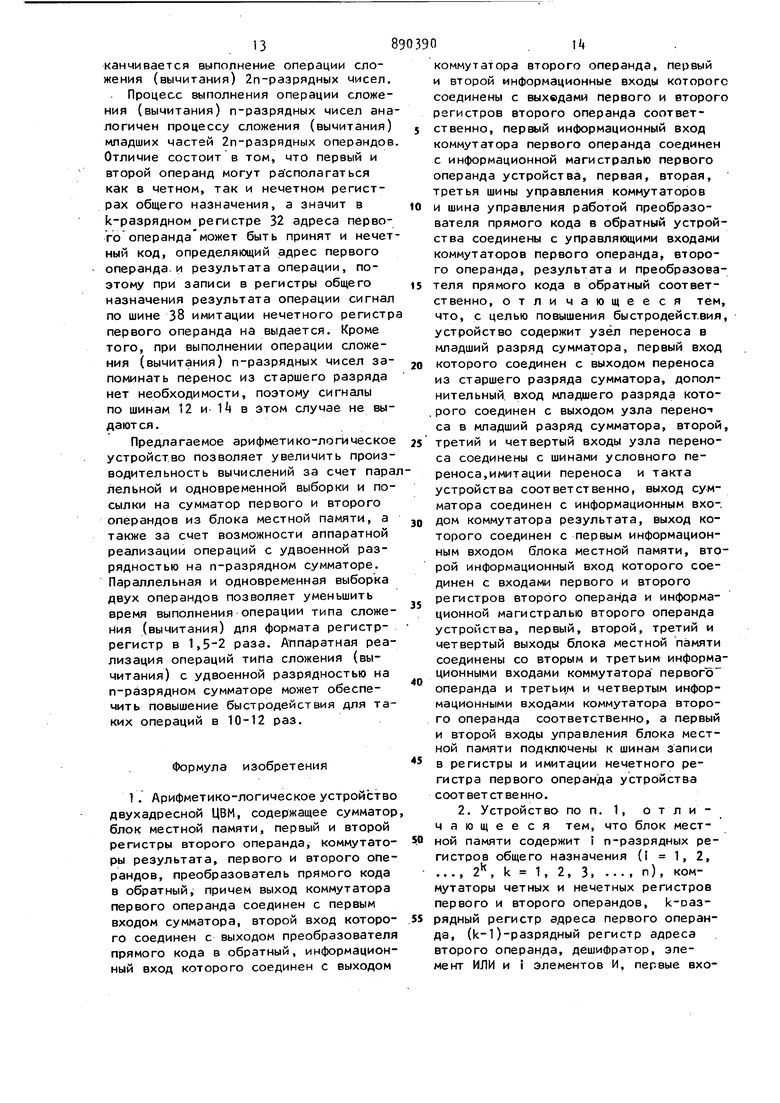

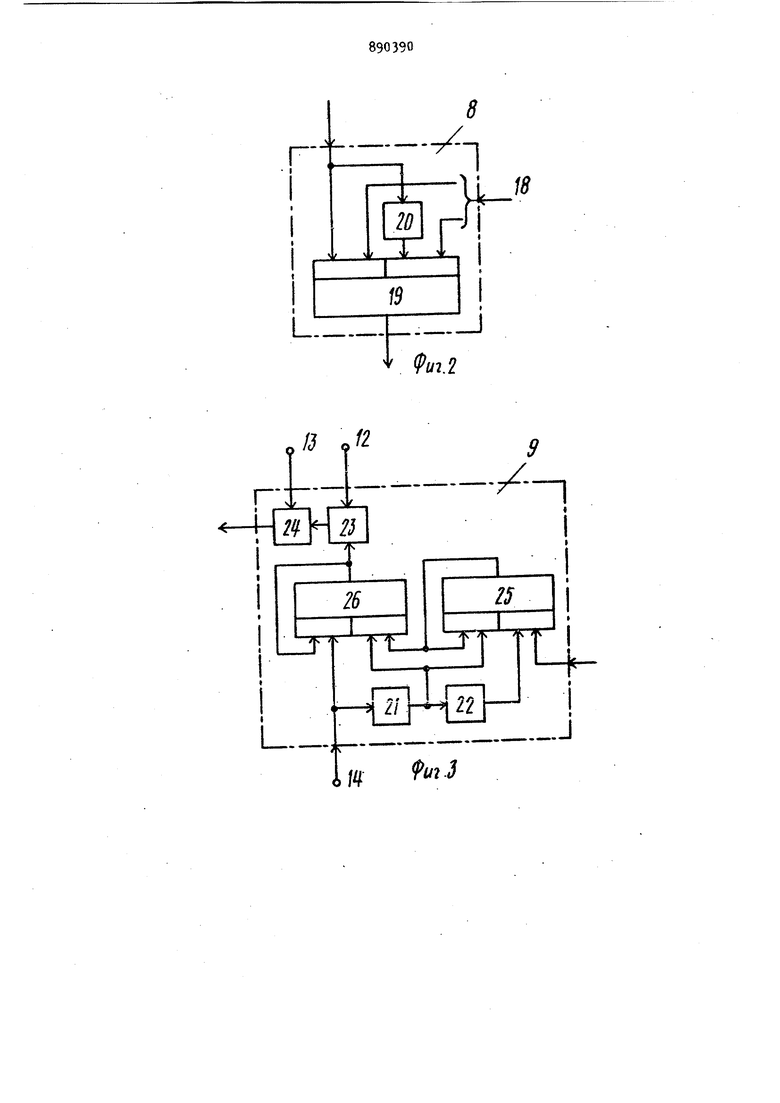

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих вычислительных машин. Известно арифметико-логическое устройство, содержащее основную память, включающую восемь регистров общего назначения, сумматор, регистр адреса и регистр назначения основной памяти, регистр второго операнда, схе му преобразования второго операнда, триггер переноса ll . Недостатком данного арифметико-логического устройства является то, что регистры общего назначения аппаратно входят в состав основной памяти, поэтому время обращения к данным регист рам равно времени обращения к ячейкам основной памяти, что исключает возможность использования их в качестве сверхоперативной памяти. Кроме того, основная память и в том числе регистры общего назначения имеют одну выходную магистраль, что исключает возможность параллельной выборки из регистров общего назначения сразу двух операндов для выполнения операции над ними (отсутствуют операции формата регистр-регистр). Указанные недостатки существенно снижают- быстродействие данного устройства. Наиболее близко к предлагаемому по технической сущности арифметико-логическое устройство процессора ЦВМ модели 50 системы ЗбО фирмы IBM, содержащее сумматор, схему сдвига сумматора, регистр результата на триггерах временного хранения, селекторы (коммутаторы) -первого, второго операндов и результата, регистры первого и второго операндов, местную память и выходную шину сумматора. Причем входы сумматора соединены с выходами коммутаторов первого и второго операндов, а выход сумматора соединен со входом схемы сдвига, выход которой соединен со входом коммутатора результата. Выход коммутатора результата соединен 3 со входом регистра результата, выход которого через выходную шину сумматора соединен со входами регистров первого и второго операндов 2 . . Недостатком такого устройства является то, что нельзя выполнять операцию с двойной точностью из-за отсутствия связи старшего разряда сумматора с младшим через схему переноса в младший разряд, результат операции из сумматора отсылается в блок местной памяти не только через.селектор результата, а через регистр на триггерах временного хранения. Кроме того, первый и второй операнды при выполнении команды в формате регистррегистр выбираются из блока местной памяти не одновременно, а последовательно друг за другом и помещаются в регистры первого и второго операнда. Все эти недостатки снижают производительность данного устройства. Цель изобретения - повышение быстр действия арифметико-логического устройства двухадресной ЦВМ. Поставленная цель достигается тем, что арифметико-логическое устройство двухадресной ЦВМ, содержащее сумматор бло местной памяти, первый и второй регистры второго операнда, коммутаторы результата, первого и второго операндов, преобразователь прямого кода в обратный, причем выход коммутатора первого операнда соединен с первым входом сумматора, второй.вход которого соединен с выходом преобразователя прямого кода в обратный, информационный вход которого соединен с выходом коммутатора второго операнда первый и второй информационные входы которого соединены с выходами первого и второго регистров второго операнда соответственно, первый информационный вход коммутатора первого операнда соединен с информационной магистралью первого операнда устройства, первая, вторая, третья шины управления коммутаторов и шина управления р работой преобразователя прямого кода fit обратный устройства соединены с уп равляющими входами коммутаторов первого операнда, второго операнда, результата и преобразователя прямого кода 8 обратный соответственно, соде жит узел переноса в младший разряд сумматора, первый вход которого соед нен с выходом переноса из старшего разряда сумматрра, дополнительный вход младшего разряда которого соеди нен с выходом узла переноса в младший разряд сумматора, второй, третий и четчет вертый входы узла переноса соединены с шинами условного переноса, имитации переноса и такта устройства соответственно, выход сумматора соединен с информационным входом коммутатора результата, выход которого соединен с первым информационным входом блока местной памяти, второй информационный вход которого соединен с входами первого и второго pieгистров второго операнда и информационной магистралью второго операнда устройства, первый , второй, третий и четвертый выходы блока местной памяти соединены со вторым и третьим информационными входами коммутатора первого операнда и третьим и четвертым информационным входами коммутатора второго операнда соответственно, апервый и второй входы управления блока местной памяти подключены к шинам записи в регистры и имитации нечетного регистра первого операнда устройства соответственно. Кроме того, блок местной памяти содержит i п-разрядных регистров общего назначения (i 1, 2, ..., 2, k 1,2, 3, .... п), коммутаторы четных и нечетных регистров первого и второго операндов, k-разрядный регистр адреса первого операнда, (k-l) - разрядный регистр адреса второго операнда, дешифратор, элемент ИЛИ и i элементов И, первые входы которых соединены с первым входом управления блока, а вторые входы - с выходами дешифратора соответственно, (k-1) входов которого соединены с управляющими входами коммутаторов нечетных и четных регистров первого операнда и с (k-l) выходами К-разрядного регистра адреса первого операнда соответственно, К-й выход которого соединен С первым входом элемента ИЛИ, второй вход которого соединен со вторым входом управления блока, а выход соединен с k-M входом дешифратора, выходы (k-т)-разрядного регистра адреса второго операнда соединены с управляющими входами коммутаторов нечетных и четных регистров второго операнда соответственно, выходы нечетных регистров общего назначеййя блока соединены со входами коммутаторов нечетных регистров первого и второго операндов соответственно, выходы четных регистров общего назначения соединены со входами коммутаторов чет58ных регистров первого и второго операндов соответственно, выход коммутатора четных регистров первого операнда соединен с первым выходом блока, второй выход которого соединен с выходом коммутатора нечетных регистров первого операнда, выход коммутатора четных регистров второго операнда, соединен с третьим выходом блока, четвертый выход которого соединен с выходом коммутатора нечетных регистров второго операнда, первый информационный вход блока соединен с информационными входами регистров общего назначения , управляющие входы которых соединены с выходами элементов И соответственно, второй информационный вход блока соединен с входами k-разрядного регистра адреса первого операнда и (k-1)-разрядного регистра адреса второго операнда. На фиг. 1 представлена блок-схема арифметико-логического устройства двухадресной ЦВМ; на фиг. 2 - структурная схема преобразователя прямого кода в обратный; на фиг. 3 - струк турная схема переноса в младший разряд сумматора; на фиг. - структур ная схема блока местной памяти. Арифметико-логическое устройство двухадресной ЦВМ содержит сумматор 1 блок 2 местной памяти, первый регистр 3 второго операнда, второй регистр k второго операнда, коммутатор 5 результата, коммутатор 6 первого операнда, коммутатор 7 второго операнда, преобразователь 8 прямого кода в обратный, узел 9 переноса в младший разряд сумматора. Выходы сумматора 1 соединены с входами коммутатора 5 результата, выход которого соединен с первым входом блока 2 местной памяти, второй вход которого соединен со входами первого регистра 3 второго операнда, второго регистра k второго операнда и с информационной магистралью второго операнда 10 основной памяти. Выходы первого регистра 3 вто рого операнда и второго регистра Ц второго операнда соединены с первым и вторым входами коммутатора 7 второго операнда, третий и четвертый входы которого соединены с третьим и четвер тым выходами блока 2 местной памяти. Выход коммутатора 7 второго операнда соединен с входом преобразователя 8 прямого кода в обратный, выход которого соединен со вторым входом сумматора 1. К первому входу коммутатора 0 6 первого операнда подключена информационная магистраль первого операнда 11 специальных регистров, ко второму и третьему входу - первый и второй выходы блока 2 местной памяти. Выход коммутатора 6 первого операнда соединен с первым входом сумматора 1, выход переноса из старшего разряда которого соединен с первым входом узла 9 переноса в младший разряд сумматора, выход которого соединен с дополнительным входом младшего разряда сумматора 1. Ко. второму, третьему и четвертому входу узла 9 переноса в младший разряд сумматора подключены соответственно шина 12 условного переноса, шина 13 имитации переноса, шина k такта. Первая шина 15, вторая 16.третья 17, четвертая 18 управления подключены соответственно к управляющим входам коммутатора 6 первого операнда, коммутатора 7 второго операнда, коммутатора 5 результата и преобразователя 8 кода. Преобразователь 8 содержит элемент И-ИЛИ 19 и элемент НЕ 20, выход которого соединен с одним из входов первого элемента И элемента И-ИЛИ 19, другой вход первого элемента И которого соединен с четвертой шиной 18 управления, которая также подключена к одному из выходов второго элемента И элемента И-ИЛИ 19. Вход элемента НЕ 20 соединен со входом преобразователя 8 и с другим входом второго элемента И элемента И-ИЛИ 19, выход которого соединен с выходом преобразователя 8 прямого кода в обратный. Узел 9 переноса в младший разряд сумматора содержит первый элемент НЕ 21, второй элемент НЕ 22, элемент И 23, элемент ИЛИ 2, первый элемент И-ИЛИ 25, второй элемент И-ИЛИ 2б, вы ход которого соединен со вторым входом элемента И 23 и первым входом первого элемента И второго элемента И-ИЛИ 2б. Первый вход элемента И 23 соединен с шиной 12 условного переноса, а выход - со вторым входом элемента ИЛИ 2k, на первый вход которого заведена шина 13 имитации переноса, а выход соединен с выходом узла 9 переноса., Вход первого элемента НЕ 21 соединен с шиной 1 такта и со вторым входом первого элемента И второго элемента И-ИЛИ 2б, а выход - со входом второго элемента НЕ 22 и со вторыми входами вторых элементов И первого и второго элементов И-ИЛИ 25 и 2б. Выход второго элемента НЕ 22 соединен со вторым входом первого элемента И первого элемента И-ИЛИ 25, первый вход которого соединен с входом узла 9 переноса. Выход первого элемента И-ИЛИ 25 соединен с первыми входами вторых элементов И первого и второго элементов И-ИЛИ 25 26. Tj и Tj являются шинами записи в РОН и имитации нечетного регистра первого операнда устройства соответственно. Блок 2 местной памяти содержит регистров 27o 27i-i общего назначения (i четное), коммутатор 28 четных регистров первого операнда, коммутатор 29 нечетных регистров первого опе (Злнда, коммутатор 30 четных регистров аторого операнда, коммутатора 31 нечетных регистров второго операнда, k - разрядный регистр 32 адреса первого операнда, (k-1) - разрядный регистр 33 адреса второго операнда, дешифратор 3, элемент ИЛИ 35, элементы И Збо-3б)1 , первые входы которых сое динены с шиной 37 записи в регистры общего назначения, а вторые входы с выходами дешифратора 3 соответстве но, k-1 входов которого соединены с управляющими входами коммутатора 2В четных регистров первого операнда и коммутатора 29 нечетных регистров пер вого операнда и с (k-l) выхрдами k|эазрядного регистра 32 адреса первого операнда соответственно, k-тый выход которого соединен с первым входом элемента ИЛИ 35, второй вход которого соединен с шиной 38 имитации нечетного регистра первого операнда, а выход элемента ИЛИ 35 соединен с k-тым входом дешифратора Вход k-раз рядно го регистра 32 адреса первого операнда соединен с входом (k-1)-разрядного регистра 33 адреса второго операнда и со вторым входом блока 2 местной . памяти. Выходы регистра 33 соединены с управляющими входами коммутатора 32 четных регистров второго операнда и коммутатора 31 нечетных регистров второго операнда, при этом выходы нечетных регистров 27i , 275, 27 27;.| общего назначения соединены со входами коммутаторов 29, 31 нечетных регистров первого и второго операндов, выходы четных регистров 27о, 272 27i, 27;.2 общего назначения соединены со входами коммутаторов 28, 30 чет ных регистров первого и второго oneранда, выход коммутатора 28 четных ре гистров первого операнда соединен с первым выходом блока 2 местной памяти, второй выход которого соединен с выходом коммутатора 29 нечетных регистров первого операнда, выход коммутатора 30 четных регистров второго операнда соединен с третьим выходом блока 2 местной памяти, а выход коммутатора 31 нечетных регистров второго операнда соединен с четвертым выходом блока 2 местной памяти, первый вход которого соединен с информационными входами регистров 27о , ... , 27; общего назначения, стробирующие входы которых соединены с выходами элементов И 36o-36i.,. При этом следует принять во внимание, что разрядность сумматора 1, первого 3 и второго регистров второго операнда, регистров 27o 27j-i общего назначения составляет п разрядов. Арифметико-логическое устройство двухадресной ЦВМ при выполнении операции сложения (вычитания) на п-разрядном сумматоре 1 2п-разрядных чисел, хранящихся на п-разрядных регистрах 27о 27i-i общего назначения блока 2 местной памяти в режиме регистр-регистр, при котором 4 и П операнды находятся в блоке 2 местной памяти, а результат операции замещают в блоке 2 местной памяти J. операнда, работает следующим образом. В исходном состоянии на двух смежных регистрах (например, 27о и 27).() общегй назначения находится 2п-разрядный .1 операнд, а на двух других смежных регистрах (например, 27ьг и 27,1 ) общего назначения находится 2п-разрядный и II операнд, причем старшие части 2п-разрядных операндов находятся в регистрах с четными адресами (например, 27о и ), а младшие части операндов - в регистрах с нечетными адресами (например, 27} 27,. ). Выполнение операции начинается с приема в блок 2 Местной памяти по информационной магистрали 10 адресной части командного слова. К-разрядная адресная чисть командного слова, принятая по информационной магистрали 10 из основной памяти и определяющая адрес X операнда и результата операции команды сложения (вычитания), помещается в k-разрядный регистр 32 адреса 1 операнда. Поскольку старшая часть 2п-разрядного I операнда находится всегда в регистре общего назначения с четным адресом, то k-разряд-ная часть командного слова, определяющая адрес 1 операнда и результата 2празрядной операции всегда .имеет четный код. (К-1)-разрядная адресная часть ко мандного слова, определяющая адрес I операнда помещается в (k-l) разрядный регистр 33 адреса II операнда. Поскольку управляющие входы коммутаторов 28-31 нечетных и четных регистров первого и второго операндов связаны только с k-1 выходами регистров 32 и 33 адреса I и И операнда (без учета младшего разряда), то од-новременно на выходе коммутатора 28 четных регистров первого операнда и коммутатора 29 нечетных регистров первого операнда будут присутствоват старшая и младшая части, соответственно, 2п-разрядного Т операнда, а на выходе.коммутатора 30 и на выхо де коммутатора 31 будут присутствовать старшая и младшая части, соответственно, 2п-разрядного II операнда. Если операция сложения (вычитания выполняется не в режиме регистр-регистр, а в режиме память-регистр, т.е. И операнд выбирается не из блока 2 местной памяти, а из основной па мяти, то старшая и младшая части 2празрядного II операнда в Начале операции принимаются по информационной магистрали 10 из основной памяти и помещаются в первый 3 и второй k регистры второго операнда. .Таким образом, перед выполнением непосредственно сложения (вычитания) на сумматоре 1 старшая и младшая части 2п-разрядного Т операнда находятся на первом и втором выходе местной памяти, а значит и на втором и третьем входам коммутатора 6 первого операнда, старшая и младшая части 2п-. разрядного И операнда находятся на третьем к четвертом (в случае режима регистр-регистр) или на первом и втором (в случае режима память-регистр) входах коммутатора 7 второго операнда На- первом входе коммутатора 6 присутствует информация специальных регистров, поступающая по информационной ма . гистрали 11 и служащая для выполнени операцйй с содержимым специальных регистров. Выполнение операции сложения (вычитания) 2п-разрядных чисел начинается со сложения (вычитания) младших частей этих чисел. При этом по первой шине 15 управления в коммутатор 6 поступает код, который осуществляет под ключение к выходу коммутатора 6 информации, присутствующей на третьем входе коммутатору 6, т.е. младшую часть 1 операнда. По второй шине 16 управления в коммутатор 7 поступает код, который осуществляет подключение к выходу коммутатора 7 информации, присутствующей на четвертом входе коммутатора 7, если операция сложения (вычитания) выполняется в режиме регистр-регистр. Если операция сложения (вычитания) выполняется в режиме память-регистр, то по второй шине 16 управления поступает код, который осуществляет подключение к выходу коммутатора 7 информации второго регистра второго операнда, присутствующей на втором входе коммутатора 7Младшая часть первого операнда из коммутатора 7 передается на первый вход сумматора 1, а при поступлении управляющего кода по четвертой шине 18 управления младшая часть второго ., операнда из коммутатора 7 передается на второй вход сумматора 1 прямым кодом через элемент И-ИЛИ 19 (при выполнении операции сложения) или обратным кодом через элемент НЕ 20 и элемент И-ИЛИ 19 (при выполнении операции вычитания). При выполнении операции сложения данная операция сводится к суммированию на сумматоре 1 кода первого операнда с Дополнительным кодом второго операнда. Аппаратно данный процесс реализуется путем сложения кода первого операнда с обратным кодом второго операнда и прибавлением в сумматоре 1 к данной сумме единицы младшего разряда, подаваемой на дополнительный вход младшего разряда сумматора 1 с выхода узла 9 переноса в младший разряд сумматора. Данный сигнал формируется на элементе ИЛИ Z путем подачи управляющего сигнала по шине 13 имитации переноса. При выполнении операции сложения по шине 13 имитации переноса данный сигнал не формируется и единица младшего разряда на дополнительный вход младшего разряда сумматора не подается. Дальнейший процесс выполнения операции спожения и вычитания идентичен. Процесс сложения двух кодов младших частей 2 -разрядных операндов на сумматоре 1 заканчивается формированием на выходе сумматора 1, а следовательно, и- на выходе коммутатора 5 результата, суммирования, а также на выходе переноса из старшего разряда сумматора 118 сигнала переноса (если таковой образуется). Данный сигнал поступает на первый вход узла 9 переноса в младший разряд сумматора, а именно на первый вход первого элемента И первого элемента И-ИЛИ 25 и запоминается в ячейке памяти, которая состоит из первого и второго элементов НЕ 21 и 22, первого и второго эле Иентов И-ИЛИ 25 и 26. Данная ячейка памяти работает следующим образом. При поступлении импульса по шине 1 такта, длительность которого равна расчетной длительности сложения кодов на. сумматоре 1, элемент И-ИЛИ 2б запоминает состояние своего выходного сигнала, отсутствие сигнала на выходе первого элемента НЕ 21 запрещает срабатывание элементов И элементов И-ИЛИ 25 и 26, входы которых соединены с вы ходом первого элемента НЕ 21, а сигнал на выходе второго элемента НЕ 22 обеспечивает подачу сигнала с первого входа узла 9 переноса на выход элемента И-ИЛИ 25. По окончании тактового импульса по шине также появляет ся сигнал на выходе первого элемента НЕ , который обеспечивает запоминание на элементе И-ИЛИ 25 состояния сигнала, имеющегося на его выходе и передачу этого сигнала на выход элемента И-ИЛИ 2б и на второй вход элемента И 23. Данный элемент памяти обе печивает запоминание входного сигнала по заднему фронту тактового импульса, поступающего по шине Т такта, что в данном случае существенно, поскольку процесс образования переноса из старшего разряда является асинхронным с длительностью,равной длительнос ти всего процесса суммирования на сум маторе 1. . Образовавшаяся младшая часть резул тата суммирования (вычитания) передается через коммутатор 5 результата по средством управления по третьей шине 17 управления на первый вход блока 2 местной памяти и записывается в регистр обцего назначения, хранящий младшую часть первого операнда (в данном примере - регистр 27). При этом, по шине 38 имитации нечетного регистра первого операнда формируется сигнал, который поступает через элемент ИЛИ 35 на -дешифратор 3 и совместно с четным кодом, указанным в k-разрядном регистре 32 адреса первого операнда, дешифрируется на дешифраторе 3 в сигнал, поступающий на второй вход элемента И Зб, соответствующего выбранному регистру общего назначения (в данном примере - элемент И Зб|). По шине 37 записи в регистры общего назначения выдается сигнал, который совместно с одним из выходов дешифратора 3 приводит к срабатыванию соответствующего элемента И 36 и формированию сигнала записи на стробирующем входе соответствующего регистра общего назначения (в данном примере - регистр 27jO. Этим заканчивается процесс сложения (вычитания) младших частей 2п-разрядных чисел. Процесс сложения (вычитания) старших частей 2п-разрядных чисел начинается с подачи по первой, второй, третьей и четвертой шинам 15-18 управления сигналов, которые обеспечивают подачу на первый вход сумматора 1 старшей части первого операнда, присутствующей на втором входе коммутатора 6, а на второй вход сумматора 1 старшей части второго операнда прямым кодом (в случае операции сложения) или обратным кодом (в случае операции вычитания), находящегося на третьем входе (в случае режима регистр-регистр) или на втором входе (в случае режима память-регистр) коммутатора 7. При этом по шине 12 условного переноса выдается сигнал, который открывает по первому входу элемент И 23 и при наличии переноса, образовавшегося при сложении младших частей операндов, данный перенос через элемент ИЛИ 2k подается на дополнительный вход младшего разряда сумматора 1. Таким образом, перенос, образовавшийся при младших частей операндов, учитывается в процессе сложения старших частей операндов. При окончании процесса суммирования старших частей результата сум.мирования аналогично результату суммирования младших частей операндов через коммутатор 5 поступает на первый вход блока 2 местной памяти и записыт вается на четный регистр общего назначения (в данном примере в регистр 27о)-. Отличие заключается в том, что при записи старшей части результата по шине 38 имитации нечетного регистра первого операнда сигнал не выдается и на деши(атор 3 поступает четный код регистра 32. Процессом записи старшей части результата операции заканчивается выполнение операции сложения (вычитания) 2п-разрядных чисел. Процесс выполнения операции сложения (вычитания) п-разрядных чисел ана логичен процессу сложения (вычитания) младших частей 2п-разрядных операндов Отличие состоит в том, что первый и второй операнд могут располагаться как в четном, так и нечетном регистрах общего назначения, а значит в k-разрядном регистре 32 адреса первого операнда может быть принят и нечет ный код, определяющий адрес первого операнда.и результата операции, поэтому при записи в регистры общего назначения результата операции сигнал по шине 38 имитации нечетного регистр первого операнда на выдается. Кроме того, при выполнении операции сложения (вычитания) п-разрядных чисел запоминать перенос из старшего разряда нет необходимости, поэтому сигналы по шинам 12 и- в этом случае не выдаются. Предлагаемое арифметико-логическое устройство позволяет увеличить производительность вычислений за счет пара лельной и одновременной выборки и посылки на сумматор первого и второго операндов из блока местной памяти, а также за счет возможности аппаратной реализации операций с удвоенной разрядностью на п-разрядном сумматоре. Параллельная и одновременная выборка двух операндов позволяет уменьшить время выполнения операции типа сложения (вычитания) для формата регистррегистр в 1,5-2 раза. Аппаратная реализация операций типа сложения (вычитания) с удвоенной разрядностью на п-разрядном сумматоре может обеспечить повышение быстродействия для таких операций в 10-12 раз. Формула изобретения 1. Арифметико-логическое устройство двухадресной ЦВМ, содержащее сумматор блок местной памяти, первый и второй регистры второго операнда, коммутаторы результата, первого и второго операндов, преобразователь прямого кода в обратный, причем выход коммутатора первого операнда соединен с первым входом сумматора, второй вход которого соединен с выходом преобразователя прямого кода в обратный, информационный вход которого соединен с выходом коммутатора второго операнда, первый и второй информационные входы которого соединены с выхвдами первого и второго регистров второго операнда соответственно, первый информационный вход коммутатора первого операнда соединен с информационной магистралью первого операнда устройства, первая, вторая, третья шины управления коммутаторов и шина управления работой преобразователя прямого кода в обратный устройства соединены с управляющими входами коммутаторов первого операнда, второго операнда, результата и преобразователя прямого кода в обратный соответственно, отличающееся тем, что, с целью повышения быстродействия, устройство содержит узел переноса в младший разряд сумматора, первый вход которого соединен с выходом переноса из старшего разряда сумматора, дополнительный вход младшего разряда которого соединен с выходом узла перено- са в младший разряд сумматора, второй, третий и четвертый входы узла переноса соединены с шинами условного переноса,имитации переноса и такта устройства соответственно, выход сумматора соединен с информационным вхо-. дом коммутатора результата, выход которого соединен с первым информационным входом блока местной памяти, второй информационный вход которого соединен с входами первого и второго регистров второго операнда и информационной магистралью второго операнда устройства, первый, второй, третий и четвертый выходы блока местной памяти соединены со вторым и третьим информационными входами коммутатора первого операнда и третьим и четвертым информационными входами коммутатора второго операнда соответственно, а первый и второй входы управления блока местной памяти подключены к шинам записи в регистры и имитации нечетного регистра первого операнда устройства соответственно. 2. Устройство по п. 1, отличающееся тем, что блок местной памяти содержит i п-разрядных регистров общего назначения (,2, ..., 2, k 1, 2, 3, ..., п), коммутаторы четных и нечетных регистров первого и второго операндов, k-Da3рядный регистр адреса первого операнда, (k-1)-разрядный регистр адреса второго операнда, дешифратор, элеент ИЛИ и i элементов И, первые входы которых соединены с первым входом управления блока, а вторые входы - с выходами дешифратора соответственно, (k-1) входов которого соединены суправляющиж входами коммутаторов нечет ных и четных регистров первого oneранда и с (k-1) выходами k-разрядного регистра адреса первого операнда соответственно, k-й выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен со вторым входом управления блока, а выход соединен с k-м входом дешифратора, выходы (k-l)-paзpяднoгo регистра адреса второго операнда срединены с управляющими входами коммутаторов нечетных и четных регистров второго операнда соответственно, выходы нечетных регистров общего назначения блока соединены со входами коммутаторов нечетных регистров первого и второго операндов соответственно, выходы четных регистров общего назначения соединены со входами KOMMyTatopoB чет ных регистров первого и второго опера ндов соответственно, выход коймутатора четных регистров первого опе0.16 ранда соединен с первым выходом блока второй выход которого соединен с выходом коммутатора нечетных регистров первого операнда, выход коммутатора четных регистров второго операнда соединен с третьим выходом блока, четвертый выход которого соединен с выходом коммутатора нечетных регистров второго операнда, первый информационный вход блока соединен с информационными входами регистров общего назначения, управляющие входы которых соединены с выходами элементов И соответственно, второй информационный вход блока соединен с входами k-разрядного регистра адреса первого операнда и (k-1)-pa3рядного регистра адреса второго операнда. Источники информации, принятые во внимание при экспертизе 1.Флорес А. Организация вычислительных машин. Мир, 1972, с. рис. 11.i.l 2.Хассон С. Микропрограммное управление.Мир, вып. 2, 197, с. UA168, рис. 8.1., 8.2, 8.9 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

х/

.1

Г

8 1

18

r

I

/J

;j

26

IIЛИI

II

U7.2

1

Я З;

Г7

T1

22

ill: ui. J

Авторы

Даты

1981-12-15—Публикация

1980-04-07—Подача