1

Изобретение относится к области вычислителыной техники и предназначено для хранения И адресной выборки фиксировааной и«фо рмаци-и (микропрограмм, значений ко«стащт и табличных фувкщий и т. д.).

Известны постоянные запоминающие устройства (ПЗУ), содерл ащие числовой блок, вышолнеЕный в виде диодной .матрицы, регистр адреса, дешифратор и усилители считывания.

Одно из известных ПЗУ содержит числовой блок, выполненный в виде диодной матрицы, одни шины которого подключены к выходам дешифратора, а другие - к разделительным элементам (резисторам).

Педостатком этого ПЗУ является низкое быстродействие.

Наиболее близким техническим решением к изобретению является устройство, содержащее регистр адреса, выходы одной группы разрядов которого (подключаиы к входам дешифратора, выходы дешифратора подключены к одним швнам числового блока, выполненного в .виде диодмой матрицы, другие шины которого подключены к разделительным элементам, выходные диодные сборки, выходы которых подключены к усилителям считывания, и дополиителвные диодные сборки.

Для этого уст1роЙ1Ства характерны органичевное быстродействие, связанное с тем, что

разделительные элементы (резисторы) включены в цепь заряда-разряда паразитных емкостей всех обратно смещенных диодов числового .блока, и недостаточно высокая надежность при интегральном исполнении числового блока из-за отсутствия при нем встроенного диодно-резистивного адресного .блока, что предопределяет значительное .количество выводов из К|ристалла и соответственно излишне

большое число 1паек при сборке ПЗУ.

Цель изобретения - повышение быстродействия и надежности известного ПЗУ.

Это достигается тем, что предлагаемое устройство, содерл ащее регистр адреса, выходы

одной группы разрядов которого подключены к входам дешифратора, выходы дешифратора подключены к одним шинам числового блока, выполненного в виде диодной матрицы, другие шины KOTOpOiro подключены к разделительньш элементам, выходные диодные сборки, выходы которых подключены к усилителям считывания, и дополнительные диодные сборки, содержит в числовом блоке дополнителыную диодную матрицу, шииы которой, соединяющие катоды диодов, подключены к выходам другой группы разрядов регистра адреса, а шины, соединяющие аиоды диодов, подключены к разделительным элементам и к входам выходных и дополнительных диодных

сборок.

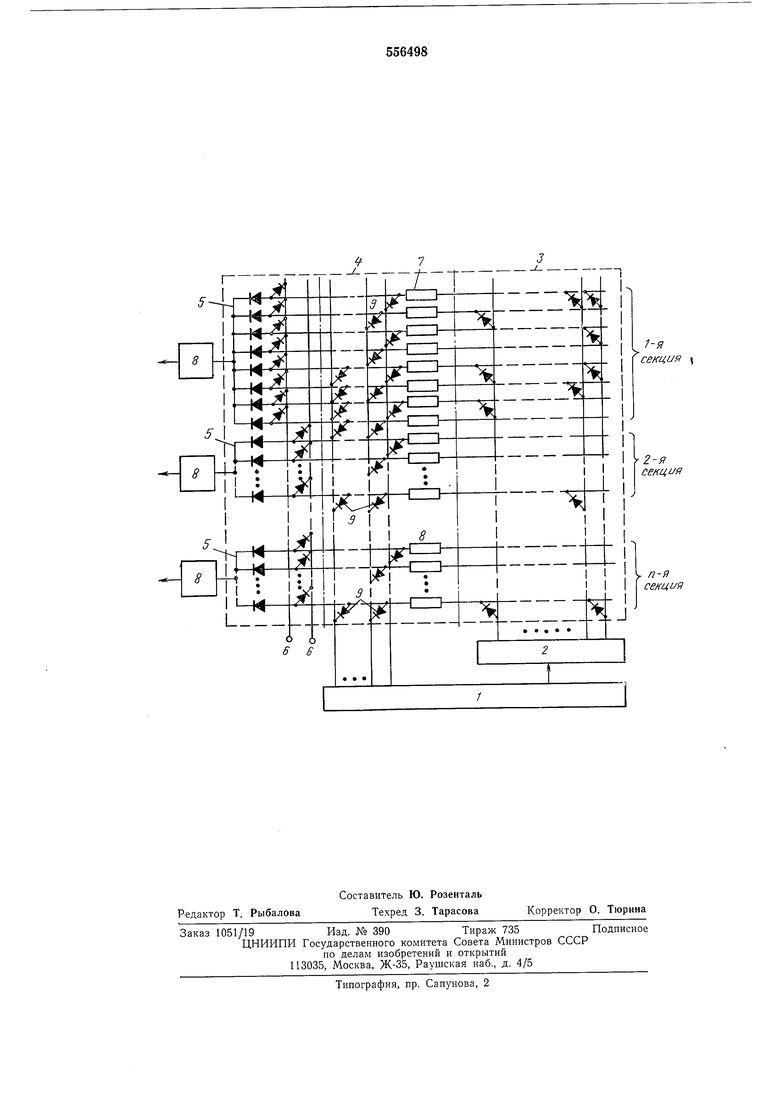

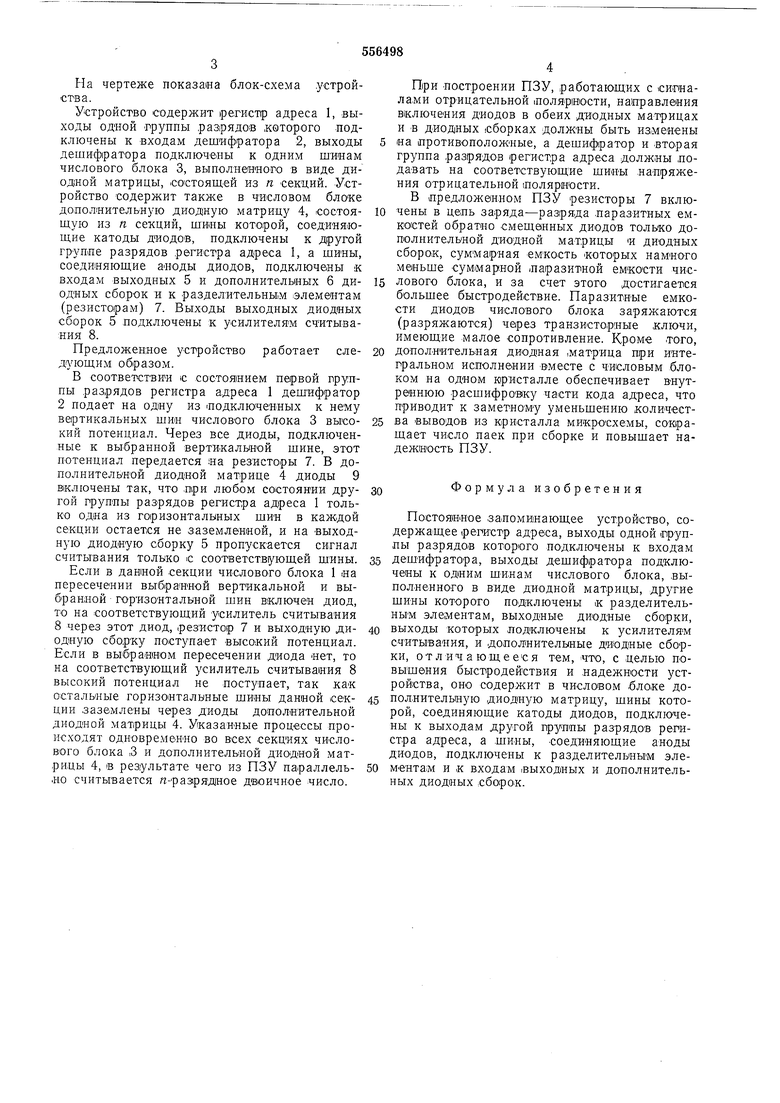

На чертеже показаиа блок-схема устройства.

Устройство содержит регистр адреса 1, выходы одной группы разрядов .которого подключены к входам дешифратора 2, выходы дешифратора подключены к одним шииам числового блока 3, выполнеяного в виде диодной матрицы, состоящей из п секций. Устройство содержит также в числовом блоке дополнительную диодную матрицу 4, состояшую из п секций, шимы которой, соедияяюш;ие катоды диодов, подключены к другой группе разрядов регистра адреса 1, а шины, соединяющие аноды диодов, подключены к входам выходных 5 и дополнительных 6 диодных сборок и к разделительным 1элементам (резисторам) 7. Выходы выходных диодных сборок 5 подключены к усилителям считывания 8.

Предложенное устройство работает следующим образом.

В соответСтвии с состоянием первой группы разрядов регистра адреса 1 дещифратор 2 подает на одну из подключенных к нему вертикальных щин числового блока 3 высокий потенциал. Через все диоды, подключенные к выбранной вертикальной щине, этот потенциал передается на резисторы 7. В дополнительной диодной матрице 4 диоды 9 включены так, что при любом состоянии другой группы разрядов регистра адреса 1 только одна из горизонтальных шин в каждой секции остается не заземленной, и на выходную диодную сборку 5 пропускается сигнал считывания только с соответствующей .

Если в данной секции числового блока 1 на пересечении выбранной вертикальной и выбранной горизонтальной шин включен диод, то на соответствующий усилитель считывания 8 через этот диод, резистор 7 и выходную диодную сборку поступает высокий потенциал. Если в выбранном пересечепии диода нет, то на соответствующий усилитель считывания 8 высокий потенциал не поступает, так как остальные горизонтальные шины данной секции заземлены через диоды дополнительной диодной матрицы 4. Указанные процессы происходят одновременно во всех секциях числового блока ,3 и дополнительной диодной матрицы 4, в результате чего из ПЗУ параллельно считывается л-раз( двоичное число.

При построении ПЗУ, работающих с сигналами отрицательной (полярности, направления включения ДИОДОВ в обеих диодных матрицах и в диодных сборках должны быть изменены на противоположные, а деши|фратор и вторая группа разрядов регистра адреса должны подавать на соответствующие шины напряжения отрицательной яолярности. В предложенном ПЗУ резисторы 7 включены в цепь заряда-разряда паразитных емкостей обратно смещенных диодов только дополнительной диодной матрицы и диодных сборок, суммарная емкость которых намного меньше суммарной .паразитной емкости числового блока, и за счет этого достигается больщее быстродействие. Паразитные емкости диодов числового блока заряжаются (разряжаются) через транзисторные ключи, имеющие малое сопротивление. Кроме того,

дополнительная диодная .матрица при интегральном исполнении вместе с числовым блоком на одном кристалле обеспечивает внутреннюю расшифровку части кода адреса, что приводит к заметному уменьшению количества выводов из кристалла микросхемы, соирашает число паек при сборке и повышает надежность ПЗУ.

Формула изобретения

Постоя1нное запоми нающее устройство, содержащее реги-стр адреса, выходы одной группы разрядов которого подключены к входам

дешифратора, выходы дещифратора подключены к одним щинам числового блока, выполненного в виде диодной матрицы, щины которого подключены к разделительным элеиментам, выходные диодные сборки,

выходы которых подключены к усилителям считывания, и допол1нительные диодные сборки, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит в числовом .блоке дополнительную диодную матрицу, шины которой, соединяющие катоды диодов, нодклю шны к выходам другой разрядов регистра адреса, а шины, соединяющие аноды диодов, подключены к разделительным элементам и к входам .выходных и дополнительных диодных сборок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU767841A2 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU750562A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU739653A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Постоянное запоминающее устройство | 1973 |

|

SU468304A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

| Трансформаторное постоянное запоминающее устройство | 1974 |

|

SU577566A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

Авторы

Даты

1977-04-30—Публикация

1975-03-04—Подача