Изобретение относится к вычислительной технике, в частности к постоянным запоминающим устройствам (ПЗУ).

Известны ПЗУ, содержащие дещифратор адреса, накопитель и усилители считывания. Однако известные ПЗУ имеют большое количество элементов в числовом блоке устройства, большие габариты и высокую стоимость, а также сложность смены хранящейся информации.

Цель изобретения - упрощение устройства и повышение его информационной емкости.

Достигается это тем, что устройство содержит сумматор, две группы диодных сборок, а накопитель выполнен из т и () числовых блоков, т из Которых выполнены из основного числового блока и вспомогательного, причем входы каждого из т и (т+1) числовых блоков соединены с соответствующими входами дешифратора адреса, выходы основных числовых блоков и (m+l) числового блока через первую группу диодных сборок, а выходы вспомогательных числовых блоков через вторую группу диодных сборок подключены к соответствующим входам усилителей считывания, выходы которых соединены -с входами сумматора.

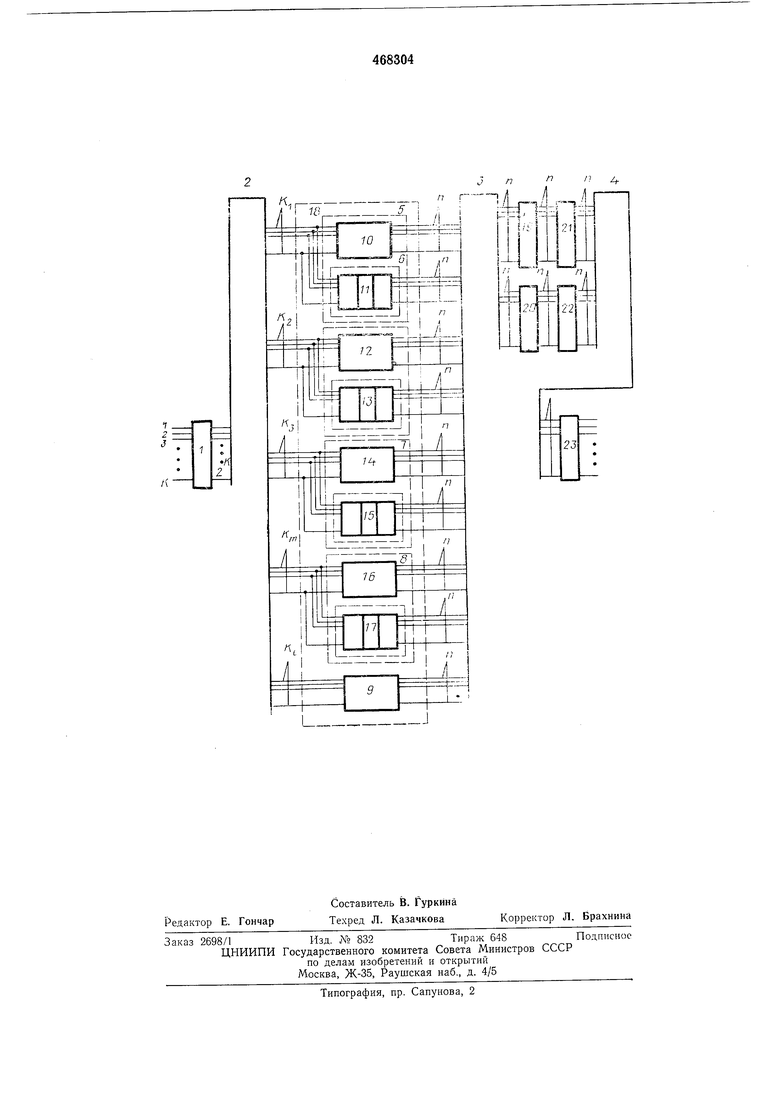

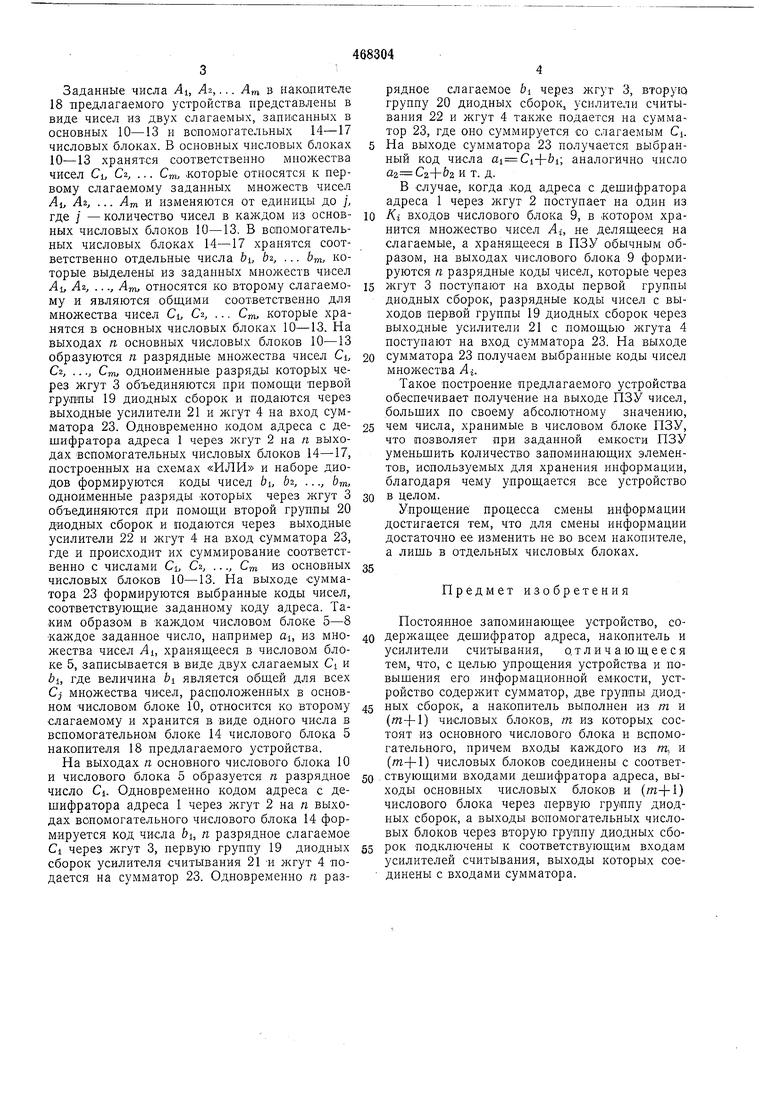

На чертеже изображена блок-схема предлагаемого устройства.

Схема содержит дешифратор адреса 1, жгуты 2-4, числовые блоки 5-9, основные числовые блоки 10-13, вспомогательные числовые блоки 14-17, накопитель 18, первую группу 19 диодных сборок; вторую группу 20 диодных сборок; усилители 21, 22 считывания и сумматор 23.

Устройство состоит из двоичного дешифратора адреса 1, 2 выходов которого собраны в жгут 2, разветвленный на Ki, К,... /С входы числовых блоков 5-8, разделенных на основные блоки 10, 11 -13 и вспомогательные 14-17 блоки и на входы числового блока 9 накопителя 18. Выходы п основных и вспомогательных числовых блоков собраны в жгут 3, разветвленный на две группы 19 и 20 диодных сборок, которые предназначены для объединения одноименных разрядов чисел из основных числовых блоков и числового блока 9, и одноименных разрядов чисел из вспомогательных числовых блоков п выходы обеих групп 19 и 20 диодных сборок через усилители 21 и 22 считывания объединяются в жгут 4, который разветвляется на входах сумматора 23.

Выборка кода числа и ПЗУ в соответствии с кодом его адреса производится в следующей последовательности: код адреса дешифратора адреса 1 через жгут 2 поступает одновременно на один из входов /d, , .., Km основных 10-13 и вспомогательных 14-17 числовых блоков 5-8.

Заданные числа Ai, Az,... Л,„ в накопителе 18 предлагаемого устройства нредставлены в виде чисел из двух слагаемых, записанных в основных 10-13 и вспомогательных 14-17 числовых блоках. В основных числовых блоках 10-13 хранятся соответственно множества чисел Сь С2, ... Cm, которые относятся к первому слагаемому заданных множеств чисел AI, Аг, ... Am и изменяются от единицы до /, где / - количество чисел в каждом из основных числовых блоков 10-13. В вспомогательных числовых блоках 14-17 хранятся соответственно отдельные числа Ьь Ь, ... Ьт, которые выделены из заданных множеств чисел Ль Аг, ..., Am, относятся КО второму слагаемому и являются общими соответственно для множества чисел Сь С, ... Cm, которые хранятся в основных числовых блоках 10-13. На выходах п основных числовых блоков 10-13 образуются п разрядные множества чисел Сь Cz, ..., Cm, одноименные разряды которых через жгут 3 объединяются нри помощи первой групяы 19 диодных сборок и подаются через выходные усилители 21 и 4 на вход сумматора 23. Одновременно кодом адреса с дешифратора адреса 1 через жгут 2 на я выходах вспомогательных числовых блоков 14-17, построенных на схемах «ИЛИ и наборе диодов формируются коды чисел ь , ..., Ьт, одноименные разряды которых через жгут 3 объединяются при помощи второй группы 20 диодных сборок и подаются через выходные усилители 22 и жгут 4 на вход сумматора 23, где и происходит их суммирование соответственно с числами Сь Сг, ..., Cm из основных числовых блоков 10-13. На выходе сумматора 23 формируются выбранные коды чисел, соответствующие заданному коду адреса. Таким образом в каждом числовом блоке 5-8 каждое заданное число, например ui, из множества чисел Ai, хранящееся в числовом блоке 5, записывается в виде двух слагаемых Ci и bi, где величина bi является общей для всех Cj множества чисел, расположенных в основном ЧИСЛОВОМ блоке 10, относится ко второму слагаемому и хранится в виде одного числа в вспомогательном блоке 14 числового блока 5 накопителя 18 предлагаемого устройства.

На выходах я основного числового блока 10 и числового блока 5 образуется п разрядное число Ci. Одновременно кодом адреса с дещифратора адреса 1 через жгут 2 на л выходах вспомогательного числового блока 14 формируется код числа &ь п разрядное слагаемое Ci через жгут 3, первую группу 19 диодных сборок усилителя считывания 21 -и жгут 4 подается на сумматор 23. Одновременно п разрядное слагаемое bi через жгут 3, вторую группу 20 диодных сборок, усилители считывания 22 и жгут 4 также подается на сумматор 23, где оно суммируется со слагаемым Сь 5 На выходе сумматора 23 получается выбранный код числа ai Ci+6i; аналогично число 0.2, и т. д.

В случае, когда код адреса с дешифратора адреса 1 через жгут 2 поступает на один из

0 K.i входов числового блока 9, в -котором хранится множество чисел Аг, не делящееся на слагаемые, а хранящееся в ПЗУ обычным образом, на выходах чи1слового блока 9 формируются п разрядные коды чисел, которые через

5 жгут 3 поступают на входы первой группы диодных сборок, разрядные коды чисел с выходов первой группы 19 диодных сборок через выходные усилители 21 с помощью л :гута 4 постзпают на вход сумматора 23. На выходе

0 сумматора 23 получаем выбранные коды чисел множества А.

Такое построение предлагаемого устройства обеспечивает получение на выходе ПЗУ чисел, больщих по своему абсолютному значению,

5 чем числа, хранимые в числовом блоке ПЗУ, что позволяет при заданной емкости ПЗУ уменьщить количество запоминающих элементов, используемых для хранения информации, благодаря чему упрощается все устройство

0 в целом.

Упрощение процесса смены информации достигается тем, что для смены информации достаточно ее изменить не во всем накопителе, а лищь в отдельных числовых блоках.

Предмет изобретения

Постоянное запоминающее устройство, со0 дерл :ащее дешифратор адреса, накопитель и усилители считывания, отличающееся тем, что, с целью упрощения устройства и повышения его информационной емкости, устройство содерл ;ит сумматор, две группы диодных сборок, а накопитель выполнен из т и (т+1) числовых блоков, m из которых состоят из основного числового блока и вспомогательного, причем входы каждого из т, и (m-f-l) числовых блоков соединены с соответствующими входами дешифратора адреса, выходы основных числовых блоков и (га+1) числового блока через первую группу диодных сборок, а выходы вспомогательных числовых блоков через вторую группу диодных сборок подключены к соответствующим входам усилителей считывания, выходы которых соединены с входами сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1977 |

|

SU750560A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Постоянное запоминающее устройство | 1975 |

|

SU556498A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU767841A2 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU750562A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

Авторы

Даты

1975-04-25—Публикация

1973-11-30—Подача