1

Изобретение относится квычислительной технике и предназначено для хранения и быстрой выборки фиксированной информации в цифровых вычислительных машинах и устройствах дискретной автоматики.

Известны постоянные запоминающие устройства (ПЗУ) , содержащие накопитель (числовой блок), выполненный в виде диодной матрицы, регистр адреса, дешифратор и усилители считывания. Существенное влияние на быстродействие диодно-матричного ПЗУ оказ|Лвает электроемкость накопителя, которая при большом объеме последнего может достигать сотен и тысяч пикофарад. Для обеспечения высокого быстродействия блочную схему ПЗУ необходимо строить так, чтобы заряд электроемкости накопителя происходил: непосредственно через открытые входные ключи, имеющие малое выходное сопротивление.

В известном ПЗУ такого типа 1 .входные шины диодно-матричного накопителя, соединяющие аноды диодов, подключены к выходам дешифратора, входы которого подсоединены к выходам первой группы разрядов регистра адреса. Выходные шины накопителя

подключены через токоограничиваю1Пие резисторы к. шинам второй диодной матрицы, со1единяющим аноды диодов, и через эти шины - к выходным диодным сборкам. Т1ины второй диодной матрицы, соединяющие катоды диодов, попарно подключены к выходам второй группы разрядов регистра адреса, а выходы диодных сборок - ко

10 входам усилителей считывания.

Данное изобретение является усовершенствованием указанного ПЗУ. Токоограничивающие резисторы, входящие в состав прототипа, включены в цепь заряда паразитных емкостей только второй диодной матрицы, суммарная величина которых намного меньше суммарной емкости элементов накопителя. Последняя же заряжается непосредственно через выходные ключи дешифратора, имеющие малое внутреннее сопротивление (1020 Ом), в силу чего время заряда оказывается меньше 10 не. ,

25

Недостатком устройства-прототипа является сравнительно большое время восстановления исходного состояния. Это свяэано с тем, что после окончания считывания информации разряд

30 электроемкости накопителя в уст рбйствё-прототипё, как и в других айалбгах, происходит через резисторы

, Большая задержка выключения небла. :гоприятно сказывается на длительйость цикла считывания.

Цель изобретения - повышение быстродействия известного ПЗУ.

ЭтЬ ЙОстйгается тем, что в состав ПЗУ по авт. св. № 556498 введены диодная сборка, входа которой под ;1 Ш Шы1с выШдй /1 Шнам liSKOWH reля, и ключ, выход которого подключен к выходу дополнительной диодной сборки, а вход является входом устройства и подсоединен ко входу дешифратора.

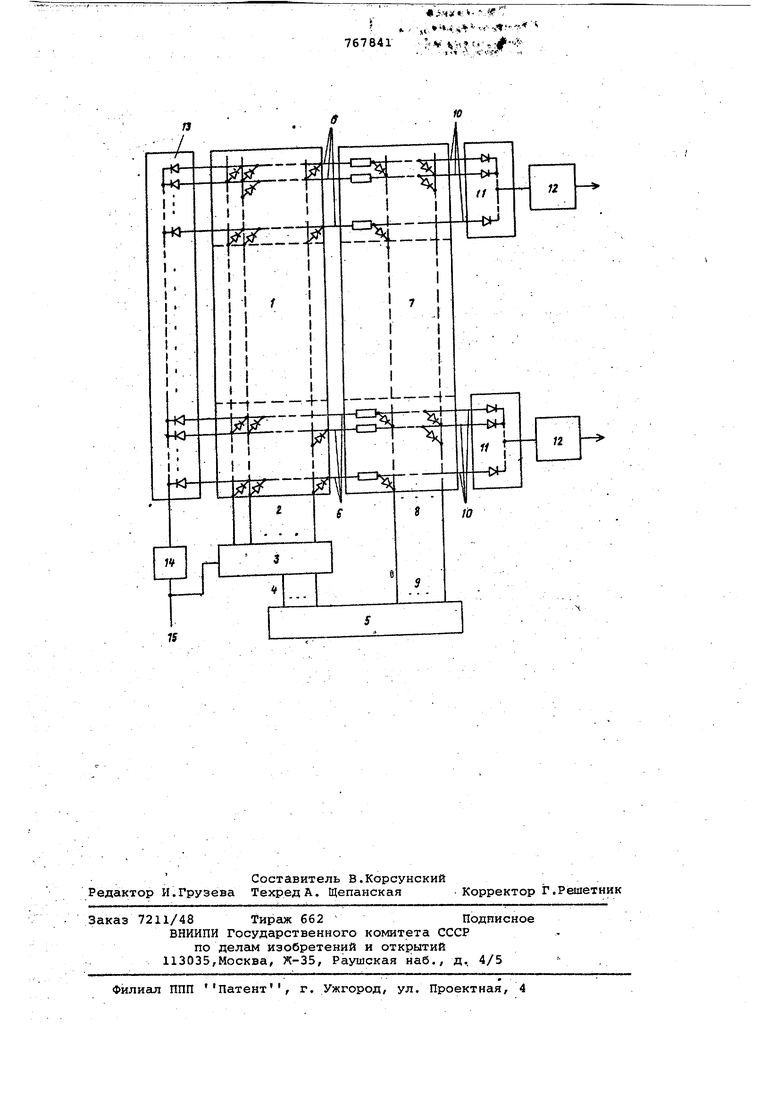

Блочная схема предлагаемого устройства представлена на чертеже,на - -jtcef545с5Й показаны также принципиальные .электрические схемы некоторых блоков, необходимые для лучшего понимания функционирования ПЗУ.

Как и устройство-прототип, предлагаемое ПЗУ содержит накопитель 1, выполненный в виде диодной матрицы и разделенный на секции. 15го входные

шины 2, соединяющие аноды диодов, .подключены к выходам деши/})ратора 3,

адресные входыкоторого подключены к выходам 4 первой группы разрядов регистра 5 адреса. Выходные (ортОгональные к входным), шины каждой секции накопителя 1 подсоединены к первым входам б соответствующей секЦйИ адресного узла 7, вторые входы 8 которого подключены к выходам 9 вто)6й группы разрядов регистра 5 адреса. Выходы 10 каждой Секции адресного узла 7 подсоединены ко входам своей выходной диодной сборки 11, выход которбй подключён к усилйтё лю 12 считывания. В отличие отуст роЙстШ-прбтотйпа -, в сост ав предлагаемо го ПЗУ в ходит тЖкзКё fttffenb ная диодная сборка 13, входы которой

подключены ко всем выходным шинам накопителя 1, и ключ 14, к которому

подключен выход дополнительной сборки 13. Вход ключа 14, также как и вхЪд разрешения выборки дешифратора 3, соединен с общим входом 15 разрешения выборки.

Устройство функционирует следующим о.бразом.

В накопитель 1 при изготовлении раз- навсегда записывается ribcfoянная информация в двоичном коде (наличию диода в перекрестийвходной и выходной шин накопителя Ьтв-етствует,. например, запись логической , а отсутствию диода запись логического ). При необходимости выборки двоичнбго слова по заданному адресу код адреса заносится в регист 5, состояние первой группы разрядов которого через йыходы 4 поступает на дешифратор 3 , и управляет возбуждением одного из выходов дешифратора, соответствующего данному состоянию. При поступлении на дешифратор по входу 15 строб-импульса чтения выбранный выход дешифратора через открытый ключ подклйчается к источнику потенциала, а .остальные выходы заземляются. Строб-импульс по входу 15 поступает также на ключ 14, который подает на выход дополнительной диодной сборки 13 высокий потенциал, в результате чего все ее диоды смещаются в рбратном направлении и практически |не влияют на процесс считывания, протекающий так, как и в устройствепрототипе. С выбранного выхода дег шифратора 3 высокий потенциал подается на соответствующие выходные шины накопителя 1 через диоды, подключенные к выбранной входной шине. Время установки высокого потенциала на выходных шинах определяется процессом заряда суммарной емкости подключенных к ним элементов накопителя.

Цепь заряда включает в себя : источник высокого потенциала, который на чертеже не показан, открытый выходной ключ дешифратора 3, подключающий к этому источнику выбранную шину, подключенные к ней и смещаемые в прямом направлении диоды, выходные шины накопителя 1, паразитные емкости между этими шинами и невыбранными входными шинами накопителя (включая и емкости смеш,аемых в обратном направг лении диодов накопителя) и выходные ключевые схемы дешифратора 3, за5 земляющие невыбранныё входные шины 2в. Благодаря малому сопротивлению перечисленных ключевых схем и источника высокоГ-о потенциала, а также малому продольному.сопротивлению шин

0 и смещенных в прямом направлении диодов, постоянная времени цепи заряда мала и высокий потенциал на выходных шинах накопителя 1 устанавливается за несколько наносекунд.

5 В адресном узле 7 диоды-включены по известной схеме матричного диодного дешифратора, так что при каждом состоянии второй группы разрядов регистра 5 адреса, передаваемом с

0 выходов 9 на входы 8, только один из выходов 10 каждой секции адресного узла 7 не заземляется и через этот выход на диодную сборку 11 и далее в усилитель 12 считывания пвгредаетсясигнал только с одного из входов б, номер которого соответствует данному состоянию второй группы разрядов регистра 5 адреса. Сигналы с остальных входов 6 каждой секции адресного узла 7 ответвляются на

0 землю и на вход соответствующей диодной сборки 11 не передаются. Если в Данной секции накопителя 1 на пересечении выбранной входной шины и выходной шины, подключенной к

5 выбранному входу 6, имеется диод, то на выход соответствующей диодной сбЬ ки 11 передается высокий потенциал и соответствующий усилитель 12 считывания формирует сигнал считывания логической 1 . Если же в соответ ствуюспем перекрестии данной секции диЪда нет, то на выход соответст вующей диодной сборки 11 высокий потенциал не передается и соответству ющий усилитель 12 считывания форми рует сигнал считывания логического О. Указанные процессы происходят одновременно во всех секциях накопит ля 1, адресного узла 7, выходных диодных сборках 11 и усилителях 12 считывания, так что из ПЗУ одновременно выбирается многоразрядное двоичное слово. Считывание информации заканчивается, когда кончается строб-импульс чтения, подаваемый по входу 15. При этом выбранная входная шина 2 накопителя 1 отключается дешифратором 3 от источника высокого потенциала и заземляется вместе с остальными входными шинаш 2. Ключ 14 в свою очередь заземляет выход дополнительной диодной сборки 13. Следующий цикл считывания не может быть начат немедленно, поскольку заряженные до высокого потенциала паразитные емкости могут сыграть роль источников напряжения и привести к считыванию ложных сигналов . Разряд сравнительно небольших паразитных емкостей адресного узла 7 и выходных диодных сборок 11 происходит через входные цепи усилителей 12 считывания. Сравнительно большая паразитная емкость накопителя. 1 раз ряжается через смещение в прямом направлении диоды дополнительной сборки 13 открытый ключ 14 и выходные ключевые схемы дешифратора 3, заземляющие его выходы в невозбужденном состоянии. Поскольку сопротивления всех перечисленных элементов малы, разряд паразитных емкостей накопителя и восстановление исходного его состояния также происходят быстро (за время менее 10 не) . При 6т сутствии доп олнительной ДИОДНОЙ сборки 13 и ключа 14 паразитная емкость накопителя 1 должна разряжаться через токоограничивающие резисторы адресного узла 7, номинал которых определяется допустимым рассеянием мощности и обычно составляет 3-6 кОм,в результате чего разряд оказывается сравнительно медленным, а время восстановления исходного состояния составляет 120-7 300 НС. Таким образом, введение дополнительной диодной сборки и ключа позволяет уменьшить время восстановления исходного состояния на порядок и за счет этого существенно - , повысить быстродействие ПЗУ. Формула изобретения Постоянное запоминающее устройство по авт. ев, 556498, отличающееся тем, что, с целью повышения быстродействия, в него введены дополнительная диодная сборка, входы которой подключены к выходным шинам накопителя, и ключ, вход которого является входом устройства и подключен ко входу дешифратора, а выход ключа подключен к выходу дополнительной диодной сборки. Источники информации, принятые во внимание при экспертизе 1. Авторские свидетельство СССР W556498, кл. G Ц С 17/00, 1975 (прототип).

, .

.

767841 -, « A . .а V.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1975 |

|

SU556498A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU739653A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Запоминающее устройство | 1968 |

|

SU842961A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Постоянное запоминающее устрой-CTBO | 1979 |

|

SU809381A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Трансформаторное постоянное запоминающее устройство | 1974 |

|

SU577566A1 |

Авторы

Даты

1980-09-30—Публикация

1978-09-18—Подача