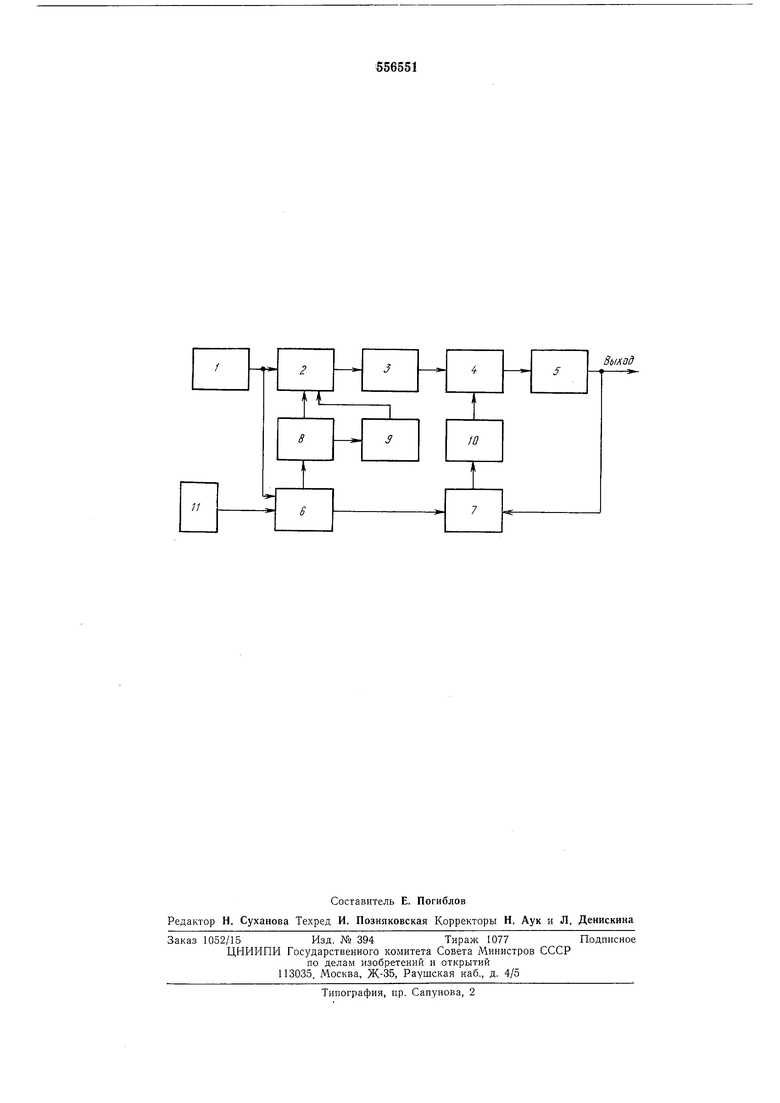

Устройство содержит последовательно соединенные опорный генератор I, синхронный сумматор 2 но модулю два, делитель 3 частоты на два, сумматор 4 по модулю два и делитель 5 частоты на т, при этом выход опорного генератора 1 через блок согласования 6 входного сигнала с тактовыми импульсами опорного генератора соединен с первым входом фавового дискриминатора 7, второй вход которого подключен к делителю 5 частоты на т, второй выход блока согласования 6 через последовательно соединенные тактируемый триггер 8 и элемент задержки 9 соединен с вторым входом синхронного сумматора 2, третий вход которого соединен с другим выходом тактируемого триггера 8, а второй вход сумматора 4 через счетный триггер 10 подсоединен к выходу фазового дискриминатора 7.

Устройство работает следующим образом.

Импульсная последовательность опорного генератора 1, имеющая форму меандра, через синхронный сумматор 2 по модулю два, делитель 3 частоты на два и сумматор 4 по модулю два подается на вход делителя 5 частоты на т, выход которого является выходом устройства. Частота выходного сигнала, имеющего форму меандра, равна номинальному значению тактовой частоты входного сигнала.

Поступающий от источника 11 входной (сигнал поступает на блок согласования 6, в /котором осуществляется логическое дифференцирование этого сигнала, т. е. при изменении полярности сигнала формируются импульсы, привязанные по фазе к тактовым позициям имиульсов опорного генератора. Каждый из этих импульсов, поступая на тактируемый триггер 8 вызывает изменение полярности напряжения на его выходе. При этом сигнал на выходе синхронного сумматора 2 по модулю два также изменяет свою полярность, что приводит к увеличению длительности одного из полупериодов выходного сигнала на половину периода частоты опорного генератора, соответствующему шагу коррекции фазы в сторону отставания. На второй вход синхронного сумматора 2 по модулю два поступает сигнал от тактируемого триггера 8, задержанный элементом задержки 9 на половину периода частоты опорного генератора. Этот сигнал, перекрывающий моменты переключения синхронного сумматора 2 по модулю два, позволяет устранить короткие импульсы на его выходе, появление которых возможно из-за разброса времени срабатывания логических элементов.

В тех случаях, когда коррекция фазы осуществляется не по всем фронтам входного сигнала, тактируемый триггер 8 работает в счетном режиме. Если же для коррекции фазы используются все фронты входного сигнала, тактируемый триггер 8 может работать в

регистровом режиме, что в некоторых случаях позволяет использовать в качестве тактируемого триггера 8 и элемента задержки 9 триггеры блока согласования 6, формирующие нмпульс логического дифференцирования.

Одновременно импульсы блока согласования 6 поступают на вход фазового дискриминатора 7, где происходит сравнение его фазы с фазой выходного сигнала, поступающего с

выхода делителя б частоты на т. При этом, если входной сигнал опережает по с|)азе выходной сигнал, фазовый дискриминатор 7 выдает импульс, вызывающий срабатывание счетного триггера 10, что приводит к инвентированию сигнала на выходе сумматора 4 по модулю два. Поскольку срабатывание происходит со сдвигом по времени на половину периода частоты опорного генератора 1 относительно фронта выходного сигнала делителя 3

частоты на два, это само по себе приводит к сдвигу выходного сигнала -на период частоты опорного генератора в сторону опережения, а результирующий сдвиг фазы выходного сигнала за счет воздействия обоих сумматоров по

модулю два оказывается равным половине периода частоты опорного генератора.

Таким образом, предлагаемое устройство дискретной фазовой синхронизации позволяет уменьшить шаг коррекции до половины периода частоты опорного генератора, что дает возможность без повышения быстродействия используемых элементов в два раза повысить точность фазирования. Кроме того, возможность использования более низкой частоты

опорного генератора упрощает конструкцию устройства и в ряде случаев снижает его стоимость.

Формула изобретения

Устройство для дискретной фазовой синхронизации, содержащее делитель частоты на два и последовательно соединенные опорный генератор, блок согласования входного сигнала с тактовыми импульсами опорного генератора и фазовый дискриминатор, второй вход которого подключен к делителю -частоты иа т, отличающееся тем, что, с целью повышения точности фазирования, между опорным генератором и делителем частоты на два

включен синхронный сумматор по модулю два, второй вход которого подсоединен через последовательно включенные тактируемый триггер и элемент задержки к второму выходу блока согласования входного сигнала с

тактовыми импульсами опорного генератора, а третий -к другому выходу тактируемого триггера, между делителем частоты на два и делителем частоты на т включен сумматор по модулю два, второй вход которого подключен

через счетный триггер к выходу фазового дискриминатора.

Вшад

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

| Цифровой демодулятор сигналов с относительной фазовой модуляцией | 1981 |

|

SU985970A1 |

| Помехоустойчивый цифровой фазометр | 1979 |

|

SU1002979A1 |

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1983 |

|

SU1131034A2 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство синхронизации | 1981 |

|

SU1159173A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| Устройство тактовой синхронизации | 1987 |

|

SU1555892A1 |

Авторы

Даты

1977-04-30—Публикация

1974-05-17—Подача