ключей .выход преобразователя интер вал - число, и с вторым входом второго распределителя, выходы.которого подключены к одним входам первого блока считывания, другие входы которого соединены с выходами блока памяти, .к входам которого подключены выходы блока записи, входы которого соединены с выходом второго блока считывания и с выходами третьего распределителя, к первому входу которого подключен выход первого элемента И, второй вход которого соединен с выходом второго элёмегта И, к первому входу которого подключен выход второго триггера, и с входом .первого распределителя, второй выход которого подключен к второму входу третьего распределителя, к первому входу второго триггера и к первому входу первого триггера, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с вторым входом первого триггера и с выходом блока выделения значащих моментов модуляции, причем выкхэд третьего элемента И подключ.ен к вто- . рому входу второго триггера и к второму входу преобразователя интервал число, соответствующие входы которого соединены с одними выходами накопителя , другие выходы которого подключены к одним входам второго блока считывания, к другим входам которого подключены соответствующие выходы первого распределителя, а выход первого блока считывания подключен к входу третьего триггера, второй вход второго эл}емента И соединен с соответствующим выходом датчика синхронных импуль.сов.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДВОИЧНЫХСИГНАЛОВ | 1971 |

|

SU313302A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство для анализа кинематической погрешности зубчатых передач | 1984 |

|

SU1227945A1 |

| КОМПЛЕКС МНОГОКАНАЛЬНОЙ ЭКСПРЕСС ДИАГНОСТИКИ | 1997 |

|

RU2152073C1 |

| Устройство для передачи и приема дискретных сигналов | 1984 |

|

SU1290556A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Запоминающее устройство | 1988 |

|

SU1547032A1 |

| Двухкратная стартстопно-синхронная система передачи дискретной информации | 1988 |

|

SU1570018A1 |

| Устройство для регистрации сейсмической информации | 1984 |

|

SU1196841A1 |

УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ.И ПРИЕЙА ДИСКРЕТНЕЛХ СИГНАЛОВ, содержащее на передающей стороне блок вьаделения значащих моментов модуляции, преобразователь интвервал - число, первый распределитель, счетчик, датчик синхронных импульсов, выход которого подключен к первому входу первого элемента И, и второй элемент И а на приемной стороне - первый триггер , датчик синхронных импульсов, выходы которого подключены к первому входу преобразователя интервал - -число и к входу накопителя, выход которого соединен с входом блока выделения значащих моментов модуляции, и первый распределитель, первый выход которого подключён к первому входу первого элемента И, о т л и ч а-ющ е е с я тем, что, с целью повыше-. ния пропускной способности, на передающей стороне введены два блока за- писи, блок-памяти, накопитель, второй и третий распределители, блок считывания, два триггера, третий элемент И и датчик импульсов записи, выход которого подключен к первому входу первого распределителя и к входу счетчика, выход которого соединен с первыми входами датчика импульсов записи и первого триггера, выход которо.го подключен к первому входу второго элемента И и с вторым вхо-, .дом первого распределителя, выходы которого подключены к одним входам первого блока записи, другой вход и выходы которого соединены соответственно с входом бл.ока выделения значащих моментов модуляции и с входами блока памяти, выходы которого подключены к одним входам блока считывания, другие входы и каход которого соединены соответственно с выходами второго распределителя и ,с одним входом второго блока записи, вых.оды которого подключены к, одним входам накопителя, другие входы которого соединены с выходами преобразователя интервал - число, входы которого соедин.ены с.первым выходом датчика синхронных импульсов, с выходом второго элемента И, с вторым входом датчика им(О пульсов запис.и и с первым вх.одрм второго триггера, выход которого подключен к второму входу первого элемента И, выход которого соединен с первым входом третьего элемента И и с входом третьего распределителя, выхЬды которого соединены с вторь м входом второго триггера, с первым входом второго распределителя, с другими входами второго блока запи р: си и с вторым входом третьего элемента И, выход которого подключен к 00 Второму входу второго распределителя, 4 при этом второй выход датчика син- 00 хронных импульсов подключен к другому входу накопителя, выход блока выделения значащих моментов модуляции соединен с вторыми входами первого триггера и второго элемента И, а на приемной стороне введены два элемента И, второй и третий триггеры, два блока считывания, блок памяти, блок записи,счетчик циклов и датчик импульсов считывания, выход которого подключен к первому входу второго распределителя и к входу счетчика циклов , выход которого соединен с первым входом датчика импульсов считывания, к второму входу которого под

Изобретение относится к технике телеграфной связи и может использова:ся для синхронного ввода стартстопных телеграфных сигналов в цифровой канал.

Известно устройство для передачи и приема дискретных сигналов, содержащее на передающей стороне блок выделения . значащих моментов модуляции, преобразователь интервал -- число, первый .распределитель, счетчик, датчик синхронных импульсов, выход которого подключен к первому входу., первого элемента И, и второй эле-, мент И, а на Щ)иемной стороне - первый триггер, датчик синхронных импульсов, выходы которого подключены к первому входу 1реобразователя ин-, тербал - число и к входу накопителя, выход которого соединен с входом блока выделения значащих моментов модуляции и первый распределител.ь, 1ервый выход которого подключен к пер вому входу первого элемента И 1 3.

Однако известное устройство имеэт низкую пропускную способность,

Цель изобретения - повышение щ)опускной способности.

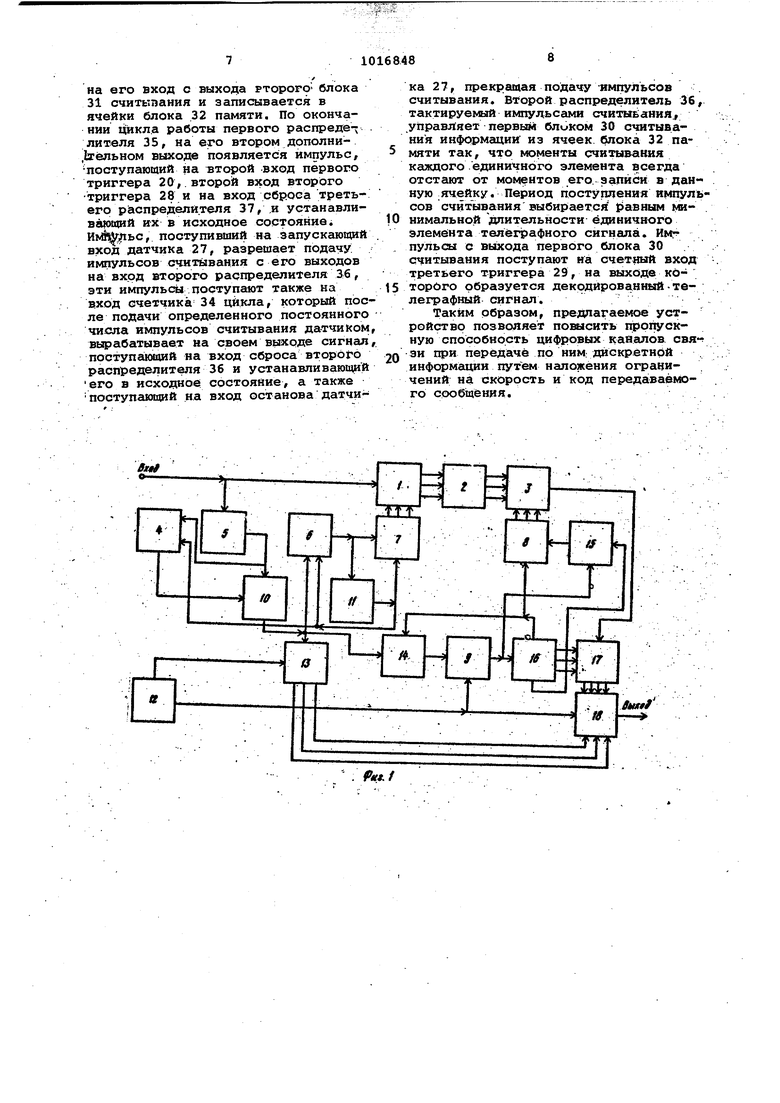

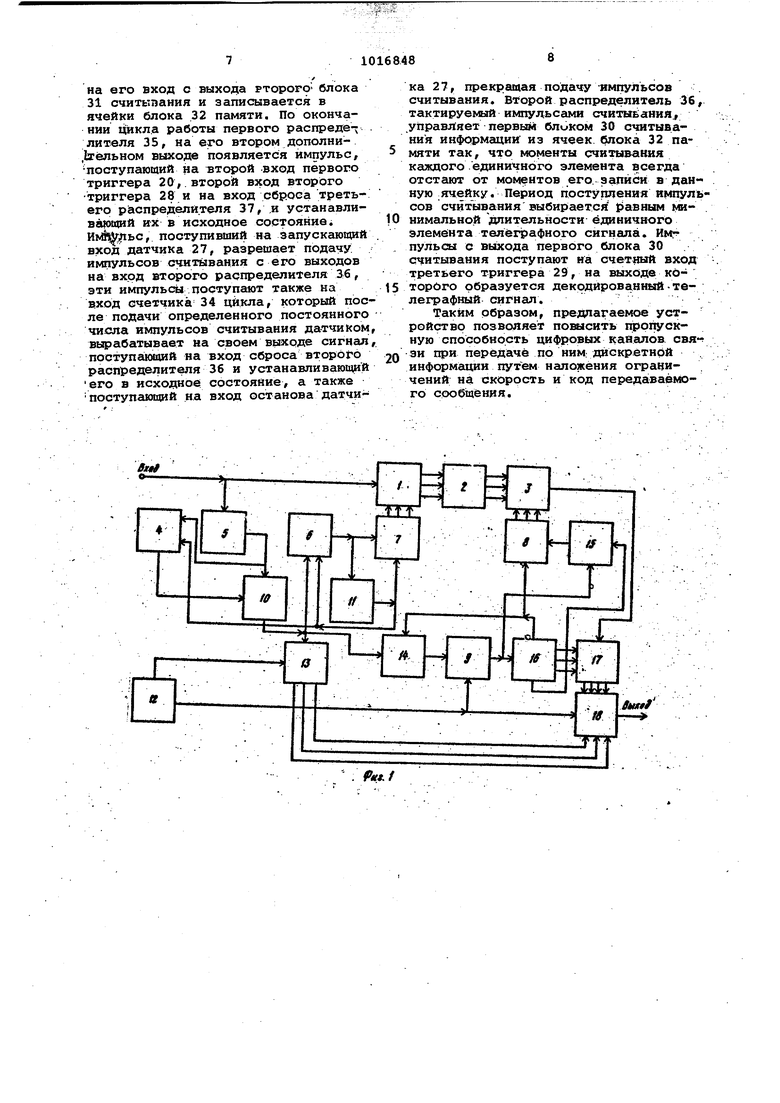

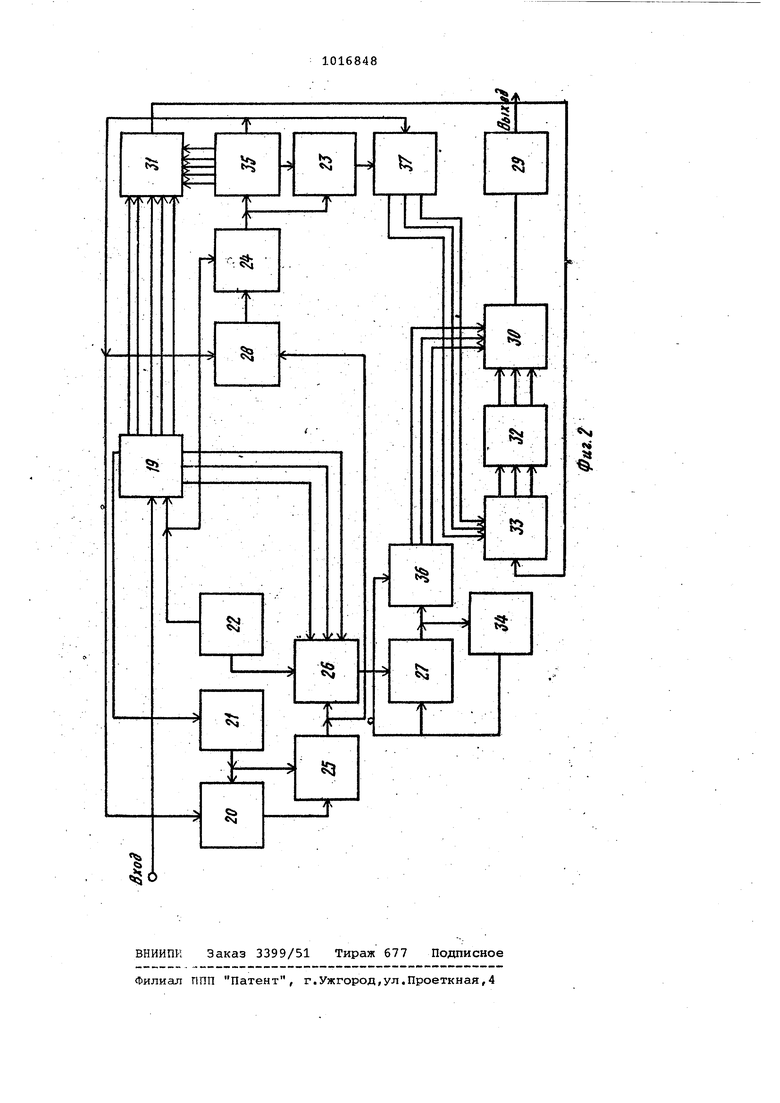

Для достижения поставленной цели в устройство для передачи и приема дискретных сигналов, содержащее на передаквдей стороне блок вы щцения значащих моментов модуляции, преобразователь интервал - число, первый распределитель, счетчик, датчик синхронных импульсов, выход которого подключен к первому входу первого элемента И и второй элемент И, а на приег шой стороне - первый триггер, датчик синхронных импульсов, выходы которого подключены к первому входу преобразователя интервал число и к входу накопителя, выход которого соединен с входом блока выделения начащих моментов, модуляции, и первый распределитель, первый выход которого подключен к первому входу первого элемента И, на передающей стороне введены два блока записи, блок памяти, накопитель, второй и третий распределители, блок считывания, два триггера, третий элемент И и датчик импульсов записи, выход.которого подключен к первому входу первого, распределителя и к входу счетчика, выход которого соединен с первыми входами датчика ИМПУЛЬСОВ записи и первого триггера, , выход которого подключен к первому входу второго элемента И, с вторым входом первого распределителя, выходы которого подключены к Одним входам первого, блока записи, другой вход и выходы которого соединены соответственно с входом блока выделения значащих моментов модуляции и с входами блока памяти, выходы которого подключены к одним входам блока считывания, другие входы и выход которого соединены соответственно с выходами второго распределителя и с одним входом второго блока записи, выходы.которого подключены к одним входам накопителя, другие входы которого соединены с выходами преобразователя интервал - число. входы которого соединены с первым выходом датчика синхронных импульСОВ, с выходом второго элемента И с вторым входом датчика импульсов записи и с первым входом второго триггера, выход которого подключен к второму входу первого элемента И, выход которого соединён с первым входом третьего элемента И с третьего распределителя, выходы которого соединены с вторым .входом второго триггера, с первым входом второго распределителя, с другими входами второго блока записи и.с вт рым входом третьего .элемента И, вы ход которого подключен к второму входу BTopoi b распределителя, при этом второй выход датчика синхронных импульсов подключен к другому входу накопителя, выход блока вваделения значаищх моментов модуляции соединен с вторыми входами первого триггера и второго элемента И, а на приёмной стороне введены два эле мента И, второй и третий триггеры два блока считывания, блок памяти блок записи, счетчик .циклов и датчик импульсов считывания, выход которого подключен к первому входу второго распределителя и к входу счетчика циклов, выход которого со единен с первым входом датчика Я1Лпульсов считывания, к вгторому входу которого подключен выход преобразов теля интервал -число, и с вторьам входом второво распределителя, выхо ды которого подключены к одним входам первого, блока Считывания, други входы которого соединены с выходами блока памяти, к входам которого под клнМены выходы блока записи, .йхода которого соединены с,выходом второг блока считывания и с выходами треть его, распределителя, к первому входу котюрого подключен выход первого эл мента И, второй вход которого соеди нен с выходе второго элемента И, к первому входу которого подключен выход второго триггера, и с входом первого распределителя, второй выхо которого подключен к второму входу, третьего распределителя, к первому входу второго триггера и к первому входу первого триггера, выход которого соединен с первым входом треть его элемента И, второй вход которо1 0 соединен с вторым входом первого триггера и с выходом блока выделени значащих, моментов модуляции, причем выход третьего элемента И подключен к второму входу второго триггера и к второму входу преобразователя интервал - число, соответст.вуюцдае . входы которого соединены с одними выходами накопителя, другие выходы которого подключены к одним входам второго блока считывания, к другим входам которого подключены соответствующие выходы первого распределителя, а выход пе.рвого блока считыва ния подключен к входу третьего триггера, второй вход второго элемента И соединен с соответствующим выходом датчика синхронных импульсов. На фиг.. 1 представлена структурная электрическая схема передакицей стороны предлагаемого устройства, на фиг. 2 - приемной стороны. Устройство для передачи и лриема дискретных сигналов содержит на петредающей стороне (фиг. 1) первый блок 1 записи, блок 2 памяти, блок 3.считывания, первый триггер 4, блок 5. выделения значащих моментов модуляции, датчик 6 импульсов записи, первый и второй распределители 7 и 8 соответственно, первый и второй элементы И 9 и 10 соответственно, счетчик 11, датчик 12 синхронных импульсов, преобразователь 13 интервал число, второй триггер 14, элемент И 15, третий распределитель 16, второй блок 17 записи и накопитель . 18, а на приемной стороне (фиг,2) накопитель 19, первьпй триггер 20, блок 21 выделения з.начаи их моментов ьюдуляции, датчик 22 синхронных импульсов, первый, второй и третий элементы И 23, 25 соответственно, преобразователь 26 интервал число, датчик 27 импульсов считыванид, рторой и третий триггеры 28 и 29 соответственно, первый и второй блоки 30 н- 31 считывания соответственно, блок 32 памяти, .блок; 33 записи, счетчик 34 циклов, первый, второй и третий распределители 35, 36 и 37 соответственно, ,, Устройство работает следующим образом. Телеграфный сигнал на передающей стороне (фиг. 1() устройства поступает на вход блока 5 выделения значащих моментов модуляции и на вход первого еЗлока 1 записи. В момент появлений значащего момента на выходе блока 5 появляется короткий импульс., который через второй эл.е мент И io. поступает на вход запуска датчика б импульсов записи, на вход преобразователя интервал - число 13 и второй триггер 14. Кроме того,с выхода блока .5 импульс поступает на вход первого триггера 4, который переключается и закрывает второй элемент И 10 с задержкой, равной длительности импульса. От последующих импульсов с блока 5 он не меняет своего состояния. Пришедший на вход датчика б импульс включает дат- . чйк импульсов записи, который информирует серию из семи импульсов с периодом, равным длительности единичного элемента поступающего телеграфкого сигнала, которые поступают на вход первого распределителя 7 и счетчик 11. Пе.рвый блок 1 записи, управляемый первым распределителем 7, обеспечивает запись единичных элеме тов телеграфного сигнала в блок 2 памяти. После приема семи импульсов счетчиком 11 на его выходе формируется сигнал, возвращающий первый, триггер 4 и первый распределитель 7 в исходное состояние и запрещающий подачу импульсов с датчика 6. Импул поступивший на вход преобразователя 13, производит стробирование кодиру ющих сигналов, поступающих с датчика 12, в результате чего с выходов преобразователя 13 на входы накопителя 13 одновременно поступают корот ;,кие импульсы, содержащие в двоичном коде информацию о полярности и мест положении пришедшего значащего момента относительно тактовых импуль.сов цифрового канала. Импульс, поступивший на вход второго триггера 14 устанавливает его в состояние, при котором сигнал на его выходе открывает первый элемент И 9, на второй вход которого поступают такто вые импульсы -С датчика 12. С выхода первого элемента И 9 тактовые импуль сы поступают на вход второго распределителя 8 через третий элемент И 15 открывающийся только в случае, когда хотя бы на одном из выходов третьего распределителя 16, включенных во второй блок 17 записи, имеется логическая 1. Второй распределитель В управляет считыванием информации из ячеек блока 2 памяти посредством блока 3 считывания, причем моменты считывания элементов стартстопной телеграфной комбинации из ячеек блока памяти отстают па., времени от моментов записи их на время, меньшее ее длительности. С выхода блока 3 информационный сигнал поступает на вход второго блока 17 записи. Третий распределитель 16, тактируемый синхроимпульсами, управляет записью в ячейки накопителя 18 информации , поступающей на вход второго блока 17 записи. Информация, записанная в накопитель, представляющий из себя регистр сдвига с установочными входами, подвигается в нем на выход при помощи тактовых импульсов, поступающих с датчика 12, синхронизированного с тактовыми импульсами цифрового канала. По окончании цикла передачи на дополнительном выходе третьего распределителя 16 появляется импульс, устанавливающий второй триггер 14 и второй распределитель 8 в исходное состояние, причем третий распределитель 16 также возвращается в исходное состояние. После передачи последнего эле мента кодовой комбинации и до появления в телеграфном сигнале следуюп1,йго значащего момента с выхода накйпителя передаются сигналы подтрйржд ния, по значению соответствующие последнему переданному элементу, что достигается введенной в накопитель 18 обратной связи. Процесс декодирования поступающего на вход приемной стороны (фиг.2) устройства синхронного двоичного сигнала происходит следующим образом. Синхронный двоичный сигнал поступает на вход накопителя 19, куда он записывается при помощи синхроимпульсов, подаваемых на тактовый вход накопителя с выхода датчика 22. После того, как в накопитель будут записаны стартовый и уточняющие элементы кодовой комбинации, на выходе блока 21 появится короткий импульй, поступающий через третий элемент И 25 на вход запуска.преобразователя 26 и на вход второго триггера 28. Кроме того, с выхода.блока 21 импульс поступает на вход первого триггера 20, который переключается и зак хлвает третий элемент И 25 с задержкой, равной длительности импульса. От последующих импульсов с блока 21 первый триггер 20 не меняет своего состояния. С момента поступления им-пульса на вход запуска преобразователя 26 начинается процесс декодирования временного интервала преобразователем 26, причем код временного интервала считывается с соответствующих выходов накопителя 19, а декодирующие импульсы поступают с датчика 22. По истечении времени декодирования, равного величине временного интервала, на выходе преобразователя 26 появляется сигнал, запускающий датчик импульсов считывания 27. Импульс с выхода третьего элемента И 25 поступает также на вход второго триггера 28, устанавливая его в состояние, при котором сигнал на его выход.е открывает второй элемент И 24, в результате чего синхроимпульсы с датчика 22, подключенного к второму входу второго элемента И 24, поступают на тактовый вход первого распределителя 35 считыйания) .и на вход первого элемента И .23. Первый распределитель 35, тактируемый синхроимпульсами, управляет вторым блоком считывания 31 так, что моменты считывания из накопителя на половину тактового интервала отстают от моментов записи. Сигнал на дополнительном выходе первого распределителя 35,, подключенном к второму входу первого элемента И 23 открывает последний только при наличии на одном из выходов пер вого распределителя 35 логической 1. С выхода первого элемента И 23 импульсы поступают на тактовый вход третьего распределителя 37 (записи), управляющего блоком 33 записи, причем информационный сигнал поступает

на его вход с выхода второго- блока 31 считьтпания и записывается в ячейки блока 32 памяти. По окончании цикла работы первого Р сгфеде , лителя 35, на его втором дополни Ьгёльном выходе появляется импульс, поступающий на второй -вход первого триггера 20, второй вход второго .ригге а 28и на вход сброса третье о Определителя 37, ,и устанавливающий их в исходное состояние. иЖьс, поступивший на запускающий fiS датчика 27, разрешает подачу считывания с его выходов второго распределителя 36, эти импульсы поступают также на 1ход счетчика 34 цикла, который после о2чи определенного постоянного числа ИМПУЛЬСОВ считывания Датчиком

Гс пгГ ГвйГс г«о г

:поступающий на вход останова датчика 27, прекращая по)цачу импульсов считывания. Второй распределитель 36, тактируемый импульсами считнйания, управляет первым блоком 30 считывания информации из ячеек блока 32 памяти так, что моменты считывания каждого единичного злемента всегда отстают от моментов его записи в данную ячейку. Период поступления импульсов считывания выбирается {Равным минимальной длительности единичного элемента телвг рафного сигнала, имг пульсы с выхода первого блока 30 считывания поступают на счетный вход третьего триггера 29, на выходе торого образуется декодированный-телеграфный сигнал.,

Таким образом, предлагаемое устройство позволяет пошсить щ опускную способность цифровых каналов свя,0 эй при передаче по ним дискретной информации путем наложения ограничений на скорость и код передаваемого сообщения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДВОИЧНЫХСИГНАЛОВ | 0 |

|

SU313302A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-05-07—Публикация

1981-04-29—Подача