(54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Накопитель телеграфных кодовых комбинаций | 1974 |

|

SU557504A1 |

| Устройство для регистрации телеграфных посылок | 1983 |

|

SU1234977A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Буферное запоминающее устройство | 1974 |

|

SU493805A1 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с последовательным доступом | 1981 |

|

SU982084A1 |

Предлагаемый накопитель может быть использован в качестве буферного устройства и дискретных системах связи, в частности в передатчике и приемнике телеграфного аппарата, а также в качестве оперативного запо.минающего устройства.

Известны накопители телеграфных кодовых комбинаций, где устройство содержит накопитель на регистрах сдвига на N разрядов и счетчик с коэффициентом счета равным N . Выходы разрядов счетчика подключены ко входам элемента И, с выхода которого поступает сигнал, управляющий записью и считыванием информации в накопитель. Для адресации используется фазовый признак представления адресе, гтриче.м при записи очередного знака фаза счетчика меняется на один шаг под воздействием сигналов формирователя одиночных импульсов 1 .

Аналогичный фазовый признак представления адресов использован в накопителе телеграфных кодовых комбинаций, где накопитель выполнен в виде -разрядных регистров сдвига, где «/С - число разрядов

В КОДОВОЙ ко бинации, а N - число хранимых кодовых комбинаций 2.

Входные информационные шнны подключены через переключатепь ко входам соответствующих регистров. Адрес очередной ; -тсываемой комбинации хранится в счетчггке записи с коэффициентом счета равным У, выходы разрядов которого подключены Kj входам первого элемента И, выход которого подключен к управляющим входам пере -;л очателей и входу второго элемента И. Выход этого второго элемента И подключен к установочному входу сигнального триггера заполнения накопит&тя, другой установочный вход триггера подключен к шине считывания.

Другой вход второго элемента . И подключен к выходу третьего элемента И, входы которого подключены к выхода.м разрядов счетчика считывания, с коэффициентом счета равным N .

В счетчике считывания хранятся адреса сч;:тывае; Ь х кодовых комбинаций.

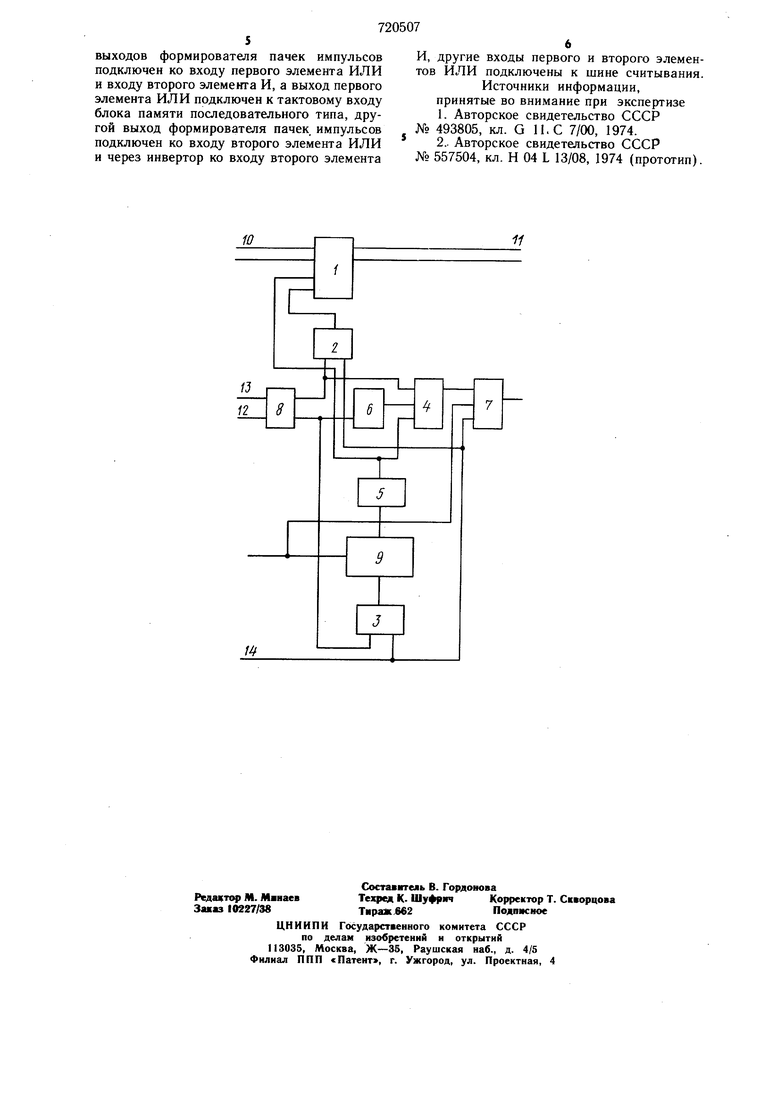

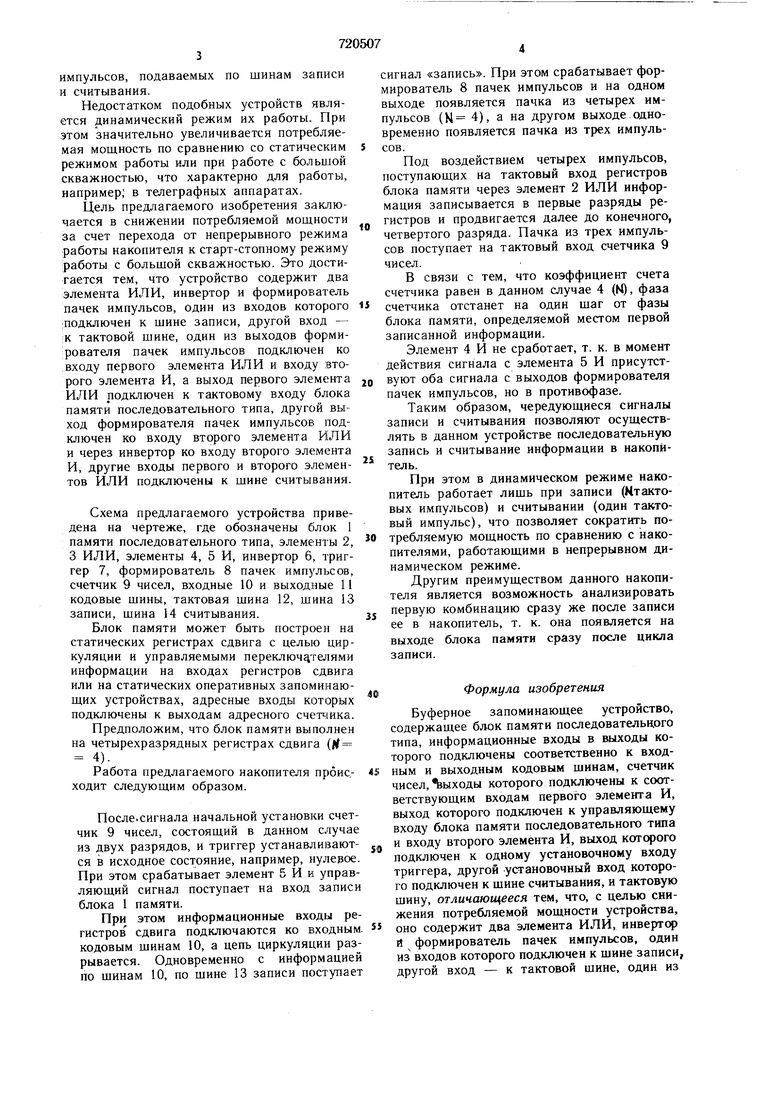

Фаза счетчиков записи и считывания изменяется под воздействием одиночных импульсов, подаваемых по шинам записи и считывания. Недостатком подобных устройств является динамический режим их работы. При этом значительно увеличивается потребляемая мощность по сравнению со статическим режимом работы или при работе с большой скважностью, что характерно для работы, например; в телеграфных аппаратах. Цель предлагаемого изобретения зак,лючается в снижении потребляемой мощности за счет перехода от непрерывного режима работы накопителя к старт-стопному режиму работы с большой скважностью. Это достигается тем, что устройство содержит два элемента ИЛИ, инвертор и формирователь пачек импульсов, один из входов которого ;подключен к шине записи, другой вход - ;К тактовой шине, один из выходов формирователя пачек импульсов подключен ко входу первого элемента ИЛИ и входу второго элемента И, а выход первого элемента ИЛИ подключен к тактовому входу блока памяти последовательного типа, другой выход формирователя пачек импульсов подключен ко входу второго элемента ИЛИ и через инвертор ко входу второго элемента И, другие входы первого и второго элементон ИЛИ подключены к шине считывания. Схема предлагаемого устройства приведена на чертеже, где обозначены блок 1 памяти последовательного типа, элементы 2, 3 ИЛИ, элементы 4, 5 И, инвертор 6, триггер 7, формирователь 8 пачек импульсов, счетчик 9 чисел, входные 10 и выходные 11 кодовые шины, тактовая шина 12, шина 13 записи, шина 14 считывания. Блок памяти может быть построен на статических регистрах сдвига с целью циркуляции и управляемыми переключателями информации на входах регистров сдвига или на статических оперативных запоминающих устройствах, адресные входы которых подключены к выходам адресного счетчика. Предположим, что блок памяти выполнен на четырехразрядных регистрах сдвига (it 4). Работа предлагаемого накопителя прбисходит следующим образом. После,сигнала начальной установки счетчик 9 чисел, состоящий в данном случае из двух разрядов, и триггер устанавливаются в исходное состояние, например, нулевое. При этом срабатывает элемент 5 И и управляющий сигнал поступает на вход записи блока 1 памяти. При этом информационные входы регистров сдвига подключаются ко входным кодовым шинам 10, а цепь циркуляции разрывается. Одновременно с информацией по шинам 10, по шине 13 записи поступает сигнал «запись. При этом срабатывает формирователь 8 пачек импульсов и на одном выходе появляется пачка из четырех импульсов (), а на другом выходе одновременно появляется пачка из трех импульсов. Под воздействием четырех импульсов, поступающих на тактовый вход регистров блока памяти через элемент 2 ИЛИ информация записывается в первые разряды регистров и продвигается далее до конечного, четвертого разряда. Пачка из трех импульсов поступает на тактовый вход счетчика 9 чисел. В связи с тем, что коэффициент счета счетчика равен в данном случае 4 ((4), фаза счетчика отстанет на один шаг от фазы блока памяти, определяемой местом первой записанной информации. Элемент 4 И не сработает, т. к. в момент действия сигнала с элемента 5 И присутствуют оба сигнала с выходов формирователя пачек импульсов, но в противофазе. Таким образом, чередующиеся сигналы записи и считывания позволяют осуществлять в данном устройстве последовательную запись и считывание информации в накопитель. При этом в динамическом режиме накопитель работает лишь при записи (Мтактовых импульсов) и считывании (один тактовый импульс), что позволяет сократить потребляемую мощность по сравнению с накопителями, работающими в непрерывном динамическом режиме. Другим преимуществом данного накопителя является возможность анализировать первую комбинацию сразу же после записи ее в накопитель, т. к. она появляется на выходе блока памяти сразу после цикла записи. Формула изобретения Буферное запоминающее устройство, содержащее блок памяти последовательного типа, информационные входы в исходы которого подключены соответственно к входным и выходным кодовым щинам, счетчик чисел, выходы которого подключены к соответствующим входам первого элемента И, выход которого подключен к управляющему входу блока памяти последовательного типа и входу второго элемента И, выход которого подключен к одному установочному входу триггера, другой установочный вход которого подключен к шине считывания, и тактовую шину, отличающееся тем, что, с целью снижения потребляемой мощности устройства, оно содержит два элемента ИЛИ, инвертер) и формирователь пачек импульсов, один из входов которого подключен к щине записи, другой вход - к тактовой шине, один из

выходов формирователя пачек импульсов подключеи ко входу первого элемента ИЛИ и входу второго элемента И, а выход первого элемента ИЛИ подключен к тактовому входу блока памяти последовательного типа, другой выход формирователя пачек импульсов подключен ко входу второго элемента ИЛИ и через инвертор ко входу второго элемента

И, другие входы первого и второго элементов ИЛИ подключены к шине считывания.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 493805, кл. G 11. С 7/00, 1974.

Авторы

Даты

1980-03-05—Публикация

1977-09-01—Подача