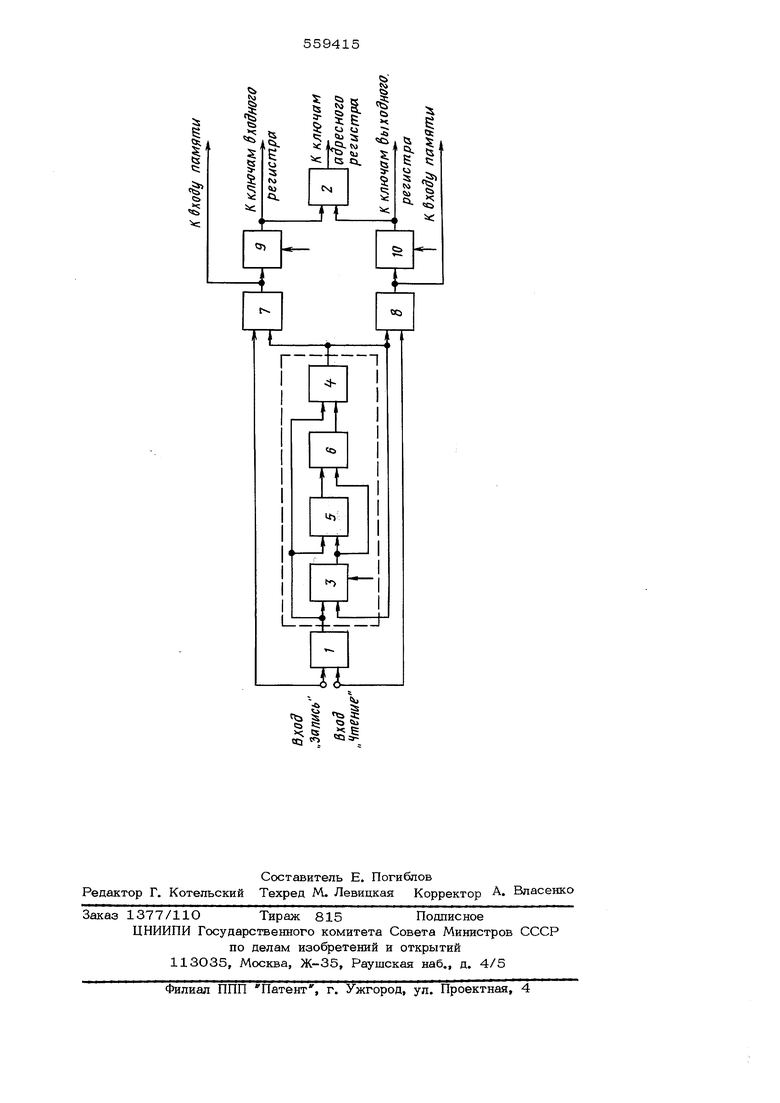

рой схемы совпадения 6 и к входу элемента задержки 5. К установочным входам три гера 4 и элемента задержки 5 подключен выход первого элемента ИЛИ 1. Устройство содержит также две цепи, каждая из которых состоит из последовательно соединенных элемента И 7 (8) и управляемого триггера 9 (1О). Один из входов каждого элемента И соединен с выходом триггера 4, а другой - с соответствующим входом первого элемента ИЛИ 1 выходы управляемых триггеров обеих цепей подключены к соответствующим входам второго элемента ИЛИ 2. При отсутствии сигналов на входах устроиства или при наличии сигналов помех с длительностью, меньшей длительности сигналов записи или чтения, сигналы на входы элементов И 7 и 8 не поступают Управляемые триггеры 9, 10 остаются в исходном состоянии, и с их выходов сигналы записи и чтения на входы управления памятью не поступают, ключи адресного , входного и выходного регистров закрыты. При поступлении сигналов на входы Запись и Чтение устройство работает следующим образом. Сигнал записи поступает на вход элемента И 7 и одновременно на вход элеме та ИЛИ 1. Сигнал с выхода последнего через схему совпадения 3, элемент задер

ки 5, схему совпадения 6 и триггер 4 поступает на вход элемента И 7. С выхода элемента И 7 сигнал в качестве управляющего поступает на вход памяти и одновременно - на управляемый триггер 9, выходной сигнал которого открывает ключи входного регистра и через элемент ИЛИ 2 - ключи адресного регистра.

Сигнал чтения, поступающий на вход элемента И 8, одновременно поступает на вход элемента ИЛИ 1, проходит через

вого элемента ИЛИ, выход которого подключен к соответствующему входу первой

схемы совпадения, а выходы управляемых триггеров обеих цепей подключены к соответствующим входам второго элемента ИЛИ.

Источники информации, принятые во вни-

мание при экспертизе:

1. Авторское свидетельство СССР. № 425366, М. Кл.Н 04 L 1/ОО, приоритет О 5.10.71 (прототип). схему совпадения 3, элемент задержки 5, схему совпадения 6 и триггер 4 и поступает на второй вход элемента И 8. С выхода элемента И 8 сигнал в качестве управляющего поступает на вход памяти и одновременно на вход управляемого триггера 10, выходной сигнал которого открывает ключи выходного регистра и через элемент ИЛИ 2 - ключи адресного регистра. Таким образом, стробирование ключей адресного, входного и выходного регистров памяти, а также устройств управления памятью производится сигналом, защищенным от импульсных помех, т. е, помехоустойчивый приеК (передача)осуществляется с помощью всего одного устройства. Это позволяет сократить объем оборудования и повысить надежность его работы. Формула изобретения Устройство для защиты от импульсных помех по авг. св. № 425366, о т л и чающееся тем, что, с целью повышения помехоустойчивости, в него введены первый и второй элементы ИЛИ и две цепи, каждая из которых состоит из последовательно соединенных элемента И и управляемого триггера, один вход элемента И каждой цепи соединен с выходом триггера, другой - с соответствующим входом пер

| название | год | авторы | номер документа |

|---|---|---|---|

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2099864C1 |

| Генератор многомерных случайных процессов | 1990 |

|

SU1755279A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1985 |

|

SU1259342A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090840C1 |

| Многоканальное устройство для ввода информации | 1989 |

|

SU1633383A1 |

| Устройство сопряжения разноскоростных асинхронных цифровых сигналов | 1988 |

|

SU1667266A1 |

| Устройство для сопряжения источника информации с процессором | 1990 |

|

SU1774341A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для контроля параметров | 1985 |

|

SU1298770A1 |

Авторы

Даты

1977-05-25—Публикация

1975-11-10—Подача