Изобретение относится к вычислительной технике и может быть использовано для ввода цифровой информации в процессор обработки в реальном или квазиреальном масштабе времени.

Известно устройство для сопряжения, содержащее блок памяти, буферный регистр, регистр уставки, сумматор, схему сравнения, мультиплексор, счетчики адресов записи и чтения, триггеры и шины записи и чтения, логические элементы И, Н Е, две линии задержки, входные и выходные шины

(И

Наиболее близким по технической сущности к заявляемому является устройство, содержащее дополнительно триггер слежения, второй и третий элементы И, элемент И-НЕ. Входы триггера подключены к выходам Больше и Меньше схемы сравнения, выходы - к первым входам элементов И, И-НЕ, вторые входы которых подключены к выходу Равно схемы сравнения. Выход элемента И-НЕ связан с вторым входом третьего элемента И, а выход второго элемента И соединен с входами установки в ноль обоих счетчиков. Выходы схемы сравнения Больше и Меньше отражают состояние счетчика записи относительно счетчика чтения. При равенстве кодов счетчиков на выходе Равно схемы сравнения появляется логическая 1. которая разблокирует второй элемент И и элемент И-НЕ, при этом в зависимости от предыдущего состояния счетчика записи, которое хранится в триггере слежения, определяется состояние блока памяти. Состояние Больше

1 4

4Ьь ОЭ

4

определяется как отсутствие информации в блоке памяти и при этом приводится сброс устройства в исходное состояние. Состояние Меньше определяется как полная загрузка блока памяти и при этом блокируется поступление информации в устройство 2.

При данной схеме подключения триггер слежения определяет ситуацию во всем диапазоне адресов от нулевого до максимального. Однако после записи информации по максимальному адресу счетчик записи естественным путем устанавливается на нулевой адрес, если в этот момент счетчик чтения находится также в нулевом состоянии (эта ситуация возникает, когда процессор допускает задержку в приеме первого информационного слова из устройства), то данная ситуация интерпретируется как отсутствие информации о блоке памяти, поскольку триггер слежения хранит состояние Больше, и соответственно происходит сброс устройства в исходное состояние. Таким образом, происходит потеря информации в объеме емкости блока памяти.

Цель изобретения - исключения потерь информации при полной загрузке блока памяти и нулевом состоянии счетчика чтения.

Цель достигается тем, что в устройстве, содержащем блок памяти, информационные входы которого соединены с пходны - ми шинами устройства, адресные входы - с выходами мультиплексора, а вход управления - с выходом второй линии задержки и входом сброса триггера записи, выходы блока памяти подключены к информационным входам буферного регистра, вход занесения которого связан со счетным входом счетчика чтения, первой шиной готовности и инверсным выходом триггера чтения, прямой выход последнего через первую линию задержки связан с первым входом первого элемента И, выход которого подключен к входу сброса триггера чтения, к входу установки последнего подключена шина чтения, а шина записи подключена к первому входу третьего элемента И, второй вход которого связан с выходом элемента И-НЕ, первый вход последнего соединен с прямым выходом триггера слежения, а второй вход - с вторым входом второго элемента И и выходом схемы сравнения, инверсный выход триггера слежения связан с первым входом второго элемента И, выход которого подключен к входам установки в ноль обоих счетчиков и элемента НЕ, выход последнего связан с вторым входом первого элемента И, третий вход которого связан с входом второй линии задержки и с инверсным выходом триггера записи, прямой выход последнего подключен к счетному входу

счетчика записи, кроме того, выходы триггера записи подключены к управляющим входам мультиплексора, а выходы счетчика записи связаны с первыми входами мультиплексора, сумматора и схемы сравнения, вторые входы которой связаны с вторыми входами мультиплексора и выходами счетчика чтения, вторые входы сумматора соединены с выходами регистра уставки, входы

0 которого связаны с выходными шинами интерфейса процессора, входные шины последнего соединены с выходами буферного регистра, причем выход третьего элемента И подключен к входу установки триггера

5 записи, а выход переноса сумматора - к второй шине готовности, вход установки триггера слежения связан с прямым выходом триггера записи, а вход сброса первого - с прямым выходом триггера чтения.

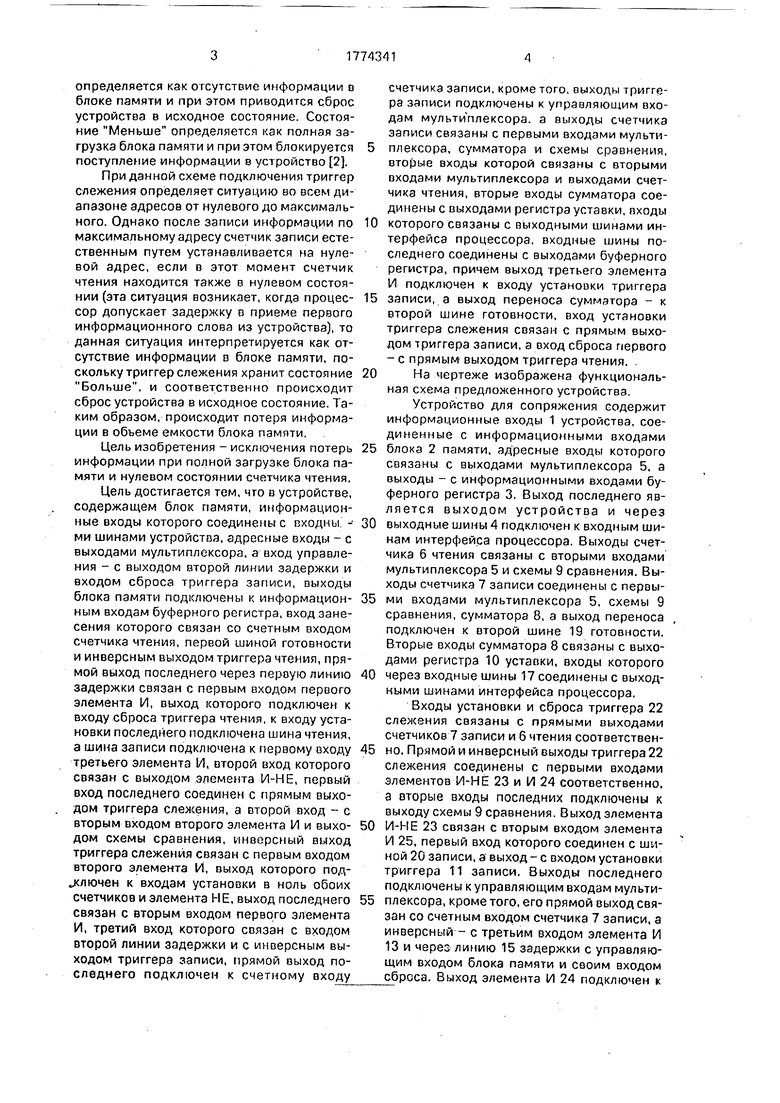

0На чертеже изображена функциональная схема предложенного устройства.

Устройство для сопряжения содержит информационные входы 1 устройства, соединенные с информационными входами

5 блока 2 памяти, адресные входы которого связаны с выходами мультиплексора 5, а выходы - с информационными входами буферного регистра 3. Выход последнего является выходом устройства и через

0 выходные шины 4 подключен к входным шинам интерфейса процессора. Выходы счетчика 6 чтения связаны с вторыми входами мультиплексора 5 и схемы 9 сравнения. Выходы счетчика 7 записи соединены с первы5 ми входами мультиплексора 5, схемы 9 сравнения, сумматора 8, а выход переноса подключен к второй шине 19 готовности. Вторые входы сумматора 8 связаны с выходами регистра 10 уставки, входы которого

0 через входные шины 17 соединены с выходными шинами интерфейса процессора.

Входы установки и сброса триггера 22 слежения связаны с прямыми выходами счетчиков 7 записи и б чтения соответствен5 но. Прямой и инверсный выходы триггера 22 слежения соединены с первыми входами элементов И-НЕ 23 и И 24 соответственно, а вторые входы последних подключены к выходу схемы 9 сравнения. Выход элемента

0 И-НЕ 23 связан с вторым входом элемента И 25, первый вход которого соединен с шиной 20 записи, а выход - с входом установки триггера 11 записи. Выходы последнего подключены к управляющим входам мульти5 плексора, кроме того, его прямой выход связан со счетным входом счетчика 7 записи, а инверсный - с третьим входом элемента И 13 и через линию 15 задержки с управляющим входом блока памяти и своим входом сброса. Выход элемента И 24 подключен к

входам установки в ноль счетчиков 6, 7 и входу элемента НЕ 16. выход которого связан с вторым входом элемента И 13. Выход последнего соединен с входом сброса триггера 12 чтения, вход установки которого подключен к шине 21 чтения, а прямой выход через линию 14 задержки связан с первым входом элемента И 13. Инверсный выход триггера 12 чтения соединен со счетным входом счетчика 6 чтения, входом занесения буферного регистра 3 и первой шиной 18 готовности.

Устройство работает следующим образом.

В исходном состоянии счетчики б, 7, триггеры 11, 22 находятся в состоянии О, триггер 12 - в состоянии 1. Элемент И 13 заперт логическим О с выхода элемента НЕ 16. Мультиплексор 5 подключен на направление счетчика 6 чтения. В регистр 10 уставки занесен из процессора дополнительный код глубины заполнения блока 2 памяти. На шинах 18, 19 готовности - логический О. Вторая шина 19 готовности включена в систему прерываний процессора. При поступлении на выходы 1 устройства первого информационного слова синхроимпульс его сопровождения поступает на шину 20 записи и через открытый элемент И 25 устанавливает триггер 11 записи в состояние Г. Последний переключает мультиплексор 5 на направление счетчика 7 записи и через вторую линию 15 задержки подает команду на управляющий вход блока 2 памяти, а затем сбрасывается в исходное состояние О. Элемент И 13, находящийся в цепи чтения, на время операции записи блокируется сигналом с инверсного выхода триггера 11, что делает невозможным чтение из блока 2 памяти.

Задний фронт сигнала с прямого выхода триггера 11 поступает на счетный вход счетчика 7 записи и наращивает его состояние на единицу, подготавливая тем самым следующие адрес для блока 2 памяти. Вследствие увеличения кода счетчика 7 на выходе схемы 9 сравнения появится логический О, который блокирует элементы И-НЕ 23 и 24. Сигнал с выхода последнего поступает на вход элемента НЕ 16, на выходе которого появляется логическая 1, поступает на второй вход элемента И 13 и разблокирует его. Сигнал с выхода последнего поступает на вход сброса триггера 12 и устанавливает его в состояние О. Передний фронт сигнала с инверсного выхода последнего поступает на вход занесения буферного регистра 3, и информация из блока памяти переписывается в буферный регистр 3, при этом на первой шине готовности появляется логическая 1, сообщая процессору о наличии информации в устройстве. Второе и последующие информационные слова, поступающие в устройство, числом не более чем задано в регистре 10, записываются в блок памяти аналогично. В этот период процессор, если он освободился от решения других задач, анализирует состояние первой шины 18 готовности, и в

0 случае наличия логической 1 на последней снимает информацию с выходных шин 4 буферного регистра 3. Строб приема информации в процессор поступает по шине 21 чтения на вход установки триггера 12 чтения

5 и устанавливает его в состояние 1. При этом сигнал с инверсного выхода триггера 12 поступает на счетный вход счетчика 6 чтения и наращивает его состояние на единицу. Прямой выход триггера 12 через ли0 нию 14 задержки выставляет запрос на вывод очередного слова из блока 2 памяти в буферный регистр 3. Если в блоке памяти есть информация и в этот момент не идет операция записи, то запрос удовлетворяет5 ся, сигнал с выхода элемента И 13 сбрасывает в ноль триггер 12 чтения, следующее слово переписывается в буферный регистр 3 и снова по шине 18 возникает сигнал готовности. По сигналам на первой шине го0 товности процессор может принять всю информацию из устройства или только ее часть (возможно, нулевую). В последнем случае при заполнении блока памяти до уровня, заданного в регистре 10 уставки, на

5 выходе переноса сумматора 8, который вычитает из кода счетчика 7 записи код, занесенный в регистр 10, возникает логическая 1. Последняя по второй шине 19 готовности поступает в систему прерываний про0 цессора и вызывает на выполнение программу приема из устройства, которая, как было выше описано, считывает всю информацию из устройства до конца. При съеме последнего слова с выходных шин 4

5 вследствие равенства кодов счетчиков на выходе схемы 9 сравнения появляется логическая 1м, которая открывает логические элементы И-НЕ 23 и И 24. Так как последней операцией была операция чтения из устрой0 ства, то триггер 22 слежения находится в состоянии О и сигнал с его инверсного выхода через открытый элемент И 24 поступает на вход установки в ноль счетчиков 6, 7 и элемента НЕ 16. Таким образом, устрой5 ство установлено в исходное состояние. В случае, если процессор игнорировал сигналы на первой шине 18 готовности и в регистре 10 уставки задана максимальная глубина заполнения блока 2 памяти, то после записи по максимальному адресу счетчик 7 записи устанавливается на минимальный адрес и сигнал равенства с выхода схемы 9 сравнения отрывает элементы И-НЕ 23, И 24. Так как триггер 22 слежения находится при этом в состоянии 1, то логический О с выхода элемента И-НЕ 23 закрывает элемент И 25 и запись в устройство приостанавливается до считывания из устройства хотя бы одного слова. Если время реакции процессора на прерывание меньше периода следования синхроимпульсов записи, то потери информации не происходит, если больше, то не следует задавать максимальную глубину заполнения блока памяти.

Триггер слежения хранит информацию о том, какая операция предшествовала ситуации равенства кодов счетчиков, и позволяет правильно оценить состояние блока памяти устройства в любой точке адресного пространства последнего. При одновременном поступлении синхроимпульсов записи и чтения из устройства состояние триггера слежения неопределенно, но это не искажает логику работы устройства, так как в этот момент равенства счетчиков быть не может, т.е. ситуация не изменяется, один пришал, один ушел. Первый пришедший после совпадения запросов к устройству одиночный импульс восстанавливает истинное положение триггера слежения.

Формула изобретения Устройство для сопряжения источника информации с процессором, содержащее счетчики записи и чтения, триггеры слежения, записи и чтения, блок памяти, соединенный выходом с информационным входом буферного регистра, выход которого и инверсный выходи вход установки триггера чтения являются соответствующими выходами и входом устройства, для подключения к информационному входу и синхронизирующим входу и выходу процессора, мультиплексор, сумматор и схему сравнения, первые информационные входы которых подключены к выходу счетчика записи, три элемента И, элемент НЕ, элемент И-НЕ, два элемента задержки и регистр уставки, информационный вход которого является входом устройства для подключения к информационному выходу процессора, а выход соединен с вторым информационным входом сумматора, причем первый оход

первого элемента И соединен через первый элемент задержки с прямым выходом триггера чтения, входом сброса подключенного к выходу первого элемента И, а инверсным выходом - к входу занесения буферного регистра к счетному входу счетчика чтения, выход которого соединен с вторыми информационными входами схемы сравнения и мультиплексора, инверсный выход триггера слежения соединен с первым входом второго элемента И, выход которого подключен к входам сброса счетчиков записи и чтения и через элемент НЕ -к второму входу первого элемента И, третьим входом соединенного с инверсным выходом триггера записи и через второй элемент задержки - с управляющим входом блока памяти и входом сброса триггера записи, установочный вход которого подключен к выходу третьего элемента И, первый и второй входы которого

соединены соответственно с входом устройства для подключения к синхронизирующему выходу источника информации и выходам элемента И-НЕ, первым входом подключенного к прямому выходу триггера

слежения, а вторым входом - к выходу схемы сравнения и второму входу второго элемента И, счетный вход счетчика записи соединен с прямым выходом триггера записи, прямой и инверсный выходы которого

соединены соответственно с первым и вторым управляющими входами мультиплексора, выходом подключенного к адресному входу блока памяти, информационный вход которого и выход переноса сумматора является соответственно входом и выходом устройства для подключения к информационному выходу и входу синхронизации источника информации, отличающееся тем, что, с целью исключения потерь информации при

полной загрузке блока памяти и нулевом состоянии счетчика чтения, в устройстве установочный вход и вход сброса триггера слежения соединены соответственно с прямыми выходами триггера записи и триггера

чтения.

И

Я

:1т г/

/а

,Изобретение относится к вычислительной технике и может быть использовано для ввода в процессор цифровой информации в реальном масштабе времени или предварительно записанной-на магнитный носитель. Цель изобретения - повышение достоверности работы устройства путем исключения потерь информации при полной загрузке блока памяти и нулевом состоянии счетчика чтения. Цель достигается тем, что в устройстве, содержащем блок памяти, мультиплексор, счетчики и триггеры записи и чтения, триггер слежения, буферный регистр, сумматор, регистр уставки, схему сравнения, три элемента И, элементы И-НЕ, НЕ и две линии задержки, установочные входы триггера слежения соединены соответственно с прямыми выходами триггера записи и триггера чтения. 1 ил. Ё

П

L-A

15

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения источника информации с процессором | 1988 |

|

SU1571601A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения источника информации с процессором | 1989 |

|

SU1658162A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-11-07—Публикация

1990-02-22—Подача