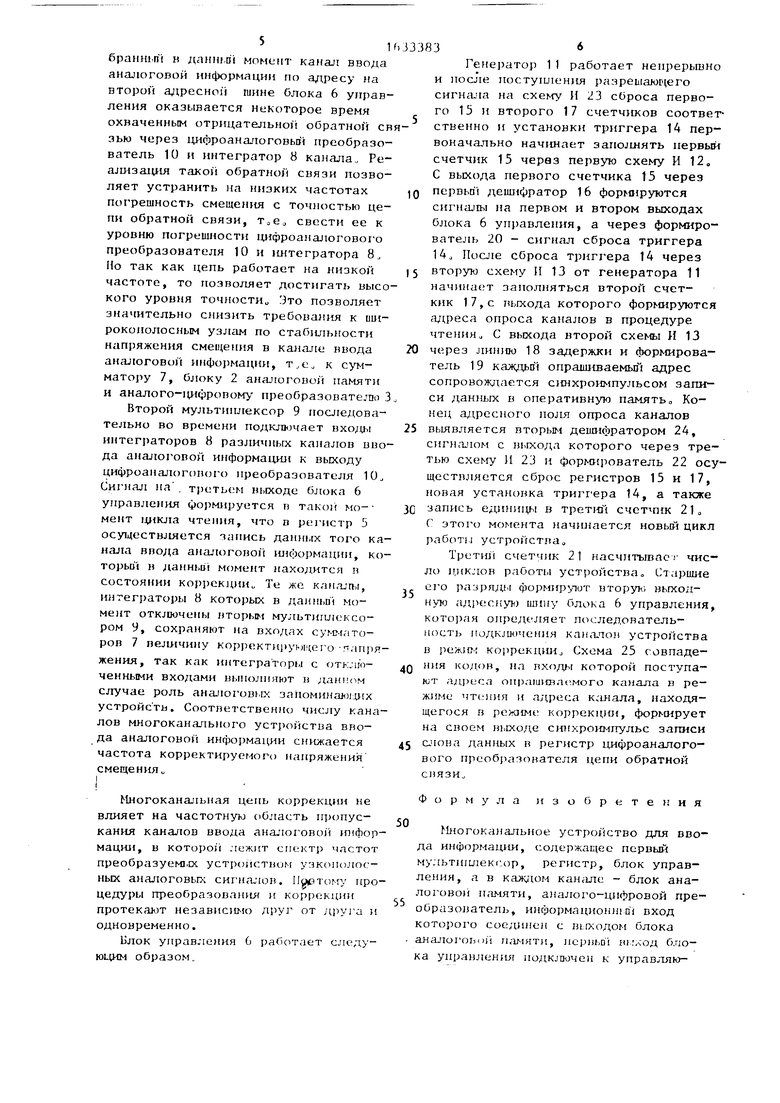

телыю - сумматор 7 и интегратор 8, устройство содержит дополнительно второй мультиплексор 9 и цифроанало- говый преобразователь 10„

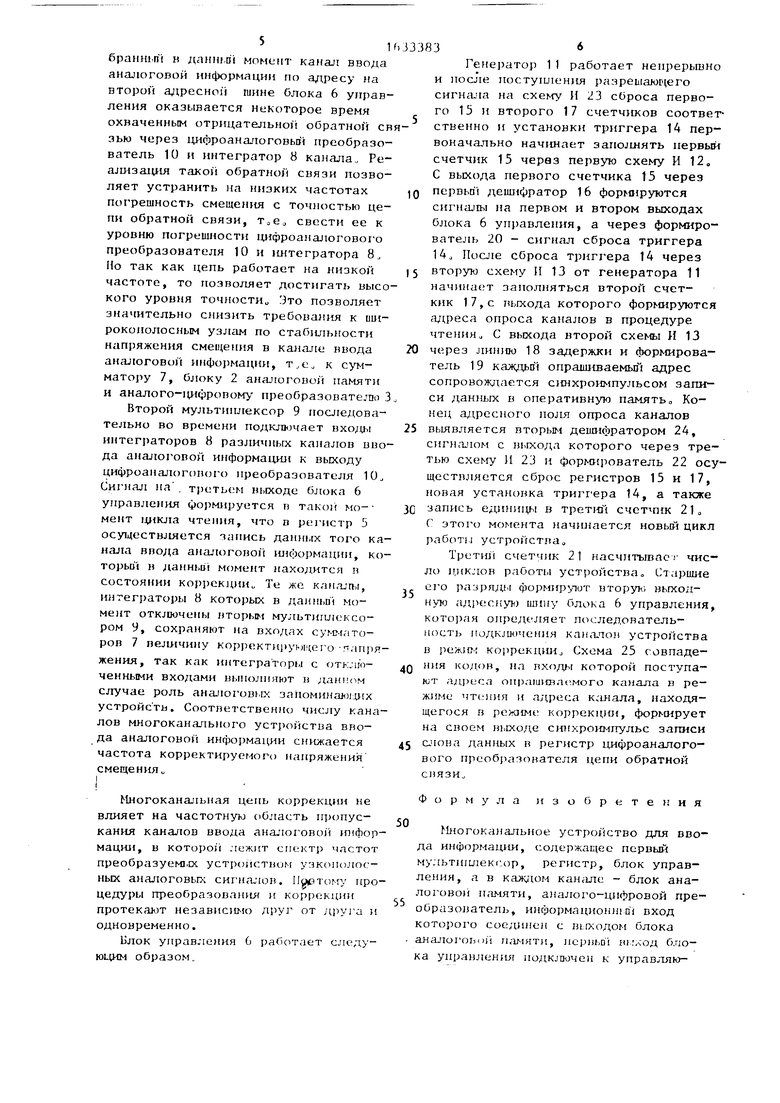

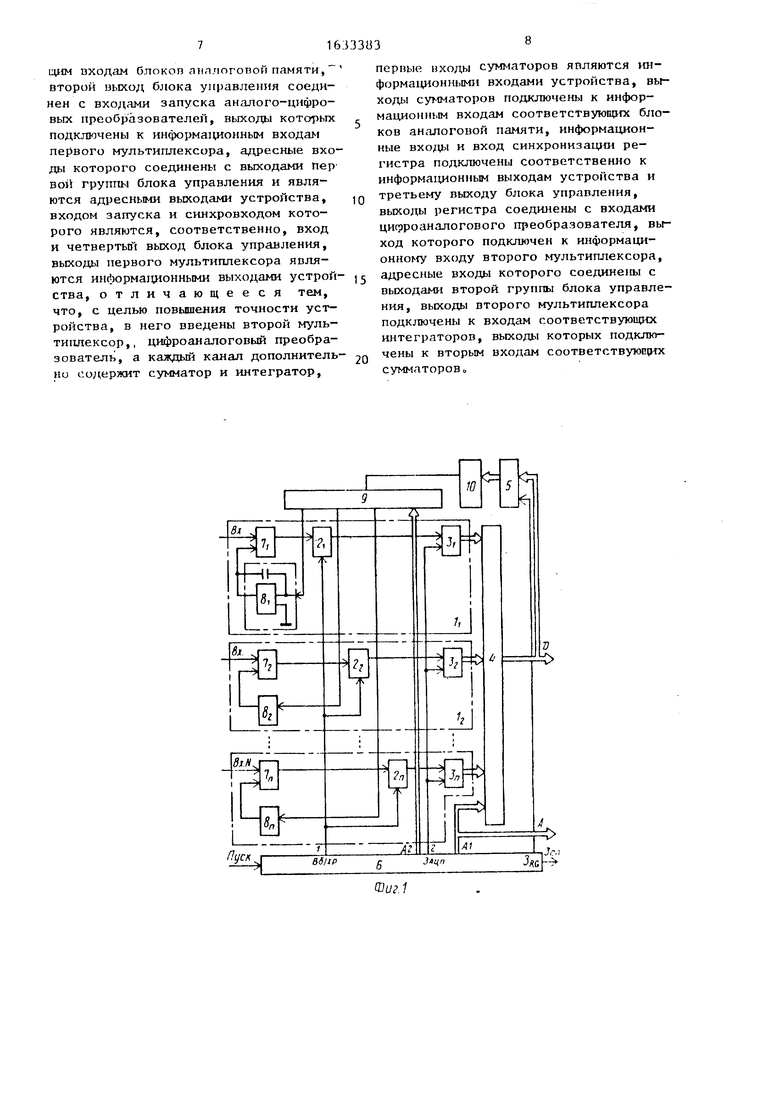

В блоке 6 управления выход тактового генератора 11 подключен к первым входам первой 12 и второй 13 схем И, вторые входы которых соединены соответственно с прямым и инверсным выходом триггера 14, выход первой схемы И 12 соединен.со счетным входом первого счетчика 15, выходы которого подключены к входам первого дешифратора 16, а выход второй схемы И 13 соединен со счетным входом второго счетчика 17 и через линию 18 задержки и формирователь 19 поступает на выход блока 6 управления на шину Запись в оперативную память Первый выход первого дешифратора 16 является первым выходом блока 6 управления, второй выход первого дешифратора 16 является вторым выходом блока 6 управления, а третий через второй формирователь 20 подключен к установочному входу триггера 14, единичный вход которого соединен с установочными входами первого 15 и второго 16 счетчиков, со счетным входом третьего счетчика 21 и подключен к выходу третьего формирователя 22, вход которого соединен с выходом третьей схемы И 23, первый вход которой соединен с выходом второго дешифратора 24, а второй является управляющим входом блока 6 управления. Выход второго счетчика 17 является выходной шиной адреса блока 6 управления, а также соединен с входом вто- рого дешифратора 24 и с первым входом схемы 25 совпадения кодов, выход которой является третьим выходом блока 6 управления, а второй вход соединен с группой старших разрядов третьего счетчика 21, которая одновременно является второй выходной шиной адреса блока 6 управления.

Устройство работает следующим образом.

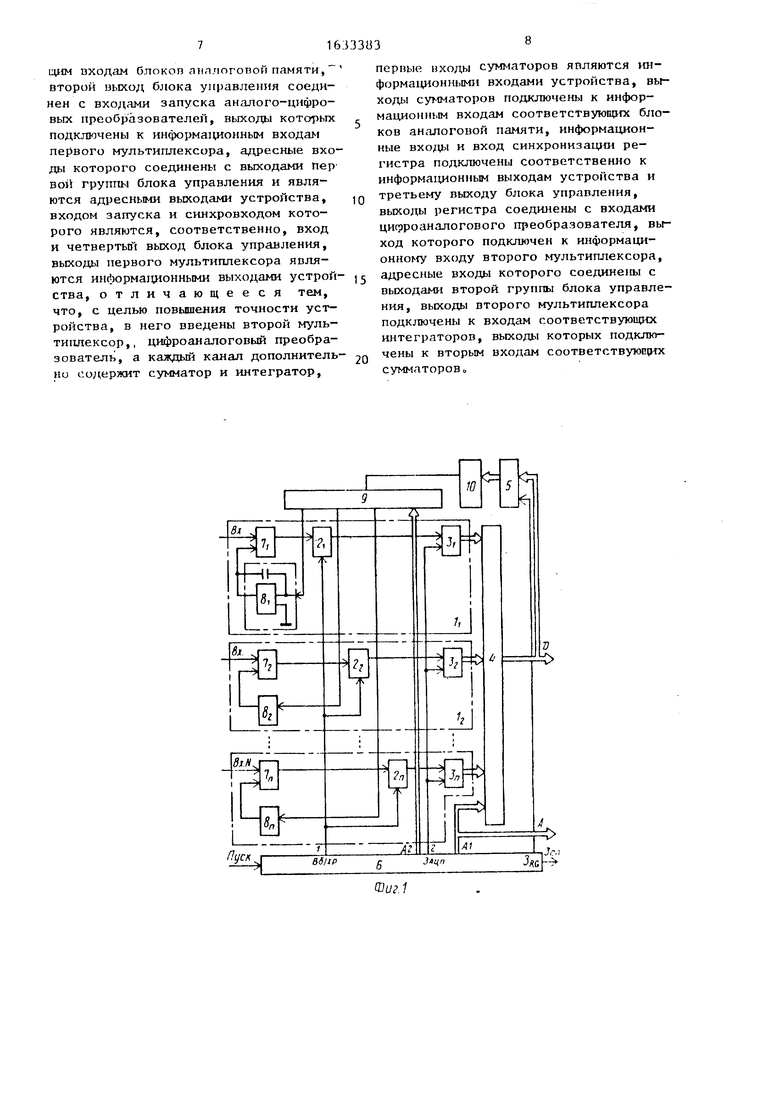

При наличии разрешающего потенциала на управляющем входе блока 6 управления (фиг.З) на ее первом выходе формируется импульс управления выборкой блоков 2 аналоговой памяти одновременно по всем каналам ввода аналоговой информациио Осуществляется выборка уровня аналоговых сигналов по всем каналамо Причем аналоговые

0

Q 5 ,

0

5

45

50

55

сигналы поступают на входы блоков 2 через сумматоры 7 в каждом канале, где к узкополосному входному сигналу добавляется постоянное напряжение равное приведенному к входу напряжению смещения тракта преобразования, но с обратным знакомо

После завершения процедуры выборки с второго выхода блока 6 управления вырабатывается сигнал запуска аналого-цифровых преобразователей, который подается на управляющие входы всех аналого-цифровых преобразователей 3 одновременно всех каналов ввода аналоговой информации„ После процедуры кодирования на выходной адресной шине блока 6 управления последовательно начинают формироваться адреса каналов многоканального устройства ввода данных. Эти адреса управляют мультиплексором 4, который последовательно подключает выходы аналого- цифровых преобразователей 3 каналов ввода аналоговых данных к выходной шине данных устройства,, Одновременно блок 6 управления формирует синхроимпульс сопровождения адреса канала на выходной шине адреса и дан- . ных по каналу на выходной шине дан- . ных„ Таким образом осуществляется процедура чтения данных,. После процедуры чтения цикл работы устройства повторяетсяс

Параллельно с механизмом преобразования и чтения данных по каналам работает механизм коррекции погрешности смещения по каналам Сущность работы механизма коррекции погрешности смещения заключается в следующем По адресу на второй адресной шине блока 6 управления второй мультиплексор 9 последовательно подключает выход цифроаналогового преобразователя 10 к входам интеграторов 8 в каналах ввода аналоговой информа- циио Причем время подключения каждот го канала значительно превосходит цикл работы устройства преобразования и ввода,, Например, за время подключения интегратора 81 1-го канала долхно осуществиться не менее 1024 кодирований по Kanajry. Одновременно с третьего выхода блока 6 управления осуществляется запись данных в регистр 5 только с выхода того . канала, интегратор которого в данный момент подключен к выходу второго мультиплексора 90 Таким образом, вы

бранный в данный момент канал ввода аналоговой информации по адресу на второй адресной шине блока 6 управления оказывается некоторое время охваченным отрицательной обратной свзью через цифроаналоговын преобразователь 10 и интегратор 8 канала„ Реализация такой обратной связи позволяет устранить на низких частотах погрешность смещения с точностью цепи обратной связи, т0е0 свести ее к уровню погрешности цифроаналогового преобразователя 10 и интегратора 8, Но так как цепь работает на низкой частоте, то позволяет достигать высокого уровня точности Это позволяет значительно снизить требования к широкополосным узлам по стабильности напряжения смещения в канале ввода аналоговой информации, т,е„ к сумматору 7, блоку 2 аналоговой памяти и аналого-цифровому преобразователю 3

Второй мультиплексор 9 последовательно во времени подключает входа интеграторов 8 различных каналов ввода аналоговой информации к выходу цифроаналогового преобразователя 10., Сигнал на . третьем выходе блока 6 управления формируется в такой мо- мент цикла чтения, что в регистр 5 осуществляется запись данных того канала ввода аналоговой информации, который в даннми момент находится в состоянии коррекции., Те же каналы, интеграторы 8 которых в данный момент отключены вторым мультиплексором У, сохраняют на входах сумматоров 7 величину корректирующего -папря- жения, так как интеграторы с отключенными входами выполняют в данном случае роль аналоговых запоминающих устройств. Соответственно числу каналов многоканального устройства ввода аналоговой информации снижается частота корректируемого напряжения смещения„

Многоканальная цепь коррекции не влияет на частотную область пропускания каналов ввода аналоговой информации, в которой лежит спектр частот преобразуемых устройством узкополог- ных аналоговых сигналов. Поэтому процедуры преобразования и коррекции протекают независимо друг от друга и одновременно.

управления 6 работает следу- юцим образом.

15

20

JQ

5 30 5

35

0

0

5

Генератор 11 работает непрерывно и после поступления разреыанщего сигнала на схему И 23 сброса первого 15 и второго 17 счетчиков соответственно и установки триггера 14 первоначально начинает заполнять первый счетчик 15 через первую схему И 12„ С выхода первого счетчика 15 через первый дешифратор 16 формируются сигналы на первом и втором выходах блока 6 управления, а через формирователь 20 - сигнал сброса триггера 14„ После сброса триггера 14 через вторую схему И 13 от генератора 11 начинает заполняться второй счет- кик 17,с выхода которого формируются адреса опроса каналов в процедуре чтения о С выхода второй схемы И 13 через линию 18 задержки и формирователь 19 каждый опрашиваемый адрес сопровождается синхроимпульсом записи данных в оперативную память Конец адресного поля опроса каналов выявляется вторым дешифратором 24, сигналом с выхода которого через третью схему И 23 и формирователь 22 осуществляется сброс регистров 15 и 17, новая установка триггера 14, а также запись единицы в третий счетчик 21„ Г этого момента начинается новый цикл работы устройства

Третий счетчик 21 насчитываем1 число циклов работы устройства„ Старшие его разряды формируют вторую выходную адресную шипу блока 6 управления, которая определяет последовательность подключения капало} устройства в режим коррекции0 Схема 25 совпадения кодов, на входы которой поступают адреса опрашиваемого канала в режиме чтения и адреса к:шала, находящегося в режиме коррекции, формирует на своем выходе синхроимпульс записи слова данных в регистр цифроаналогового преобразователя цепи обратной снязи„

Формула изобретения

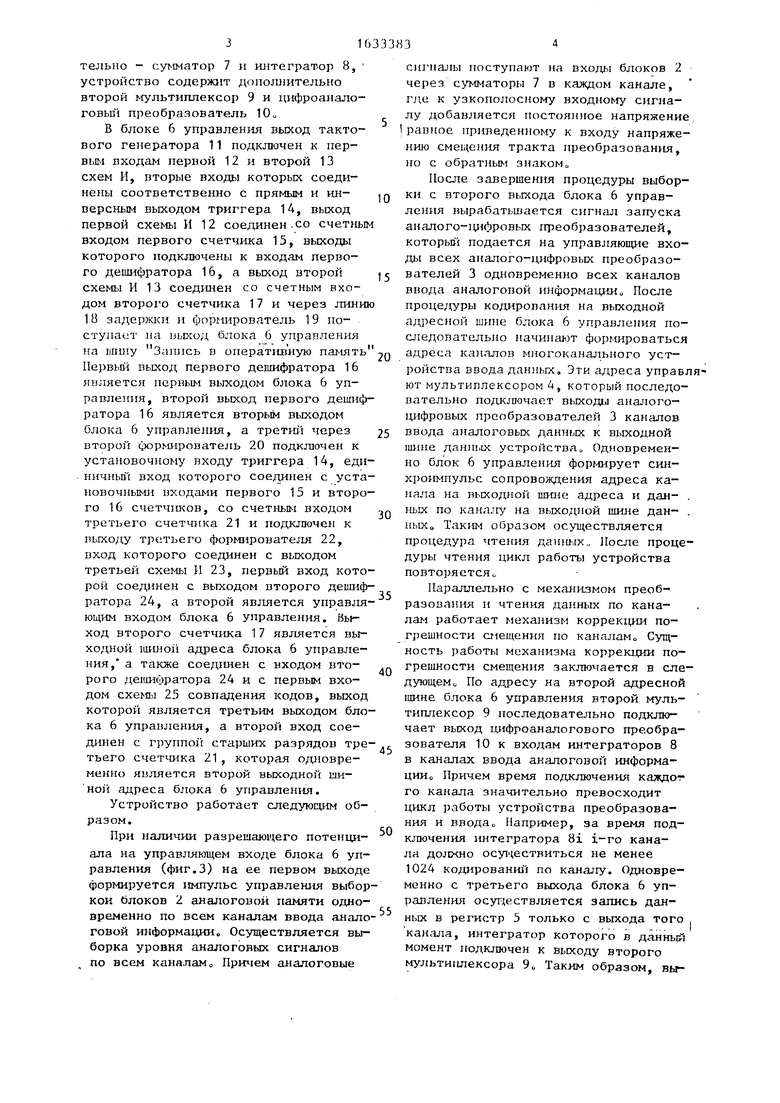

Многоканальное устройство для ввода информации, содержащее первый мультиплексор, регистр, блок управления, а в каждом канале - блок аналоговой памяти, аналого-цифровой преобразователь, информационный вход которого соединен с выходом блока аналоговой памяти, первый выход блока управления подключен к управляю1днм входам блокоп анллоговой памяти, второй выход блока управления соединен с входами запуска аналого-цифровых преобразователей, выходы которых подключены к информационным входам первого мультиплексора, адресные входы которого соединены с выходами первой группы блока управления и являются адресными выходами устройства, входом запуска и синхровходом которого являются, соответственно, вход и четвертый выход блока управления, выходы первого мультиплексора являются информационными выходами устрой- ства, отличающееся тем, что, с целью повышения точности устройства, в него введены второй мультиплексор,, цифроаналоговый преобразователь, а каждый канал дополнитель- но содержит сумматор и интегратор,

первые входы сумматоров являются информационными входами устройства, выходы сумматоров подключены к информационным входам соответствующих блоков аналоговой памяти, информационные входы и вход синхронизации регистра подключены соответственно к информационным выходам устройства и третьему выходу блока управления, выходы регистра соединены с входами цисрроаналогового преобразователя, выход которого подключен к информационному входу второго мультиплексора, адресные входы которого соединены с выходами второй группы блока управления, выходы второго мультиплексора подключены к входам соответствующих интеграторов, выходы которых подключены к вторым входам соответствующих сумматоров о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Установка для акустико-эмиссионного контроля | 1986 |

|

SU1452316A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для ввода информации | 1988 |

|

SU1665362A1 |

| Устройство для многоканальной записи аналоговых процессов | 1985 |

|

SU1304070A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и в устройствах цифровой обработки сигналов. Цель изобретения - повышение точности устройст- Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и в устройствах цифровой обработки сигналов. Целью изобретения является повышение точности устройства. На фиг.1 представлена структурная схема устройства; на фиг.2 - структурная схема блока управления, . на ва. Цель достигается тем, что в устройство, содержащее п каналов 1i лво- да аналоговой информации, каждый из которых содержит блок 21 аналоговой памяти и аналого-цифровой преобразователь 31, а также первый мультиплексор 4, регистр 5 и блок 6 управления, введены второй мультиплексор 9 и цифроаналоговый преобразователь 10, а в каждый канал 11 ввода аналоговой информации - сумматор 71 и интегратор 81„ Повышение точности многоканального устройства ввода достигается за счет частотного разделения полезного сигнала помехи. Коррекция сигнала помехи осуществляется независимо от основного сигнала и происходит одновременно с работой канала преобразования информации. Применение контура коррекции в низкочастотной области передаточной характеристики канала позволяет исключить погрешность напряжения смещения аналоговых блоков канала преобразования информации и тем самым повысить точность устройства. 3 ил. ю (Л фиг.З - временная диаграмма работы устройства. Многоканальное устройство ввода узкополостных сигналов содержит п каналов Н ввода аналоговой информации (), каждый из которых содержит блок 2 аналоговой памяти и ана- . лого-цифровой преобразователь 3, мультиплексор 4, регистр 5 и блок 6 управления, а в каждом канале дополни- О СО СО СО 00 со

Jf

л;

О

-Л

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1985 |

|

SU1339892A1 |

| Патент США № 4651131, i кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Чернов В.Г | |||

| Устройства ввода-вывода аналоговой информации для цифровых систем сбора и обработки данных | |||

| - М.: Машиностроение, 1988, с | |||

| Переносная печь-плита | 1920 |

|

SU184A1 |

Авторы

Даты

1991-03-07—Публикация

1989-04-11—Подача