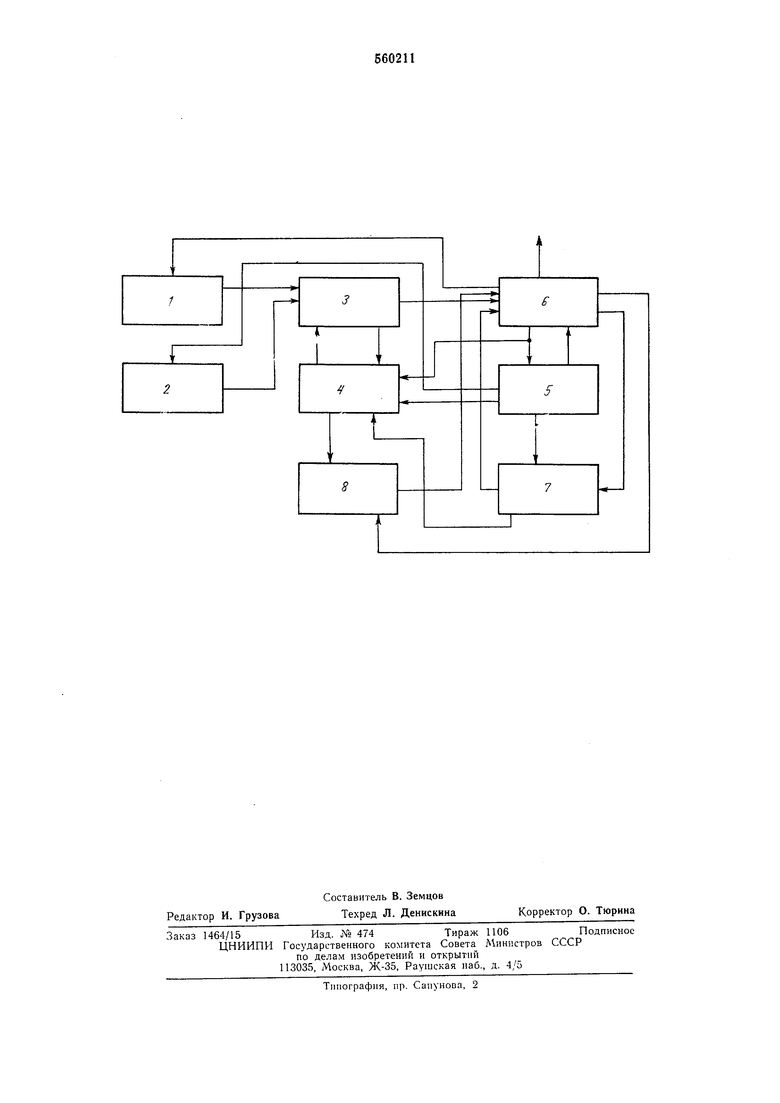

Устройство содержит блок 1 задания программы с перфоленты, блок 2 коррекции, блок 3 логических вычислений, блок 4 оперативной памяти, блок 5 памяти алгоритмов, блок б управления, блок 7 коммутации микрокоманд, блок 8 индикации. Управляющие сигналы поступают циклически из блока 6 упрваления в блок 5 памяти алгоритмов. По сигналам блока памяти алгоритмов блоком 1 считываются кадры программы управления стаиком. Работает устройство в режиме автоконтроля управляющих алгоритмов следующим образом. |1о1сле обработки очередного запроса от станка и освобождения блоков 3-5 управление передается схеме диспетчера в блоке 5 паДШти алгоритмов. При этом контролируется наличие в блоке 5 эталонного и контролируемого алгоритмов. Ьсли эталонный и контролируемый алгоритмы находятся в блоке 5, то схема диспетчера подготавливает схему клапанирования блока 7 к приему иерсой микрокоманды эталонного алгоритма. После того как диспетчер получит подтверждение из блока управления о готовности блока 7 коммутации микрокоманд к приему, в буферный регистр блока 7 считывается первая микрокоманда эталонной программы. В конце приема микропрограммы блок 7 вырабатывает сигнал «заирет приема и сбрасывает в исходное состояние схему планирования. Кроме того, блок 7 подает сигнал, инициатирующий схему диспетчера блока 5 на иередачу содержимого блока 7 в свободные ячейки блока 4 оперативной памяти. После завершения цикла передачи содержимого блока 7 коммутации микрокоманд в блок 4 оиеративиой памяти, схема диспетчера подготавливает схему клаианирования олока 7 к приему иервой микрокоманды контролируемого алгоритма. Полный цикл передачи микрокоманды контролируемого алгоритма из блока 5 памяти алгоритмов в блок 4 оперативной памяти идентичен циклу передачи микрокоманды эталонного алгоритма. После того как микрокоманды эталонного и контролируемого алгоритмов оказываются в блоке оперативной намяти, схема дисиетчера передает управление блоку 3 логических вычислений, где проводится поразрядное сравнение микрокоманд ио схеме «исключающее или (Т): Л(6)А (6)ЕО, где Л - микрокоманда эталонного алгоритма;А - микрокоманда контролируемого алгоритма;b - число разрядов. В случае появления единицы в результате сравнения какого-либо разряда схема диспетчера передает управление блоку 8 индикации. Блок индикации печатает содержимое микрокоманды с указанием ее адреса в блоке о хранения алгоритмов и номера разряда, ио которому произощло несовпадение. При совпадении всех разрядов (вырабатывается код «и по всем разрядам) весь цикл начинается сначала со следующими микрокомандами эталонного и контролируемого алгоритмов. Введение блока коммутации микрокоманд выгодно отличает предлагаемое устройство числового программного управления от .прототипа, так как позволяет расширить область применения устройства и повысить надежность его работы со станком. Формула изобретения Устройство для числового программного управления, содержащее блок задания программы, блек логических вычислений, блок управления, блок памяти алгоритмов, блок коррекции, блок индикации и блок оиеративной памяти, первый вход которого иодключен к иервому выходу блока логических вычислений, иервый выход блока оперативной памяти подключен к первому входу блока логических вычислений, второй выход - к первому входу блока индикации, выход которого соединей с нервым входом блока управления, второй вход которого подключен к второму выходу блока логических вычислений, второй вход которого подключен к выходу блока коррекции, вход которого соединен с первым выходом блока иамяти алгоритмов, вход которого иодключен к первому выходу блока управления и второму входу блока оперативной иамяти, второй выход блока памяти алгоритмов подключен к третьему входу блока управления, иервый выход когорого иодключен к входу блока задания программы, выход которого подключен к третьему входу блока логических вычислений, отличающееся тем, что, с целью расщирения области применения устройства, оно содержит блок коммутации микрокоманд, первый вход которого соединен с третьим выходом блока памяти алгоритмов, четвертый выход которого подключен к третьему входу блока оперативной памяти, второй вход блока коммутации микрокоманд соединен с вторым выходом блока управления, первый выход блока коммутации микрокоманд иодключен к четвертому входу блока оиеративной памяти, а второй выход -юдллючен к четвертому входу блока управления, третий выход которого иодключен к второму входу блока индикации. Источники информации, принятые во внпмание при эксиертизе: 1. Гусев А. П. и др. Групповое управление станками от ЦВМ. М., «Машиностроение, 1974, с. 149. 2. Авт. св. № 354401, кл. G 05В 19/18, 1970 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для числового программного управления станками | 1975 |

|

SU732813A1 |

| Устройство для тестового контроля больших интегральных схем | 1984 |

|

SU1218390A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для диагностики абонентов вычислительной сети | 1989 |

|

SU1679488A1 |

| Имитатор канала | 1991 |

|

SU1839250A2 |

| Однородный параллельный процессор | 1978 |

|

SU736107A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Пневматическое устройство для централизованного контроля | 1973 |

|

SU452823A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля тестопригодных программ | 1990 |

|

SU1751767A1 |

Авторы

Даты

1977-05-30—Публикация

1976-01-29—Подача