I

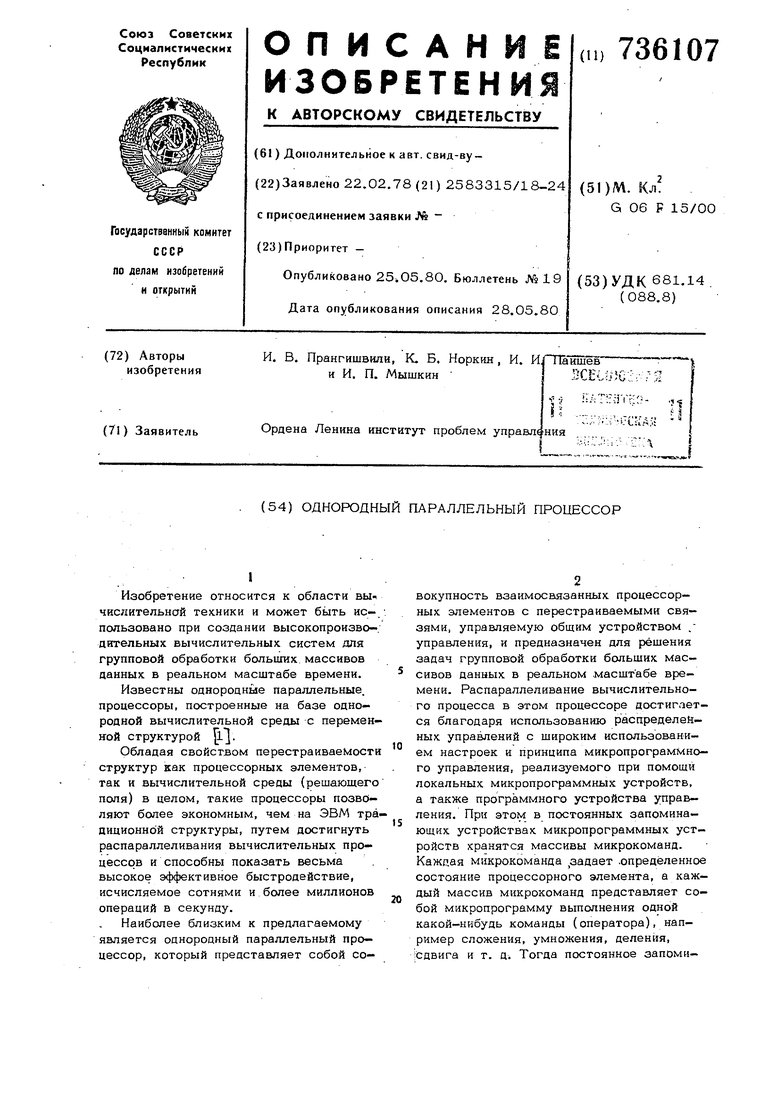

Изобретение относится к области вычислительной техники и может быть ис-/ пользовано при создании высокопроизво-. дительных вычислительных систем для групповой обработки больших массивов данных в реальном масштабе времени.

Известны однородные параллельные, процессоры, построенные на базе однородной вычислительной среды с переменкой структурой ji.

Обладая свойством перестраиваемости структур как процессорных элементов, так и вычислительной среды (решающего поля) в целом, такие процессоры позволяют более экономным, чем на ЭВМ традиционной структуры, путем достигнуть распараллеливания вычислительных процессов и способны показать весьма высокое эффективное быстродействие, исчисляемое сотнями и более миллионов операций в секунду.

Наиболее близким к предлагаемому является однородный параллельный процессор, который представляет собой со-

вокупность взаимосвязанных процессорных элементов с перестраиваемыми связями, управляемую общим устройством .управления, и предназначен для решения задач групповой обработки больших массивов данных в реальном .масштабе времени. Распараллеливание вычислительного процесса в этом процессоре достигается благодаря использованию распределенных управлений с широким использованием настроек и принципа микропрограммного управления, реализуемого при помощи локальных микропрограммных устройств, а также программного устройства управления. При этом в постоянных запоминающих устройствах микропрограммных устройств хранятся массивы микрокоманд. Кажпая микрокоманда задает .определенное состояние процессорного элемента, а каждый массив микрокоманд представляет собой микропрограмму выполнения одной какой-нибудь команды (оператора), например сложения, умножения, деления, Ъдвига и т. д. Тогда постоянное запоми37нающее устройство должно содержать столько массивов, сколько команд содержит система команд данного процессора, а размерность управляющего слова (микрокоманды) в массиве определяется числом точек управления процессорным элементом и количеством сопровождающей служебной информации. При этом одни и те же микрокоманды (состояния микропроцессора) могут многократно входить различные микропрограммы, поэтому они будут записаны в память микропрограммного устройства столько раз, сколько раз встречаются в массивах микрокоманд . (микропрограммах) 21. Существенный недостаток такой схемы управления состоит в том, что для ее реализации необходимости многократной записи микрокоманд требуется неоправданно завышенный объем постоянного запоминающего устройства. Цель изобретения - уменьшение объем постоянных запоминающих устройств, тре бующихся для реализации микропрограммного управления параллельным процессором. Указанная цель достигается тем, что в известный однородный параллельный процессор, содержащий блок программного управления, л устройств обработки данных, каждое из которых содержит входной регистр, блок оперативных регистров, выходной регистр, блок управляемых элементов И, арифметико-логический блок и блок микропрограммного управления, причем первый вход входного регистра каждого устройства обработки даннъЕХ соединен с соответствующим выходом блока коммутации, а выход вход ного регистра подключен к первому входу блока управляемых элементов И, первый вход - выход которого соединен с выходом - входом блока оперативных регистров, второй вход-выход блока управления элементов И подключен к выходу - входу арифметико-логического блока, первъй выход которого соединен с первым входом блока микропрограммно го управления, а второй вькод арифметико-логического блока подключен к первому входу выходного регистра, а выход выходного регистра каждого устройства обработки данных подключен к соответст вующему входу блока коммутации, выход блока микропрограммного управления каж дого устройства обработки данньрс подклю чен к соответствующему входу блока про раммного управления, первый вход-выход 7 которого является входом-выходом процессора, вход блока приема информации является входом процессора, а вьсход блока приема информации подключен к ин- формацион}1ому входу блока коммутации, а выход блока диспетчеризации соединен с управляющими входами блока приема инфqэмaции, блока программного управления и блока микропрограммного управления каждого устройства обработки данныХ; введен блок памяти, а в каждое устройство обработки данных введена постоянная память, при этом вход- выход постоянной памяти соединен со входом-выходом блока микропрограммного управления, первый выход постоянной памяти подключен ко второму входу входного регистра, второй выход постоянной памяти подключен ко второму входу блока управляемых элементов И, третий выход постоянной памяти соединен со входом арифметико-логического блока, четвертый выход постоянной памяти подключен ко второму входу выходного регистра, второй вход блока микропрограммного управления каждого устройства обработки данных соединен с соответствующим выходом блока памяти, вход-, выход которого подключен ко второму выходу-входу блока программного управления, а управляющий выход блока памяти подключен к управляющему входу блока коммутации. Благодаря введению постоянных запоминающих устройств удается избежать повторений записи микрокоманд в память (имеет место в известном процессоре). Во вновь вводимое постоянное запоминающее устройство записьюается вся совокупность микрокоманд, встречающихся хотя бы в из микропрограмм. При этом микрокоманда записывается только один раз и имеет свой строго фиксированный адрес в пределах постоянного запоминающего устройства. Благодаря этому появляется возможность составлять микропрограммы реализации команд процессора просто в виде перечней имен микрокоманд с указанием правил перехода к очередному имени. Таким образом, требуемая совокупность микропрограмм, реализующих команды процессора, определена на заранее заданном множестве микрокоманд. Составленные таким образом микропрограммы, имеющие более сжатый вид, чем аналогичные микропрограммы известного процессора, хранятся в постоянном

запоминающем устройстве микропрограммного устройства.

В блоке памяти хранится Множество различньос сочетаний команд (микропрограммы) , которые встречаются в данной задаче и задают режимы работ устройств обработки в каждом такте работы процессора. Например, строка массива может иметь следующий смысл: первому устройству обработки выполнить сложение, второму - умножение, третьему - деление и т. д., а , h4-му - ничего не делать. В следующем такте сочетание команд в строке будет другое и, соответственно, устройства обработки будут работать уже в других режимах. Каждое сочетание команд для устройств обработки записывается в блок памяти один раз и получает при этом свой адрес. Благодаря этому появляется возможность составлять программу решения задачи в виде перечня различных сочетаний команд аналогично управлению на уровне микрокоманд, а сами программы, составленные таким образом, хранить в оперативном запоминающем устройстве блока программного управления. При этом длина команд программы такж сократится по сравнению с известным процессором.

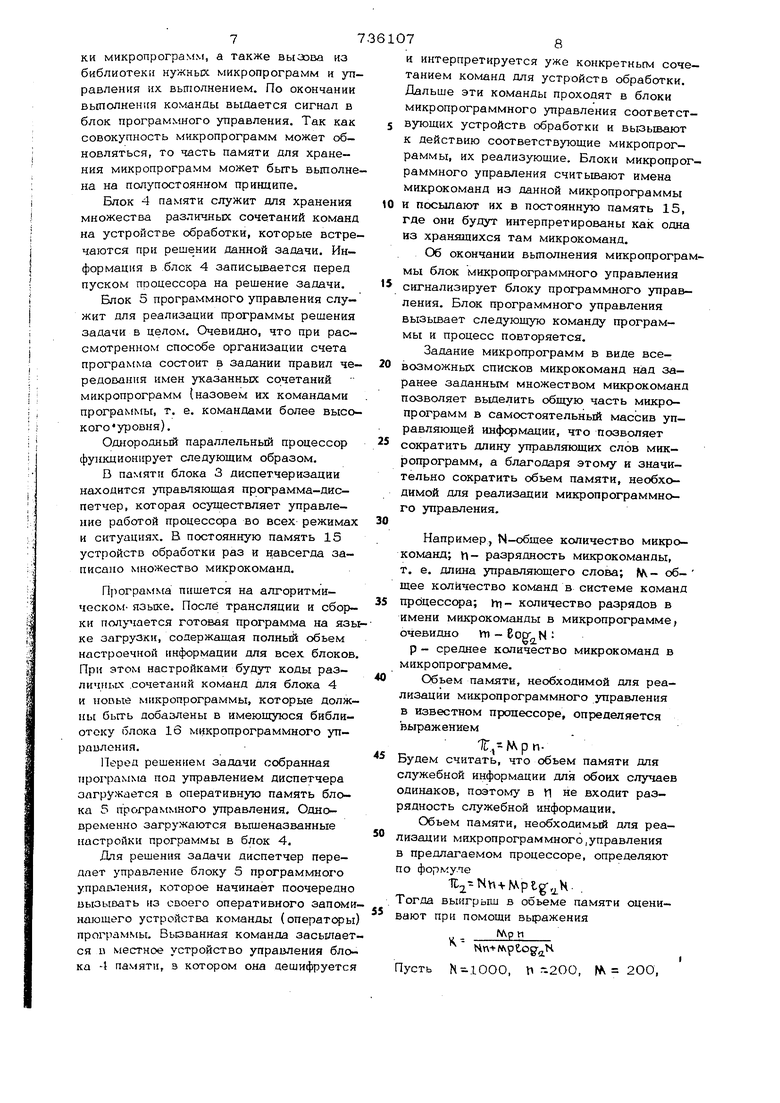

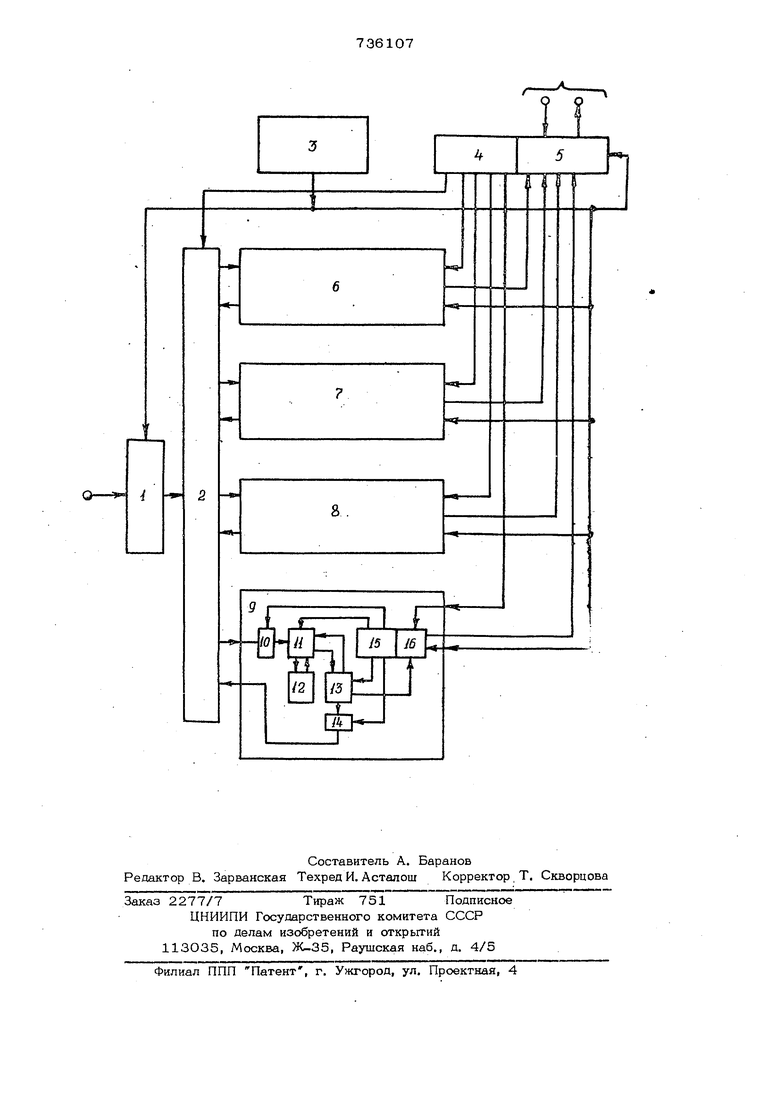

На чертеже представлена блок-схема однородного параллельного процессора, построенного на базе четырех устройств обработки данных (f 4).

Однородный параллельный процессор состоит из блока 1 приема информации, блока 2 коммутации, блока 3 диспетчеризации, блока 4 памяти (например, полупостоянной памяти), блока 5 программного управления, VI устройств 6-9 обработки данных, каждое из которых: содержит входной регистр 10, блок 11 управляемых элементов И, блок 12 оперативных регистров, арифметико-логический блок 13, выходной регистр 14, постоянную память 15 и блок 15 микропрограммного управления.

Блок 1 приема информации служит для приема данньрс извне, временного их хранения и передачи их по командам из устройства управления на выход блока коммутации.

Блок 2 коммутации служит для установления нужных связей между входами и вькодами устройств 6-9 обработки, а также выходом блока 1 приема информации и входами устройств обработки. Нужное состояние блока коммутации уста- ном

навливается при помощи информации, снимаемой с блока 4 памяти по командам из блока 5 программного управления.

Устройства 6-9 обработки служат для реализации элементарных вычислительных операций (команд). В качестве эле- ментарньк операций приняты, например, такие операции, как

алгебраическое сложение чисел с фиксированной запятой;

0

алгебраическое сложение чисел с плавающей запятой;

умножение чисел с фиксированной

запятой;

5

умножение чисел с плавающей запятой;

деление чисел с фиксированной запятой;

деление чисел с плавающей запятой;

0

умножение чисел с фиксированной запятой с произвольным форматом и т. д.

В качестве эле ментарньк операций могут быть приняты также вычисления

5 значений таких функций, как F Ах + В F - АЧ, +YH

Y А + Ч,Н

Эти функции обычно выявляются при де0композиции алгоритмов решения конкретных классов задач.

Входной регистр 10 служит для оперативного приема данных от входного устройства и от устройств обработки.

5

Выходной регистр 14 служит для оперативной выдачи результатов на входы устройств обработки, а также на другие внешние потребители информацией

Арифметико-логический блок 13 непосредственнореализует, команды, т. е. элементарные вычислительные и логические операции.

Блок 12 оперативных регистров обслуживает нуждь арифметико-логического блока.

Блок 11 управляемых элементов И служит для задания режимов pa6otbi, т. е. типов выполняемых элементарных операций устройств отработки.

Постоянная память 15 служит для хранения множества микрокоманд. Информация в память 15 заносится один раз (например, при изготовлении устройства обработки) и, как правило, в дальнейшем не меняется, хотя это и не исключается.

Блок 16 микропрограммного управления служит для хранения в своем постоянзапоминающем устройстве библиоте- ки микропрограмм, а также вызова из библиотеки нужных микропрограмм н уп равления их вьшолнением. По окончании выполнения команды выдается сигнал в блок програм шого управления. Так как совокупность микропрограмм может обновляться, то часть памяти для хранения микропрограмм может быть вьшолне на на полупостоянном принципе. Блок 4 памяти служит для хранения множества различных сочетаний команд на устройстве обработки, которые встре чаются при решении данной задачи. Информация в блок 4 записьшается перед пуском процессора на решение задачи. Блок 5 программного управления служит для реализации программы решения задачи в целом. Очевидно, что при рассмотренном способе организации счета программа состоит в задании правил че редования имен указанных сочетаний микропрограмм (назовем их командами программы, т. е. командами более высо кого «уровня). Ошгородный параллельный процессор функционирует следующим образом. D памяти блока 3 диспетчеризации находится управляющая программа-диспетчер, которая осуществляет управление работой процессора во всех режимах и ситуациях. В постоянную память 15 устройств обработки раз и навсегда записано множество микрокоманд. Программа пишется на алгоритмическом- языке. После трансляции и сборки получается готовая программа на язы ке загрузки, содержащая полный обьем настроечной информации для всех блоков При этом настройками будут коды различных сочетаний команд для блока 4 и новые микропрограммы, которые должны быть добавлены в имеющуюся библиотеку блока 16 микропрограммного управления. llispeu решением задачи собранная программа под управлением диспетчера загружается в оперативную память блока 5 программного управления. Одновременно загружаются вышеназванные настройки программы в блок 4. Для решения задачи диспетчер передает управление блоку 5 программного управления, которое начинает поочередно вызывать из своего оперативного запоми нающего устройства команды (операторы программы. Вызванная команда засылает ся в местное устройство управления блока -{ памяти, в котором она дешифруется И интерпретируется уже конкретным сочетанием команд для устройств обработки. Дальше эти команды проходят в блоки микропрограммного управления соответствующих устройств обработки и вызьшают к действию соответствующие микропрограммы, их реализующие. Блоки микропрограммного управления считьшают имена микрокоманд из данной микропрограммы и посылают их в постоянную память 15, где они будут интерпретированы как одна из хранящихся там микрокоманд. Об окончании вьтолнения микропрограммы блок микропрограммного управления сигнализирует блоку программного управления. Блок программного управления вызьшает следующую команду программы и процесс повторяется. Задание микропрограмм в виде всевозможных списков микрокоманд над заранее заданным множеством микрокоманд позволяет выделить общую часть микропрограмм в самостоятельньй массив управляющей информации, что позволяет сократить длину управляющих слов микропрограмм, а благодаря этому и значительно сократить обьем памяти, необходимой для реализации микропрограммного управления. Например, N-общее количество микрокоманд; ц- разрядность микрокоманды, т. е. длина управляющего слова; Nv- общее количество команд в системе команд процессора; ti- количество разрядов в имени микрокоманды в микропрограмме; очевидно УП - р - среднее количество микрокоманд в микропрограмме. Объем памяти, необходимой для реализации микропрограммного управления в известном процессоре, определяется выражением Т., Мрп. Будем считать, что объем памяти для лужебной информации для обоих случаев динаков, поэтому в ц не входит разядность служебной информации. Обьем памяти, необходимъШ для реаизации микропрограммного .управления предлагаемом процессоре, определяют о формуле 1l.-Nv -vNVplg-,. . огда выигрыш в объеме памяти оцениают при помощи выражения U Nn -Nvpuog-jjH N-1000, И--200, 200, усть

m 2ogr2 100O 10, p 50. Эти данные не противоречат соответствующим параметрам современньк процессоров.

Тогда, подставив эти данные, получим раз. Таким образом, для данного случая выигрыш составляет 6 раз.

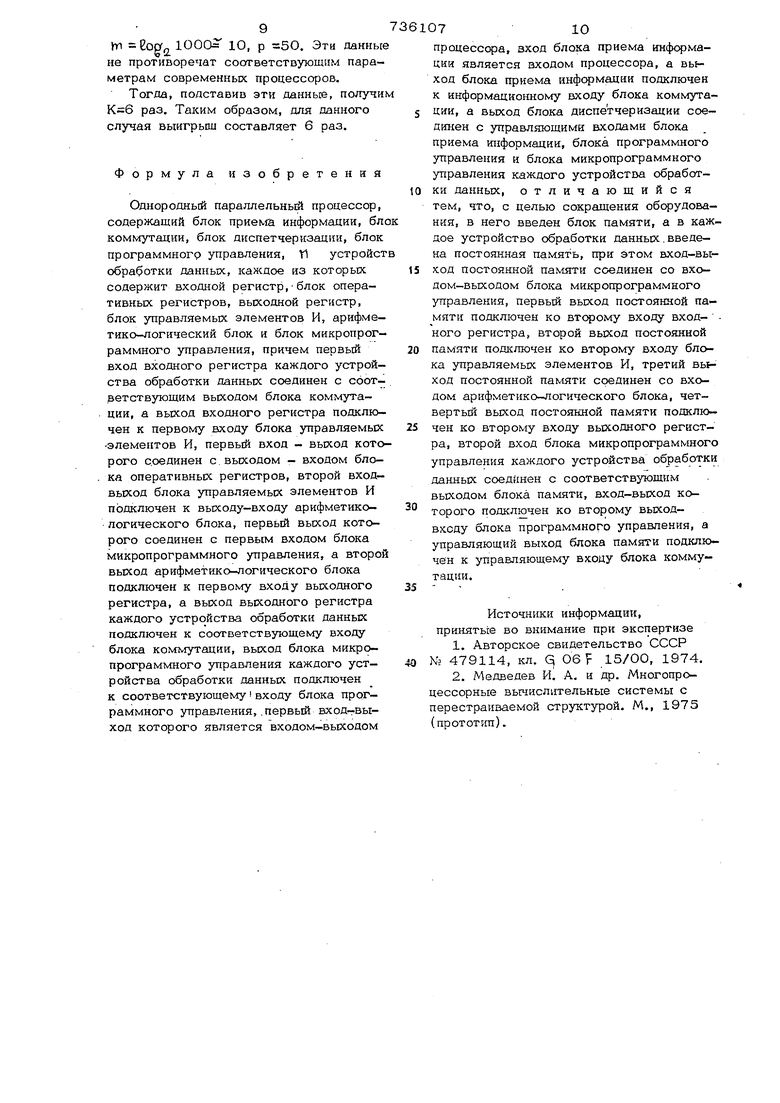

Формула изобретения

Однородный параллельньй процессор, содержащий блок приек1а информации, блок коммутации, блок диспетчеризации, блок программногр управления, Y устройств обработки данных, каждое из которых, содержит входной регистр,-блок оперативных регистров, выходной регистр, блок управляемьк элементов И, арифметико-логический блок и блок микропрограммного управления, причем первый вход входного регистра каждого устройства обработки ziaHHbK соединен с соответствующим выходом блока коммутации, а выход входного регистра подключен к первому входу блока управляемых -элементов И, первый вход - выход которого соединен с выходом - входом бло- ка оперативных регистров, второй входвыход блока управляемых элементов И подключен к выходу-входу арифметикологического блока, первый выход которого соединен с первым входом блока микропрограммного управления, а второй вькод арифметико-логического блока подключен к первому входу вькодного регистра, а выход вькодного регистра каждого устройства обработки данных подключен к соответствующему входу блока коммутации, выход блока микропрограммного управления каждого устройства обработки данных подключен к соответствующему входу блока программного управления, .первый вход-выход которого является входом-вькодом

процессора, вход блока приема информации является входом процессора, а выход блока приема информации подключен к информадкоршому входу блока коммута S ции, а выход блока диспетчеризации соединен с управл5пощимн входами блока приема информации, блока программного управления и блока микропрограммного управления каждого устройства обработ10 ки данных, отличающийся тем, что, с целью сокращения оборудования, в него введен блок памяти, а в каждое устройство обработки данных.введена постоянная память, при этом вход-вы15 ход постоянной памяти соединен со входом-выходом блока микропрограммного управления, первый выход постоянной подключен ко второму входу вход- ного регистра, второй выход постоянной 0 памяти под1слючен ко второму входу блока управляемьк элементов И, третий вь{ход постоянной памяти соединен со входом арифметико-логического блока, четвертый выход посто5шной памяти подклю- 5 чен ко второму входу выходного регистра, второй вход блока микропрограммного управления каждого устройства обработки данных соединен с соответствующим выходом блока памяти, вход-выход ко0торого подключен ко второму выходвходу блока программного управления, а управляющий выход блока памяти подключен к управляющему входу блока коммутации. 5 -.

Источники информации, принятьге во внимание при экспертизе

1.Авторское свидетельство СССР № 479114, кл. q O6F 15/00, 1974.

2.Медведев И. А. и др. Многопроцессорные вычислительные системы с перестраиваемой структурой. М., 1975 (прототип).

О

8 .

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор | 1974 |

|

SU526902A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| ПРОЦЕССОР ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ СХЕМ | 1972 |

|

SU435527A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

/

ш«и

И

/3

У6

а

Авторы

Даты

1980-05-25—Публикация

1978-02-22—Подача