рого подключен выход преобразователя параллельного кода в последовательный, а выход блока символьной синхронизации подключен к входу синхронизации триггера и через задающий счетчик к установочным входам реверсивного счетчика и накопителя.

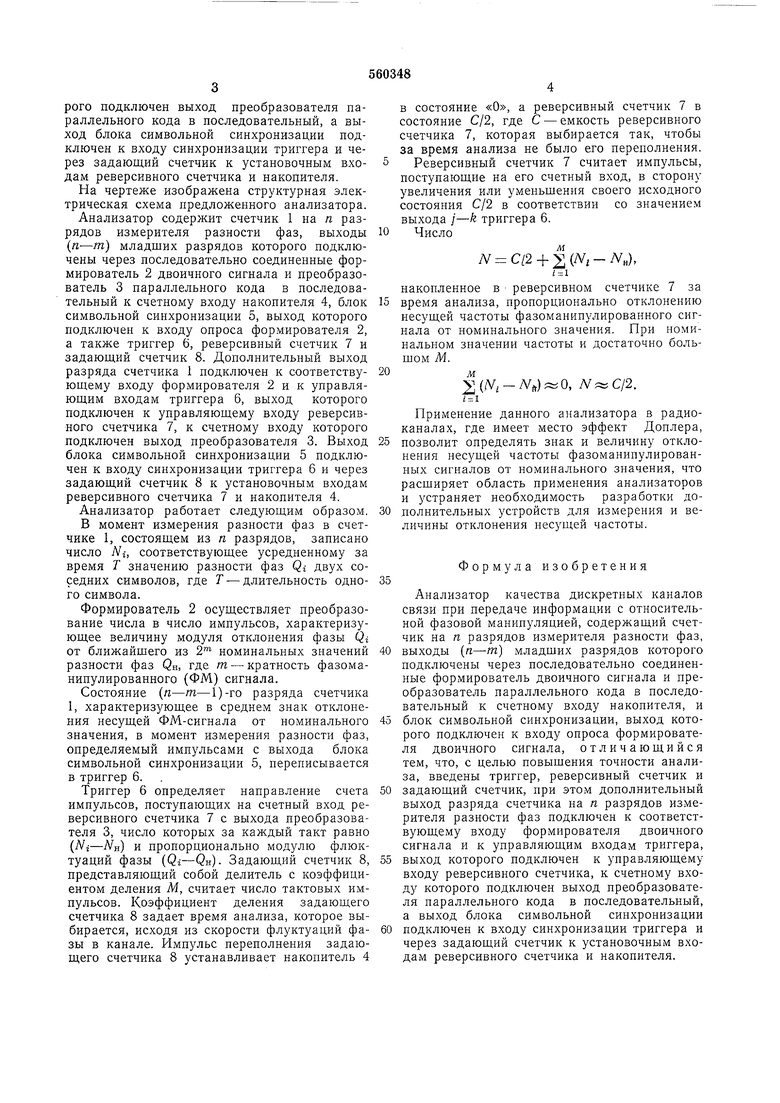

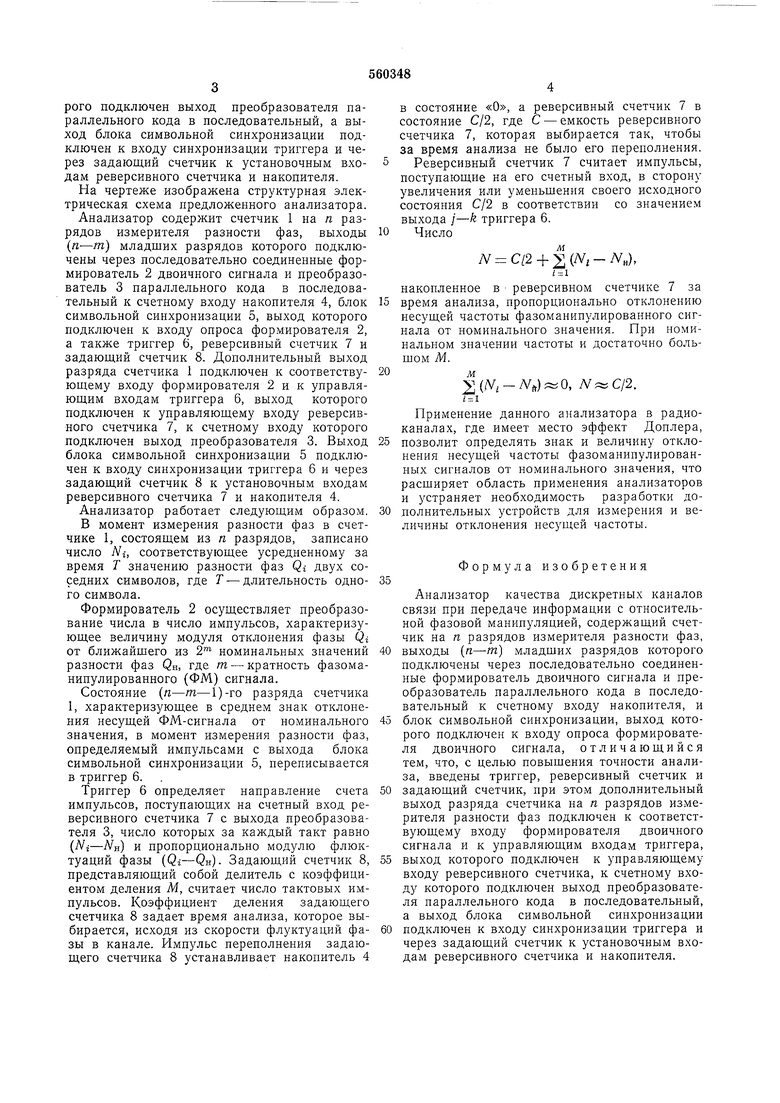

На чертеже изображена структурная электрическая схема предложенного анализатора.

Анализатор содержит счетчик 1 на п разрядов измерителя разности фаз, выходы (п--т) младших разрядов которого подключены через последовательно соединенные формирователь 2 двоичного сигнала и преобразователь 3 параллельного кода в последовательный к счетному входу накопителя 4, блок символьной синхронизации 5, выход которого подключен к входу опроса формирователя 2, а также триггер 6, реверсивный счетчик 7 и задающий счетчик 8. Дополнительный выход разряда счетчика 1 подключен к соответствующему входу формирователя 2 и к управляющим входам триггера 6, выход которого подключен к управляющему входу реверсивного счетчика 7, к счетному входу которого подключен выход преобразователя 3. Выход блока символьной синхронизации 5 подключен к входу синхронизации триггера 6 и через задающий счетчик 8 к установочным входам реверсивного счетчика 7 и накопителя 4.

Анализатор работает следующим образом.

В момент измерения разности фаз в счетчике 1, состоящем из п разрядов, записано число , соответствующее усредненному за время Т значению разности фаз Qi двух соседних символов, где Т - длительность одного символа.

Формирователь 2 осуществляет преобразование числа в число импульсов, характеризующее величину модуля отклонения фазы Q от ближайшего из 2™ номинальных значений разности фаз QH, где т - кратность фазоманипулированного (ФМ) сигнала.

Состояние (п-т-1)-го разряда счетчика 1, характеризующее в среднем знак отклонения несущей ФМ-сигнала от номинального значения, в момент измерения разности фаз, определяемый импульсами с выхода блока символьной синхронизации 5, переписывается в триггер 6.

Триггер 6 определяет направление счета импульсов, поступающих на счетный вход реверсивного счетчика 7 с выхода преобразователя 3, число которых за каждый такт равно (Ni-Л/н) и пропорционально модулю флюктуации фазы (Qi-QH). Задающий счетчик 8, представляющий собой делитель с коэффициентом деления М, считает число тактовых импульсов. Коэффициент деления задающего счетчика 8 задает время анализа, которое выбирается, исходя из скорости флуктуации фазы в канале. Импульс переполнения задающего счетчика 8 устанавливает накопитель 4

в состояние «О, а реверсивный счетчик 7 в состояние С/2, где С - емкость реверсивного счетчика 7, которая выбирается так, чтобы за время анализа не было его переполнения. Реверсивный счетчик 7 считает импульсы, поступающие на его счетный вход, в сторону увеличения или уменьшения своего исходного состояния С/2 в соответствии со значением выхода /-k триггера 6. Число

м

Л z С/2 + 2 (Ni - N,),

накопленное в реверсивном счетчике 7 за

время анализа, пропорционально отклонению несущей частоты фазоманипулированного сигнала от номинального значения. При номинальном значении частоты и достаточно большом М.

м

2(./V;-AA,), . ( 1

Применение данного анализатора в радиоканалах, где имеет место эффект Доплера,

позволит определять знак и величину отклонения несущей частоты фазоманипулированных сигналов от номинального значения, что расширяет область применения анализаторов и устраняет необходимость разработки дополнительных устройств для измерения и величины отклонения несущей частоты.

Формула изобретения

Анализатор качества дискретных каналов связи при передаче информации с относительной фазовой манипуляцией, содержаший счетчик на п разрядов измерителя разности фаз,

выходы (п-т младших разрядов которого подключены через последовательно соединенные формирователь двоичного сигнала и преобразователь параллельного кода в последовательный к счетному входу накопителя, и

блок символьной синхронизации, выход которого подключен к входу опроса формирователя двоичного сигнала, отличающийся тем, что, с целью повышения точности анализа, введены триггер, реверсивный счетчик и

задающий счетчик, при этом дополнительный выход разряда счетчика на п разрядов измерителя разности фаз подключен к соответствующему входу формирователя двоичного сигнала и к управляющим входам триггера,

выход которого подключен к унравляющёму входу реверсивного счетчика, к счетному входу которого подключен выход преобразователя параллельного кода в последовательный, а выход блока символьной синхронизации

подключен к входу синхронизации триггера и через задающий счетчик к установочным входам реверсивного счетчика и накопителя,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения качества канала связи | 1979 |

|

SU788400A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Цифровой демодулятор сигналов фазоразностной модуляции второго порядка | 1989 |

|

SU1716616A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Цифровой частотный демодулятор | 1977 |

|

SU698150A2 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Цифровое устройство частотной автоподстройки | 1983 |

|

SU1104659A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Синхрогенератор приемной части телевизионных систем | 1980 |

|

SU1035828A1 |

Авторы

Даты

1977-05-30—Публикация

1975-11-17—Подача