стопныи распределитель подключен к одному входу элемента ИЛИ, к другому входу которого подключен выход второго блока ключей, причем управляющие входы синхронного и стартстопного распределителей, первого и второго блока ключей и блока памяти соединены с Соответствующими выходами блока управления выдачей информации, входы которого соединены с сигнальными выходами блока управления, синхронного и стартстопорного распределителей.

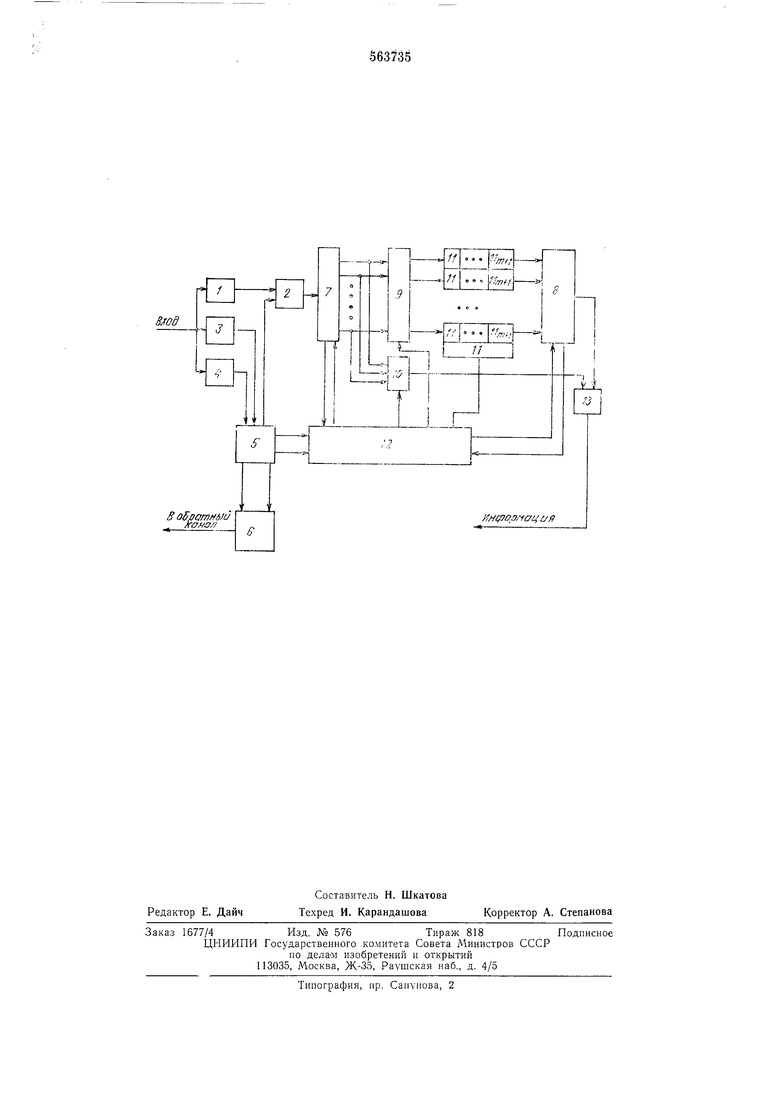

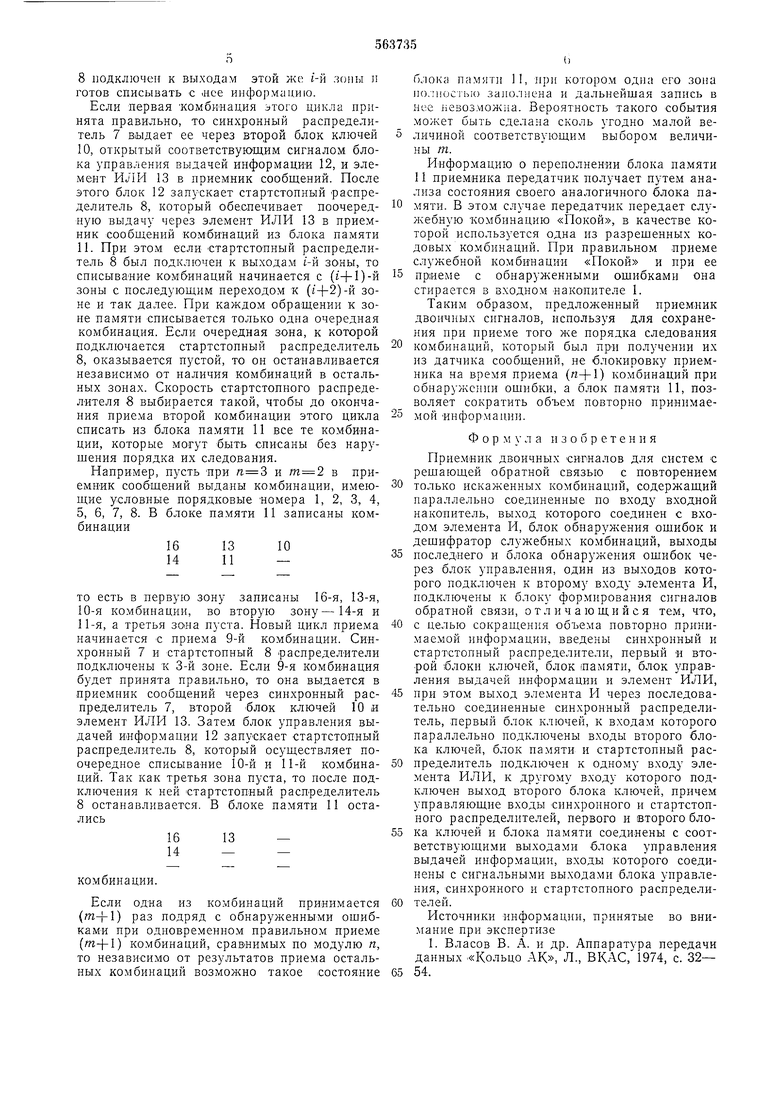

На чертеже изображена структурная электрическая схема приемника двоичных сигналов.

Приемник двоичных сигналов содержит параллельно соединенные по входу входной накопитель 1, выход которого соединен с входом элемента И 2, блок 3 обнаружения ощибок и дешифратор 4 служебных комбинаций, а блок 5 Зправления, блок 6 формирования Сигналов обратной связИ, синхронный 7 и стартстонный 8 распределители, первый 9 и второй 10 ;блок1И ключей, блок памяти II, блок 12 управления выдачей информации и элемент ИЛИ 13, при этом выход дешифратора 4 служебных комбинаций и выход блока 3 обнаружения ощибок через блок управления 5, оди-н из выходов которого подключен к второму входу элемента И 2, подключепы к блоку 6 формирования сигналов обратной связи, а выход элемента И 2 через последовательно соединенные синхронный раснределитель 7, первый блок ключей 9, к входам которого параллельно подключены входы второго блока ключей 10, блок памяти И и стартстонный распределитель 8 подключен к одному входу элемента ИЛИ .13, к другому входу которого подключен выход второго блока ключей 10, причем управляющие входы синхронного 7 и стартстопного 8 распределителей, первого 9 и второго 10 блока ключей и блока памяти 11 соединены с соответствующими выходами блока 12 управления выдачей информации, входы которого соединены с сигнальными выходами блока управления 5, синхронного 7 и стартстоиного 8 распределителей.

Ириемник двоичных сигналов работает следующим образом.

Если все предыдущие комби-нации были приняты правильно (правильным приемом будем называть любое событие, нри котором отсутствует сигнал об обнаружении ошибок от блока 3 обнаружения ощибок), то очередная правильно принятая комбинация из входного накопителя 1 поступает в приемник сообщений через открытый соответствующим сигналом |блока управления 5, элемент И 2 синхронный распределитель 7, (Второй блок ключей 10 и элемент ИЛИ 13. Синхронный 7 и стартстонный 8 распределители работают синхронно и синфазно. Блок 6 формирования сигналов обратной связи передает в обратный канал сигнал «Подтверждение.

При обнаружении ошибок в принятой комбинации она стирается. Блок 6 формирования

си -налоБ обратно, связи передает и обратный канал сигнал «Запрос. Блок управления выдачей информации 12 останавливает стартстопиый распределитель 8.

5 Комбинация, принятая правильно после комбинации с обнаруженной ошибкой, не может быть выдана в приемник сообщений, так как это привело бы к изменению порядка следования комбинаций, который был при их по0 ступлении от датчика сообщений. Поэтому эта комбинация через открытый соответствующим сигналом блока управления 5 элемент И 2, синхронный распределитель 7, первый блок ключей 9, открытый соответствую5 щим сигналом блока 12 управления выдачей информации, записывается в блок намяти И, Блок памяти II состоит из п зон, где величина п определяется временем распространения сигнала ло петле передатчик-приемник-

0 передатчик (емкость повторителя передатчика). Каждая зона состоит из (m-f-1) ячеек памяти, каждая из которьк рассчитана на запись одной комбинации.

Каждой комбинации, поступающей на вход

5 приемника двоичных сигналов, можно присвоить число натурального ряда, то есть занумеровать. Тогда процесс записи комбинаций в зоны блока намяти 11 можно рассматривать как процесс разбиения чисел натурального ряда на классы вычетов по модулю п. Например, для л 4 и т Ь это выглядит следующим образом:

1713951

1814106 2

1915117 3

2016128 4

Комбинации, записываемые в одн} и ту же зону блока памяти И, будем называть комбипациями, сравнимыми по модулю п. Назовем циклом приема прием я комбинаций, условные номера каждой из которых принадлежат различным классам вычетов. Цикл, состоящий из Комбинаций, которые все стираются, называется стираемым циклом. За начало цикла можно принимать прием любой комбинации.

Если же после приема комбинации с обнаруженными ошибками очередная комбинация будет также принята с обнаруженными ошибками, то она стирается.

Таким образом, если цикл приема начинается с приема комбинации с обнаруженными

ошибками, то каждая последующая правильно принятая комбинация цикла записывается в блок памяти И, а каждая комбинация с обнаруженными ошибками стирается.

С началом нового цикла положения синхронного 7 и стартстопного 8 распределителей совпадут. Это означает, что синхронный распределитель 7 подключен через первый блок ключей к входу t-й зоны блока Памяти и готов записывать в нее очередную принимаемую

комбинацию, а стартстопный распределитель

8 подключен к выходам этой же t-й лопы п готов списывать с лее информацию.

Если первая комбинация этого цикла нриията правильно, то синхронный распределитель 7 выдает ее через второй блок ключей

10,открытый соответствующим сигналом блока управления выдачей информации 12, и элемент ИЛИ 13 в приемник сообщений. После этого блок 12 запускает стартстопный распределитель 8, который обеспечивает поочередную выдачу через элемент ИЛИ 13 в приемник сообщений ком бинаций из блока памяти

11.При этом если Стартстопный распределитель 8 был подключен к выходам t-й зоны, то списывяние комбинаций начинается с (1-|-1)-й зоны с последующим переходом к (г-|--2)-й зоне и так далее. При каждом обращении к зоне памяти списывается только одна очередная комбинация. Если очередная зона, к котюро-й подключается стартстопный распределитель 8, оказывается пустой, то он останавливается независимо от наличия комбинаций в остальных зонах. Скорость стартстопного распределителя 8 выбирается такой, чтобы до окончания приема второй комбинации этого цикла списать из блока памяти И все те комбинации, которые могут быть списаны без нарушения порядка их следования.

Например, пусть при и в приемник сообщений выданы комбинации, имеющие условные порядковые номера 1, 2, 3, 4, 5, 6, 7, 8. В блоке памяти 11 записаны комбинации

161310

1411-

то есть в первую зону записаны 16-я, 13-я, 10-я комбинации, во вторую зону-14-я и 11-я, а третья зона пуста. Новый цикл приема начинается € приема 9-й комбинации. Синхронный 7 и стартстопный 8 распределители подключены к 3-й зоне. Если 9-я комбинация будет принята правильно, то она выдается в приемник сообщений через синхронный распределитель 7, второй блок ключей 10 и элемент ИЛИ 13. Затем блок управления выдачей информации 12 запускает стартстопный распределитель 8, который осуществляет поочередное списывание 10-й и 11-й комбинаций. Так как третья зона пуста, то после подключения к ней стартстопный распределитель 8 останавливается. В блоке памяти И остались

13

16 14

комбинации.

Если одна из комбинаций принимается раз подряд с обнаруженными ошибками при одновременном правильном приеме (т-}-) комбинаций, сравнимых ио модулю п, то независимо от результатов приема остальных комбинаций возможно такое состояние

блокя памят 11, при котором одна его зона iio.niocrbio залолнена и дальнейшая запись в нее невозможна. Вероятность такого события .может быть сделана сколь угодно малой величиной соответствующим выбором величины т.

Информацию о переполнении блока памяти 11 приемника передатчик получает путем анализа состояния своего аналогичного блока памяти. В этом случае передатчик передает служебную комбинацию «Покой, в качестве которой используется одна из разрешенных кодовых комбинаций. При правильном приеме служебной комбинации «Покой и при ее

приеме с обнаруженными ошибками она стирается в входном накопителе I.

Таким образом, предлол ;енный приемник двоичных сигналов, используя для сохранения при нриеме того же порядка следования

комбинаций, который был при получении их из датчика сообщений, не блокировку приемника на время приема {«+) комбинаций при обнаружении ошибки, а блок памяти 11, позволяет сократить объем повторно принимаемой информации.

Формула изобретения

Приемник двоичных сигналов для систем с решающей обратной связью с повторением

только искаженных комбинаций, содержащий параллельно соединенные по входу входной накопитель, выход которого соединен с входом элемента И, блок обнарул ения ошибок и дешифратор служебных комбинаций, выходы

последнего и блока обнаружения ошибок через блок управления, один из выходов которого подключен к второму входу элемента И, подключены к блоку формирования сигналов обратной связи, отличающийся тем, что,

с целью сокращения объема повторно принимаемой информации, введены синхронный и стартстопный распределители, первый и второй блоки ключей, блок ламяти, блок управления выдачей информации и элемент ИЛИ,

при этом выход элемента И через последовательно соединенные синхронный распределитель, первый блок ключей, к входам которого параллельно подключены входы второго блока ключей, блок на мяти и стартстопный распределитель подключен к одному входу элемента ИЛИ, к другому входу которого подключен выход второго блока ключей, причем управляющие входы синхронного и стартстопного распределителей, первого и второго блока ключей и блока памяти соединены с соответствующими выходами блока управления выдачей информации, входы которого соединены с сигнальными выходами блока управления, синхронного и стартстопного распределителей.

Источники информации, принятые во внимание при экспертизе

1. Власов В. А. и др. Аппаратура передачи данных .«Кольцо АК, Л., ВКАС, 1974, с. 32-

54.

;/1 .Г, /.v,,;j-,,

-| |.- FIiiIE i- i

-.;vi -

f f tfloafiaiiaff

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ передачи и приема дискретной информации для систем связи с решающей обратной связью | 1976 |

|

SU650243A1 |

| Устройство приема-передачи дискретной информации с решающей обратной связью | 1980 |

|

SU930716A1 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Устройство для передачи и приема кодов | 1978 |

|

SU949835A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

| Устройство для передачи и приема информации | 1982 |

|

SU1048580A1 |

| Телеграфное устройство для исключения обнаруженных ошибок | 1976 |

|

SU660286A2 |

| Устройство для приема избыточной информации | 1981 |

|

SU1001147A1 |

| МНОГОКАНАЛЬНАЯ АППАРАТУРА ПЕРЕДАЧИ ДВОИЧНЫХСИГНАЛОВ | 1971 |

|

SU313302A1 |

Авторы

Даты

1977-06-30—Публикация

1976-02-10—Подача