(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Микропрограммное устройство управления | 1976 |

|

SU602947A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1972 |

|

SU331387A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU824312A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1985 |

|

SU1288706A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

1

Изобретение относится к области вычислительной техники, в частности к устройствам управления и может быть испол зовано при построении ЦВМ с микропрог раммным управлением.

Известно микропрограммное устройство управления 1 содержащее ЗУ регистры, дешифраторы, генераторы тактовых сигналов-. Недостатками устройства являются ограниченное быстродействие и малая

гибкость структуры,

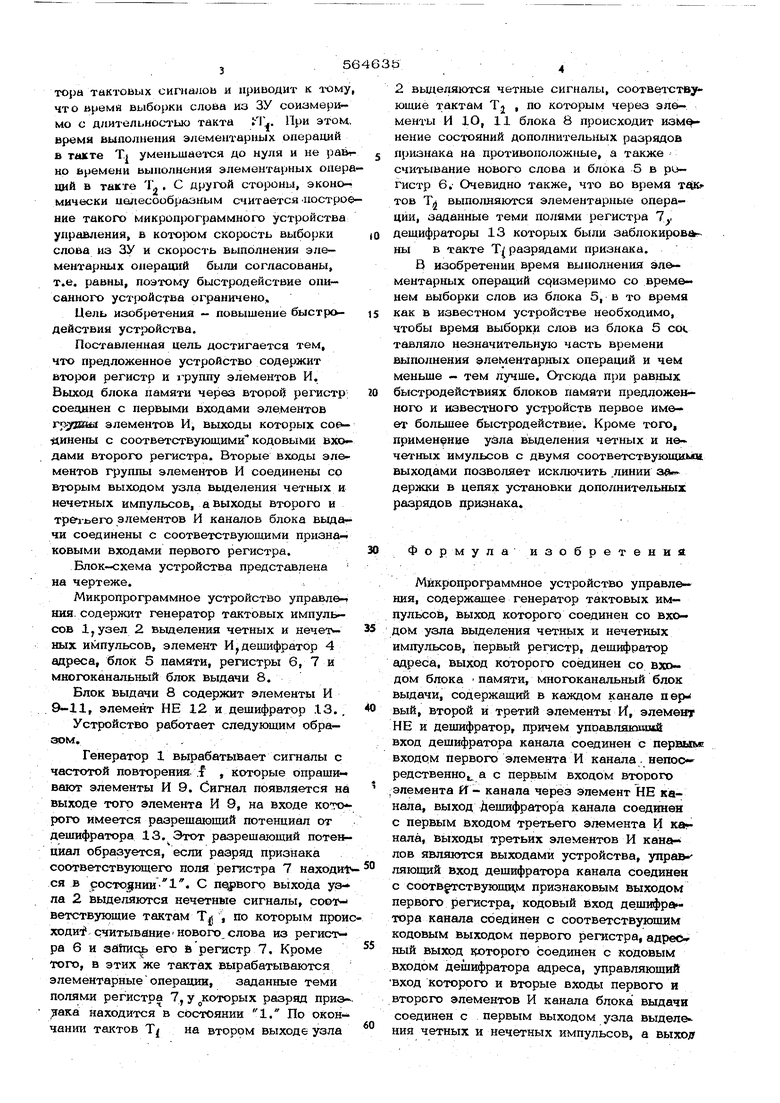

. Наиболее близким к изобретению по технической сущности и достигаемому эффекту является микропрограммное устройство управления 2j , содержащее генератор тактовых импульсов, выход которого соединен со входом узла вьщеления четных и нечетных импульсов, первый регистр, дешифратор адреса, выход которого соединен со входом блока памяти, многоканальный блок вьщачи, содержащий в каждом канале первый, второй и третий элементы И, элемент НЕ и дешифратор. Управляющий вход дешифратора канала соединен с первым входом первого элемента И канала не-

посредственно, а с первым входом второго элемента И канала через элемент НЕ канала. Выход дешифратора канала соединен с первым входом третьего элемента И канала. Выходы третьих элементов И каналов являются выходами устройства. Управляющий вход дешифратора канала соединен с соответствующим признаковым выхо дом первого регистра, кодовый вход - с соответствующим кодовым выходом первого регистра, адресный выход которого соединен с кодовым входом дешифратора адреса, управляющий вход которого и вторые входы первого к второго элементов И канала блока выдачи соединены с первым выходом узла выделения четных и нечетных импульсов, а выход генератора тактовых импульсов соединен со вторыми входами третьих элементов И каналов блока выдачи В данном устройстве управления длительность тактов Т , Tj выбрана такой, что время выборки слова из ЗУ составляет незначительную ее часть. Увеличение быстродействия этого устройства соответствует увеличению частоты повторения f генера- тора тактовых сигналов и приводит к ачэму что иремй выборки слова из ЗУ соизмеримо с длительностью такта tT. При этом время выполнения элементарных операций в такте T.i уменьшается до нуля и не рав но времени выполнения элементарных опер ций в такте Т ДРУГой стороны, экономически иалесообрааным считается постро ние такого микропрограммного устройства управления, в кото}юм скорость выборки слова из ЗУ и скорость выполнения элементарных онеращ1й были согласованы, т.е. равны, поэтому быстродействие описанного уст1юйстгва ограничено. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что предложенное устройство содержит второй регистр и группу элементов И. Выход блока памяти через BTOPOI регистр; соединен с первыми входами элементов гр яззямг элементов И, выходы которых со цинеаы с соответствующими кодовыми вхо яами второгх регистра. Вторые входы элементов группы элементов И соединены со вторым выходом узла вьщеления четньгх и нечетных импульсов, а выходы второго и тре -ьего элементов И каналов блока вьщачи соединены с соответствующими призна-ч ковыми входами первого регистра. Блок-схема устройства представлена на чертеже. Микропрограммное устройство управле-i ния. содержит генератор тактовых импульсов 1,узел 2 Бьщеления четных и нечетных импульсов, элемент И,дещифратор 4 адреса, блок 5 памяти, регистры б, 7 и многоканальный блок выдачи 8. Блок выдачи 8 содержит элементы И 9-11, элемент НЕ 12 и дешифратор 13., Устройство работает следующим образом. Генератор 1 вырабатывает сигналы с частотой повторения, .f .которые опрашивают элементы И 9. Сигнал появляется на выходе того элемента И 9, на входе которого имеется разрешающий потенциал от дешифратора 13. Этот разрешающий потен циал образуется, если раарад признака соответствующего поля регистра 7 находи ся в состо§нии-1. С левого выхода узла 2 вьщеляются нечетные сигналы, соответствующие тактам TJ; , по которым прои ходит считывание-нового слова из регистра 6 и аййись его и регистр 7, Кроме того, в этих же тактах вырабатываются элементарные операции, заданные теми полями регистра 7, у которых разряд приэ ака находится в состоянии 1. По окончании тактов Т на втором выходе узла 2 вьщеляются четные сигналы, соотвеа-ству ющие тактам Tj , по которым через элементы И Ю, 11 блока 8 происходит изм нение состояний дополнительных разрядов признака на противоположные, а также считывание нового слова и блока 5 в ригистр 6. Очевидно также, что во время Тл выполняются элементарные операции, заданные теми полями регистра 7. дешифраторы 13 которых были заблокирова ны в такте Т разрядами признака. и изобретении время выполнения элементарных операций сризмеримо со временем выборки слов из блока 5, в то время как в известном устройстве необходимо, чтобы время выборки слов из блока 5 сое тавляло незначительную часть времени выполнения элементарных операций и чем меньше - тем лучше. Отсюда при равных быстродействиях блоков памяти предложенного и известного устройств первое имеет большее быстродействие. Кроме того, применение узла в ыделения четных и нечетных имульсов с двумя соответствующими выходами позволяет исключить .линии держки в цепях установки дополнительных разрядов признака Формулаизобретений Микропрограммное устройство управления, содержащее генератор тактовых импульсов, выход которого соединен со входом узла выделения четных и нечетных импульсов, первый регистр, дешифратор адреса, выход которого соединен со входом блока памяти, многоканальный блок выдачи, содержащий в каждом канале пер вый, второй и третий элементы И, элемену НЕ и дешифратор, причем упоавя5ающиа вход дешифратора канала соединен с первьвж входом первого элемента И канала. непоО редственно а с первым входом второго .элемента Й- канапа через Элемент НЕ канала, выход Дешифратора канала соединен с первым входом третьего элемента И канала. Выходы третьих элементов И каналов явл5аются выходами устройства, управ ляющий вход дешифратора канала соединен с соотв ствующнм признаковым выходом первого регистра, кодовый Вход дешифра« тора канала соединен с соответствующим кодовым выходом первого регистра, адрес ный выход доторого соединен с кодовым входом дешифратора адреса, управляющий вход которого и вторые входы первого и второго элементов И канала блока выдачи соединен с первым выходом узла выделе ния четных и нечетных импульсов, а выходг

генераго} тактовых импульсов соединен со вторыми входами третьих элементов И каналов блока выдачи, отличающее е с я тем, что, с целью повышения быстчродеиствия, оно содержит второй регистр и группу элементов И,причем выход блока памяти че)еа второй 1)егистр соединен с первыми входами элементов группы элемен1ЮВ И, выходы которых соединены с соответствующими кодовыми входами второго регистра; вторые входы элементов группы :элементов И соединены со вахэрым выхопом

/.

узла вьщеления четных и нечетных импуль сов, а выходы второго и третьего элей ментов И каналов блока выдачи соединеныс соответствующими признаковыми входагми первого регистра.

Источники информации, принятые во внимание при экспертизе:

2,Авторское свидетельство СССР № 331387, кл. QO6.f9/16. J Я7О.

Авторы

Даты

1977-07-05—Публикация

1976-03-03—Подача