(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

и обратный выходы управляющего разряда каждого поля информационного регистра соединены с первыми входами соответствующих управляющих элементов И, вторые входы управляющих элементов И соединены с разноименными выходами блока выделения четных и нечетных сигналов, выходы управляющих элементов И через элемент ИЛИ соединены с управляющим входом соответствующего дешифратора кода операции.Это позволяет, кроме упрощения схемы за счет отказа от использования элементов задержки и элементов И на выходах дешифратора кода операции каждого поля, повысить ее надежность, поскольку в предлагаемом устроЯстве переключение управляюшн разрядов регистра информации мшкет происхси91ить тблыю в такте считывания микрокоманды из запоминающего блока.

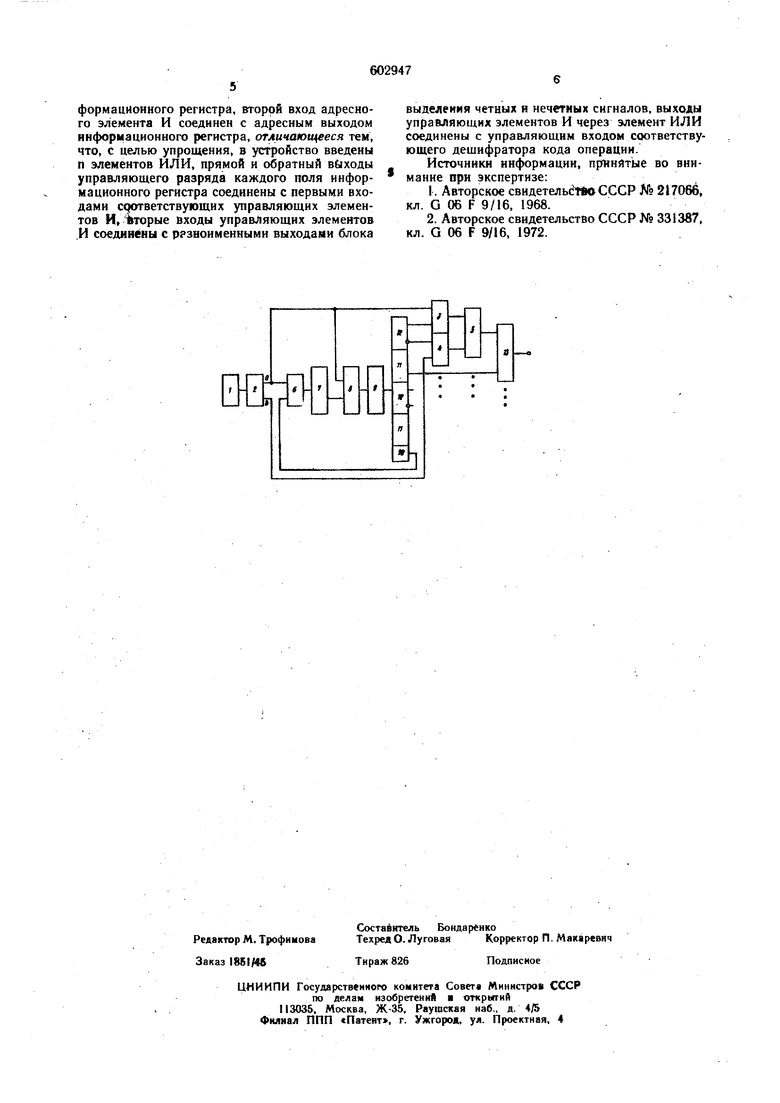

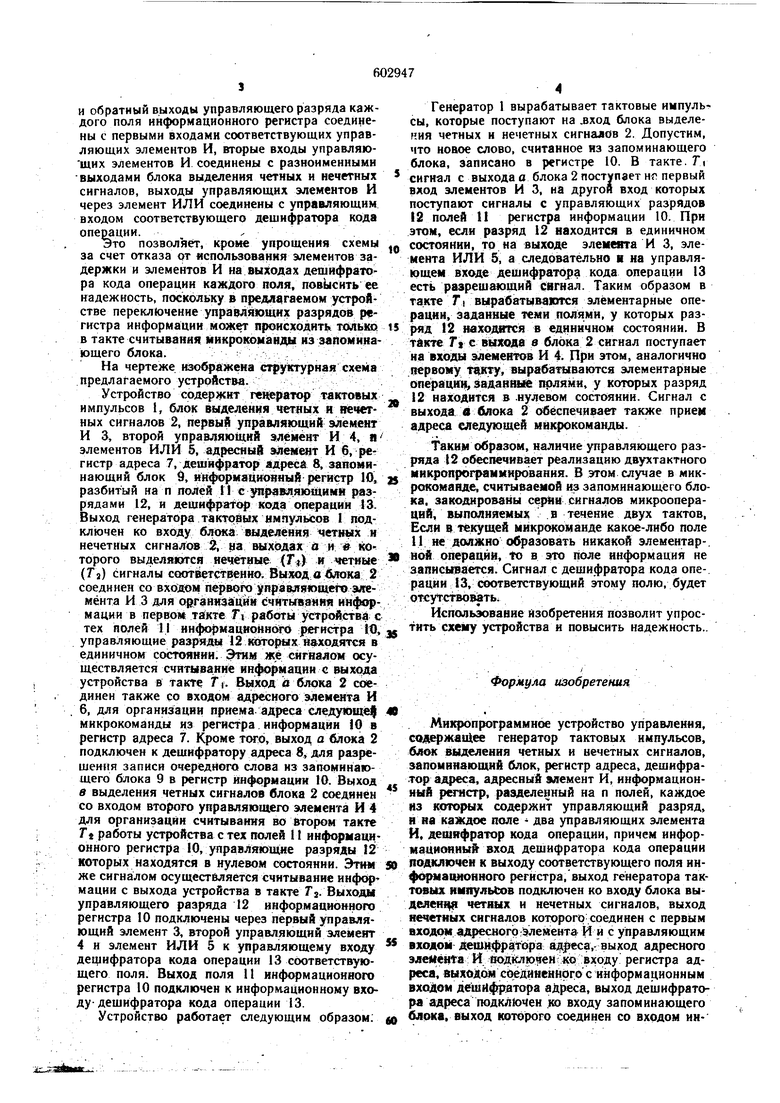

На чертеже изображена структурная схема предлагаемого устройства.

Устройство содержит генератор тактовых импульсов 1, блок выделения четных я нечетных сигналов 2, первый управляющий элемент И 3, второй управляющий элемент И 4, я элементов ИЛИ 5, адресный элемент И б, регистр адреса 7, дешифратор адреса 8, заломннающий блок 9, инфюрмационный регистр 10, разбитый на п полтей И с управляющими разрядами 12, и дешифраТ ф кода операций 13. Выход генератора тактовых нмпульЁов 1 подклк)чен ко входу блока выделения четналх н нечетных си гналов 2, на выходах и и которого выделяются нечётные (Г) и четные (Tj) сигналы с«ют)8етстс№нно. Вы)юд о блока 2 соединен со входш nepBqtro упр ацляюшего элемента И 3 для одганиздЦЙн счнты амня нмформадии в первом такте TV работы устройства с тех яслей II информационного jpefHcrpa №. управляющие разряды 12 оторых находятся в единичном состоянин. Этим жje (сигналом осуществляется считыванне инфор114ации с устройства в такте ft. Выход Ь блока 2 саединен также со входом адресного элемента И 6, для органнзацин приема, адреса следующЦ микрокоманды из регистра. информации 10 в регистр адреса 7. Кроме того, выход а блсжа 2 подключен к дещнфратору адреса 8, для разрешения записи очередного слова из запоминающего блока 9 в регистр информации 10. Выход в выделения четных сигналов блока 2 соединен со входом второго управляющего элемента И 4 для организации счнтывания во втором такте Г работы устройства с тех полей 11 информационного регистра 10, управляющие разряды 12 которых находятся в нулевом состоянни. Этнм же сигналом осуществляется считыванне информации с выхода устройства в тактеТз- Выходы управляющего разряда 12 информационного регистра 10 подключены через первый управляющий элемент 3, второй управляющий элемент 4 н элемент ИЛИ 5 к управляющему входу дещнфратора кода операции 13 соответствующего поля. Выход поля 11 информационного регистра 10 подключен к ннфорнаЦионному входу-дещнфратора кода операции 13.

Устройство работает следующим образом,

Генератор 1 вырабатывает тактовые импульсы, которые поступают на .вход блока выделер;ия четных и нечетных сигналов 2. Допустим, что новое слово, считанное нз запоминающего блока, записано в регистре 10. В такте. Т сигнал с выхода а блока 2 поступает нг первый вход элементов И 3, на другой вход которых поступают сигналы с управляющих разрядов 12 полей II регистра информации 10. При этом, еслн разряд 12 находится в единичном состояннн, то.на выходе элемента И 3, элемента ИЛИ 5, а следовательно ш на управляющем входе дешифратора кода операции 13 есть разрешающий сигнал. Таким образом в такте Г) вырабатываются элементарные one рацни, заданные теми полями, у которых разряд 12 находятся в еднннчном состоянии. В тйкте TI с выхода в блока 2 сигнал поступает на входы элементов И 4. этом, аналогично первому тадггу, вырабатываются элементарные операции, заданные прлями, у которых разряд 12 находится в .нулевом состоянии. Сигнал с выхода в блока 2 обеспечивает также прием адреса следующей мнкрокоманды.

Таким образом, наличие управляющего разряда 12 обеспечивает реализацию двухтактного микропрограммирования. В этом случае в микрокоманде, считываемой т запоминающего блока, закодированы серйн сигналов микрооперацнй, выполняемых в течение двух тактов, Еслн в текущей микрокоманде какое-либо поле 11 не должно образовать никакой элементар-. ной операции, to в это поле ннформация не запнсырается. Сигнал с дешифратора кода операцйн 13, оютветствующнй этому полю, будет от :утствомть.

Использованне изобретения позволит упростить схеМу устройства н повысить надежность..

Формула изобретения

Микропрограммное устройство управления, содержяц ее генератор тактовых импульсов, блок выделения четных и нечетных сигналов, запомннающнй блок, регистр адреса, дешифратор а.еса, адресный элемент И, информационный регнсгр, раэделеиный на п полей, каждое КЗ которых содержнт управляющий разряд, н на каждое поле - два управляющих элемента И, дешифратор кода операции, причем информаиноннь(й вход дешифратора кода операцни подключен к выходу соответствующего поля информационного регистра, выход генератора такптык иыпульЬоя подключен ко входу блока выделен1Ц1 четных н нечетных сигналов, выход нечетных снгналов которого соедннен с первым входом адресногр:элемента И и с управляющим входом дешифратора адреса,- выход адресного элe«eнta И вод йювеН;кр входу регистра адреса, выходом соединенного с информационным входом дешифратора адреса, выход дей1ифратора адреса подключен ко входу запоминающего блока, выход которого соедннен со входом ин

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

.i -Г-ДвЬмЙЕ формационного регистра, второй вход адресного элемента И соединен с адресным выходом информационного регистра, отличающееся тем, что, с целью упрощения, в устройство введены п элементов ИЛИ, прямой и обратный вйходы управляющего разряда каждого поля информационного регистра соединены с первыми входами С9ответствующих управляющих элементов И, вторые входы управляющнх элементов .И соединены с разноименными выходами блока

выделения четных и нечетиых сигналов, выходы управляющих элементов И через элемент ИЛИ соединены с управляющим входом соответствующего дешифратора кода операции.

Источники информации, пр нйтЫе во внимание при экспертизе:

ш

Авторы

Даты

1978-04-15—Публикация

1976-05-28—Подача