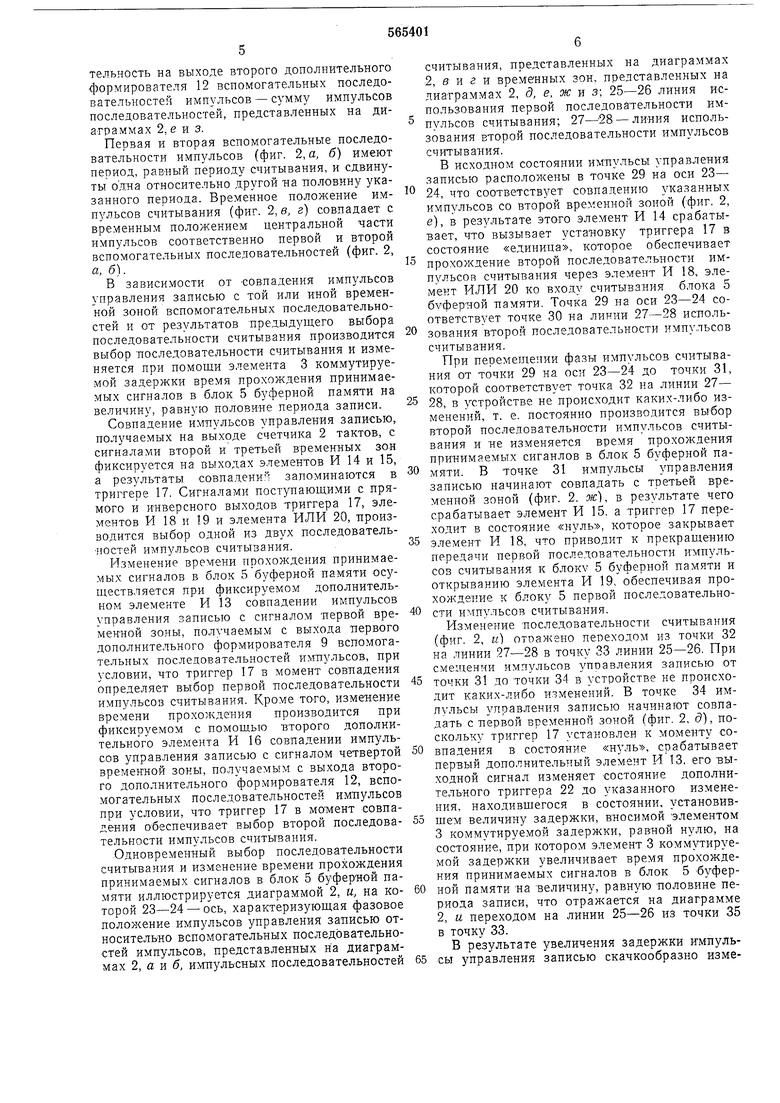

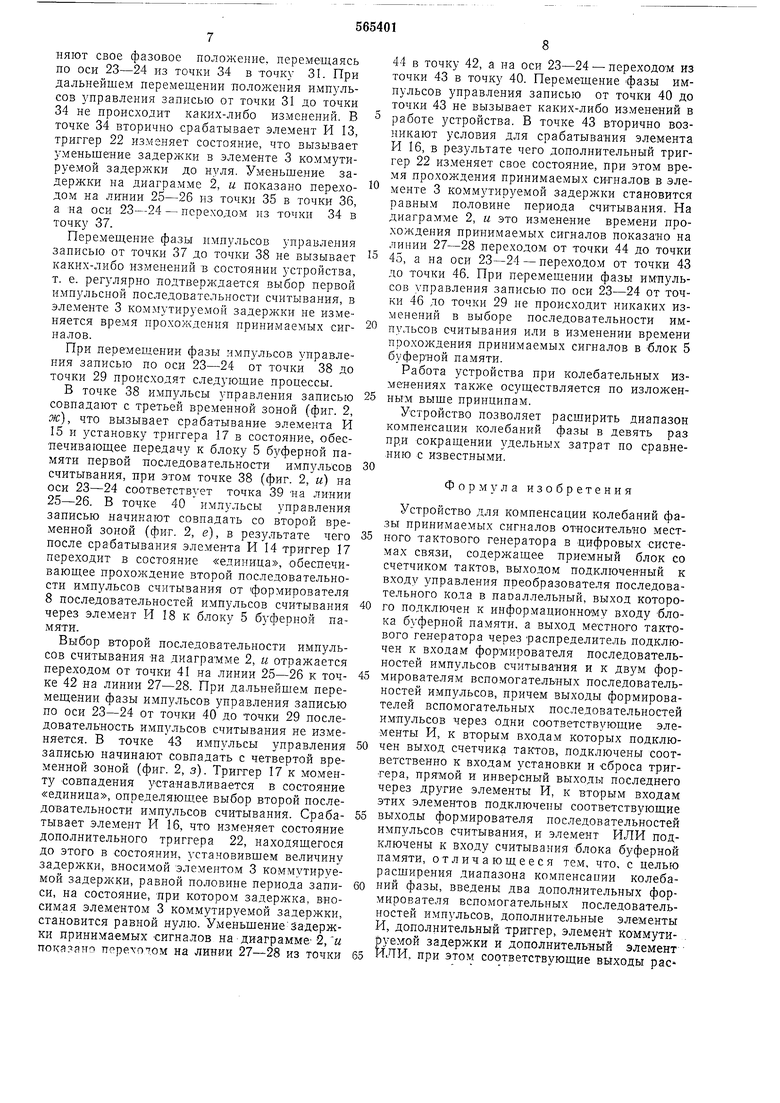

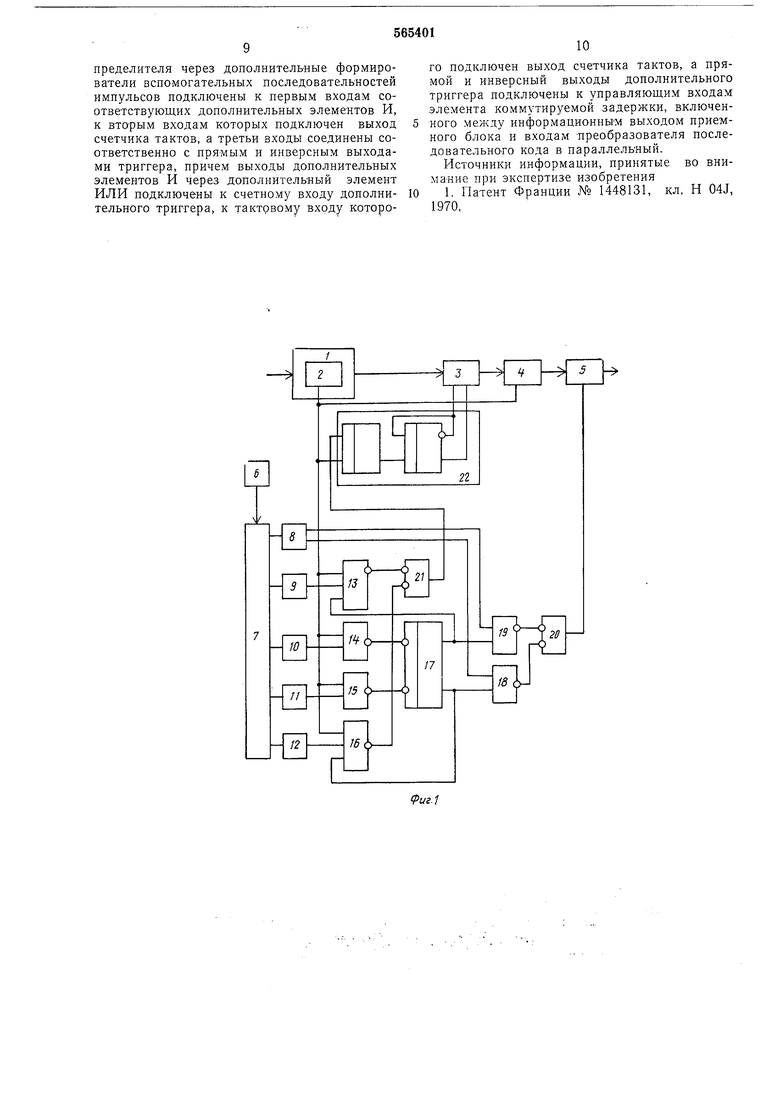

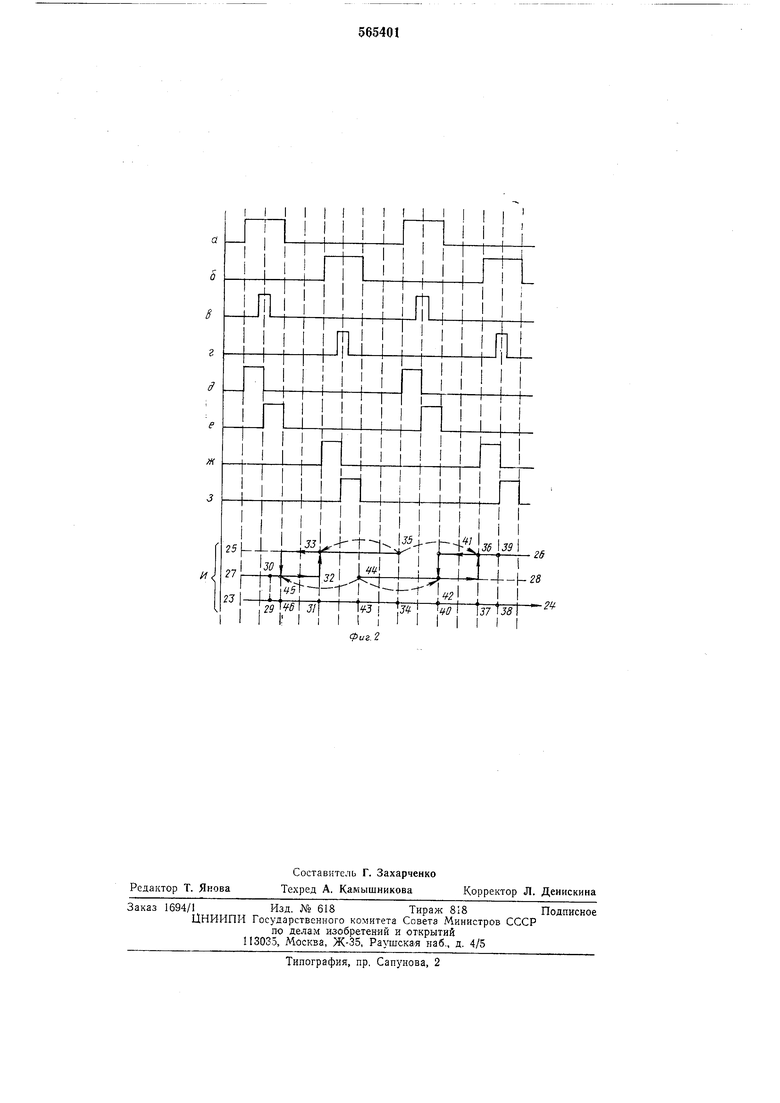

компенсируемый без искажений иринимаемых сигналов. С целью расширения диапазона компенсации колебаний фазы в предлагаемое устройство для компенсации колебаний фазы принимаемых сигналов относительно местного тактового генератора в цифровых системах связи введены два донолнительиых формирователя вспомогательных последовательностей импульсов, дополнительные элементы И, дополнительный триггер, элемент коммутируемой задержки и дополнительный элемент ИЛИ, при этом соответствующие выходы распределителя через дополнительные формирователи вспомогательных последовательностей импульсов подключены к первым входам соответствующих дололнительных элементов И, ко вторым входам которых подключен выход счетчика тактов, а третьи входы соединены соответственно с прямым и инверсным выходами триггера, причем выходы дополнительных элементов И через дополнительный элемент ИЛИ подключены к счетному входу дополнительного триггера, к тактовому входу которого подключен выход счетчика тактов, а прямой и инверсный выходы дополнительного триггера подключены к управляющим входам элемента коммутируемой задержки, включенного между информационным выходом приемного блока и входом преобразователя последовательного кода в цараллельяый. На фиг. 1 представлена структурная электрическая схема предлагаемого устройства для компенсации колебаний фазы .принимаемых сигналов относительно местного тактового генератора в .цифровых системах связи; на фиг. 2 - временные диаграммы, поясняющие его работу. Устройство содержит приемный блок 1, состоящий из счетчика 2 тактов, информационный выход приемного блока 1 через элемент 3 коммутируемой задержки и преобразователь 4 последовательного кода в параллельный соединен с информационным входом блока 5 буферной памяти, местный тактовый генератор 6 через распределитель 7 соединен с формирователем 8 последовательностей импульсов считывания, первым дополнительным формирователем 9 вспомогательных последовательностей импульсов, первым формирователем 10 вспомогательных последовательностей импульсов, с вторым формирователем 11 вспомогательных последовательностей импульсов, и вторым дополнительным формирователем 12 вспомогательных последовательностей импульсов. Выход счетчика 2 тактов соединен с входом управления преобразователя 4 последовательного кода в параллельный, выход первого дополнительного формирователя 9 вспомогательных последовательностей имлульсов соединен с первым входом первого дополнительного элемента И 13, выходы формирователей 10 и 11 подключены соответственно к первым входам элементов И 14 и 15, а выход второго дополнительного формирователя 12 вспомогательных последовательностей импульсов соединен с первым входом второго дополнительного элемента PI 16. Вторые входы элементов И 13-16 соединены с выходом счетчика 2 тактов, а выходы элементов И 14 и 15 - соответственно к входам установки и сброса триггера 17, прямой и инверсный выходы которого соединены соответственно с первыми входами элементов И 18 и 19 и с третьими входами второго и первого дополнительных элементов И 16 и 13. Вторые входы элементов И 18 и 19 подключены к выходам формирователя 8 последовательностей импульсов считывания, а выходы элементов И 18 и 19 соединены с входами элемента ИЛИ 20, выход последнего подключен к входу считывания блока 5 буферной памяти. Выходы лервого и второго дополнительных элементов И 13 и 16 соединены с входами дополнительного элемента ИЛИ 21, подключенного выходом к счетному входу дополнительного триггера 22, прямой и инверсный выходы которого соединены с управляющими входами элемента 3 коммутируемой задержки. Тактовый вход дополнительного триггера 22 соединен с выходом счетчика 2 тактов. Входом устройства для компенсации колебаний фазы принимаемых сигналов относительно местного тактового генератора в цифровых системах связи является вход приемного блока 1, а выходом - информационный выход блока 5 буферной памяти. Устройство работает следующим образом. Сигналы, поступающие па вход устройства из линии связи и проходящие через приемный блок 1, элемент 3 коммутируемой задержки и преобразователь 4 последовательного кода в параллельный, записываются в блок 5 буферной памяти с ломощью импульсов управления записью, которые формируются из принимаемых сигналов в счетчике 2 тактов. При помощи местного тактового генератора 6, распределителя 7 и формирователя 8 формируются последовательности импульсов считывания, а при помощи местного тактового генератора 6, распределителя 7 и формирователей 9-12 - вспомогательные последовательности импульсов. На диаграммах 2,а и б показаны первая и вторая вспомогательные последовательности импульсов на выходах формирователей 10 и 11 соответственно, на диаграммах 2,8 и г - первая и вторая лоследовательности импульсов считывания на выходах формирователя 8, на диаграммах 2, д, е, ж w. з -импульсы временных зон с цервой по четвертую, которые бразованы путем деления каждой вспомогаельной последовательности, показанной па иаграммах 2, а и б на две части. Вспомогательная последовательность на выоде первого дополнительного формирователя представляет собой сумму имлульсов послеовательностей, представленных на диаграм - 2, с и ж, а вспомогательная лоследовательность на выходе второго дополнительного формирователя 12 всномогательных последовательностей импульсов - сумму импульсов последовательностей, представленных на диаграммах 2, е и 3. Первая и вторая вспомогательные последовательности импульсов (фиг. 2, а, 6} имеют период, рав-ный периоду считывания, и сдвинуты одна относительно другой на половину указанного периода. Временное положение импульсов считывания (фиг. 2, в, г совпадает с временным положением центральной части импульсов соответственно первой и второй вспомогательных последовательностей (фиг. 2, а, б. В зависимости от совпадения импульсов управления записью с той или иной временной зоной вспомогательных последовательностей и от результатов предыдущего выбора последовательности считывания производится выбор последовательности считывания и изменяется при помощи элемента 3 коммутируемой задержки время прохождения принимаемых сигналов в блок 5 буферной памяти на величину, равную половине периода записи. Совпадение импульсов управления записью, получаемых на выходе счетчика 2 тактов, с сигналами второй и третьей временных зон фиксируется на выходах элементов И 14 и 15, а результаты совпадений запоминаются в триггере 17. Сигналами поступающими с прямого и инверсного выходов триггера 17, элементов И 18 н 19 и элемента ИЛИ 20, производится выбор одной из двух последовательностей импульсов считывания. Изменение времени прохождения принимаемых сигналов в блок 5 буферной памяти осуществляется при фиксируемом дополнительном элементе И 13 совпадении импульсов управления записью с сигналом первой временной зоны, получаемым с выхода первого дополнительного формирователя 9 вспомогательных последовательностей импульсов, при условии, что триггер 17 в момент совпадения определяет выбор первой последовательности импульсов считывания. Кроме того, изменение времени прохождения производится при фиксируемом с помощью второго дополнительного элемента И 16 совпадении импульсов управления записью с сигналом четвертой временной зоны, получаемым с выхода второго дополнительного формирователя 12, вспомогательных последовательностей импульсов при условии, что триггер 17 в момент совпадения обеспечивает выбор второй последовательности импульсов считывания. Одновременный выбор последовательности считывания и изменение времени прохождения принимаемых сигналов в блок 5 буферной памяти иллюстрируется диаграммой 2, и, на которой 23-24 - ось, характеризующая фазовое положение импульсов управления записью относительно вспомогательных последовательностей импульсов, представленных на диаграммах 2, а и б, импульсных последовательностей считывания, представленных на диаграммах 2, 8 и г и временных зон, представленных на диаграммах 2, д, е, ж w з; 25-26 линия использования первой последовательности импульсов считывания; 27--28 - линия использования второй последовательности импульсов считывания. В ИСХОДНОЛ1 состоянии импульсы управления записью расположены в точке 29 на оси 23- 24, что соответствует совпадению указанных импульсов со второй временной зоной (фиг. 2, е), в результате этого элемент И 14 срабатывает, что вызывает установку триггера 17 в состояние «единица, которое обеспечивает прохождение второй последовательности импульсов считывания через элемент И 18, элемент ИЛИ 20 ко входу считывания блока 5 буферной памяти. Точка 29 на оси 23-24 соответствует точке 30 на линии 27-28 использования второй последовательности импульсов считывания. При перемещении фазы импульсов считывания от точки 29 на оси 23-24 до точки 31, которой соответствует точка 32 на линии 27- 28, в устройстве не происходит каких-либо изменений, т. е. постоянно производится выбор второй последовательности импульсов считывания и не изменяется время прохождения принимаемых снганлов в блок 5 буферной памяти. В точке 31 импульсы управления записью начинают совпадать с третьей временной зоной (фиг. 2. ж, в результате чего срабатывает элемент И 15. а триггер 17 переходит в состояние «нуль, которое закрывает элемент И 18, что приводит к прекращению передачи первой последовательности импульсов считывания к блоку 5 буферной памяти и открыванию элемента И 19, обеспечивая прохождение к блоку 5 первой последовательности импульсов считывания. Изменение последовательности считывания (фиг. 2, и отоажено переходом из точки 32 на линии 27-28 в точку 33 линии 25-26. При смещении импульсов управления записью от точки 31 до точки 34 в устройстве не происходит каких-либо изменений. В точке 34 импульсы управления записью начинают совпадать с первой временной зоной (фиг. 2, д, поскольку триггер 17 установлен к моменту совпадения в состояние «нзль, срабатывает первый дополнительный элемент И 13, его выходной сигнал изменяет состояние дополнительного триггера 22 до указанного изменения, находивщегося в состоянии, установившем величину задержки, вносимой элементом 3 коммутируемой задержки, равной нулю, на состояние, при котором элемент 3 коммутируемой задержки увеличивает время прохождения принимаемых сигналов в блок 5 буферной памяти на величину, равную половине периода записи, что отражается на диаграмме 2, и переходом на линии 25-26 из точки 35 в точку 33. В результате увеличения задержки импульсы управления записью скачкообразно изменяют свое фазовое положение, перемещаясь по оси 23-24 из точки 34 в точку 31. При дальнейшем перемещении положения импульсов управления записью от точки 31 до точки 34 не происходит каких-либо изменений. В точке 34 вторично срабатывает элемент И 13, триггер 22 изменяет состояние, что вызывает уменьшение задержки в элементе 3 коммутируемой задержки до нуля. Уменьшение задержки на диаграмме 2, и показано переходом на лянии 25-26 из точки 35 в точки 36, а на оси 23-24 - переходом из точки 34 в точку 37.

Перемещение фазы импульсов управления записью от точки 37 до точки 38 не вызывает каких-либо изменений в состоянии устройства, т. е. регулярно подтверждается выбор первой имп)льсной последовательности считывания, в элементе 3 коммутируемой задержки не изменяется время прохождения принимаемых сигналов.

При перемещении фазы импульсов управления записью по оси 23-24 от точки 38 до точки 29 происходят следующие процессы.

В точке 38 имп)льсы управления записью совпадают с третьей временной зоной (фиг. 2, ж, что вызывает срабатывание элемента И 15 и установку триггера 17 в состояние, обеспечивающее передачу к блоку 5 буферной памяти первой последовательности импульсов считывания, при этом точке 38 (фиг. 2, и) на оси 23-24 соответствует точка 39 на линии 25-26. В точке 40 импульсы управления записью начинают совпадать со второй временной зоной (фиг. 2, е), в результате чего после срабатывания элемента И 14 триггер 17 переходит в состояние «единица, обеспечивающее прохождение второй последовательности импульсов считывания от формирователя 8 последовательностей импульсов считывания через элемент И 18 к блоку 5 буферной памяти.

Выбор второй последовательности импульсов считывания -на диаграмме 2, и отражается переходом от точки 41 на линии 25-26 к точке 42 на линии 27-28. При дальнейшем перемещении фазы импульсов управления записью по оси 23-24 от точки 40 до точки 29 последовательность импульсов считывания не изменяется. В точке 43 импульсы управления записью начинают совпадать с четвертой временной зоной (фиг. 2, з). Триггер 17 к моменту совпадения устаиавливаетея в состояние «единица, определяющее выбор второй последовательности импульсов считывания. Срабатывает элемент И 16, что изменяет состояние дополнительного триггера 22, находящегося до этого в состоянии, установившем величину задержки, вносимой элементом 3 коммутируемой задержки, равной половине периода записи, на состояние, при котором задержка, вносимая элементом 3 коммутируемой задержки, становится равной нулю. УменьшениеЗадержки принимаемых сигналов на диаграмме-2, м показано ттерелочом на линии 27-28 из точки

44 в точку 42, а на оси 23-24 - переходом из точки 43 в точку 40. Перемещение фазы импульсов управления записью от точки 40 до точки 43 не вызывает каких-либо изменений в

работе устройства. В точке 43 вторично воз} икают условия для срабатывания элемента И 16, в результате чего дополнительный триггер 22 изменяет свое состояние, при этом время прохождения принимаемых сигналов в элементе 3 коммутируемой задержки становится равным половине периода считывания. На диаграмме 2, и это изменение времени прохождения принимаемых сигналов показано на линии 27-28 переходом от точки 44 до точки

45, а на оси 23-24 - переходом от точки 43 до точки 46. При перемещении фазы импульсов управления записью по оси 23-24 от точки 46 до точки 29 пе происходит никаких изменений в выборе последовательности импульсов считывания или в изменении времени прохождения принимаемых сигналов в блок 5 буферной памяти.

Работа устройства при колебательных изменениях также осуществляется по изложенным выше принципам.

Устройство позволяет расширить диапазон компенсации колебаний фазы в девять раз при сокращении удельных затрат по сравнению с известными.

Формзла изобретения

Устройство для компенсации колебаний фазы принимаемых сигналов относительно местного тактового генератора в цифровых системах связи, содержащее приемный блок со счетчиком тактов, выходом подключенный к входу управления преобразователя последовательного кола в паоаллельный, выход которого подключен к информационному входу блока буферной памяти, а выход местного тактового генератора через распределитель подключен к входам формирователя последовательностей импульсов считывания и к двзш формирователям вспомогательных последовательностей импульсов, причем выходы формирователей вспомогательных последовательностей импульсов через одни соответствующие элементы И, к вторым входам которых подключен выход счетчика тактов, подключены соответственно к входам установки и сброса триггера, прямой и инверсный выходы последнего через другие элементы И, к вторым входам этих элементов подключены соответствующие

выходы формирователя последовательностей импульсов считывания, и элемент ИЛИ подключены к входу считывания блока буферной памяти, отличающееся тем, что, с целью расширения диапазона компенсации колебаНИИ фазы, введены два дополнительных формирователя вспомогательных последовательностей импульсов, дополнительные элементы И, дополнительный триггер, элемент коммутируемой задержки и дополнительный элемент

ИЛИ, при этом соответствующие выходы распределителя через дополнительвые формирователи вспомогательных последовательностей импульсов подключены к первым входам соответствующих дополнительных элементов И, к вторым входам которых подключен выход счетчика тактов, а третьи входы соединены соответственно с прямым и инверсным выходами триггера, причем выходы дополнительных элементов И через дополнительный элемент ИЛИ подключены к счетному входу дополнительного триггера, к тактрвому входу которого подключен выход счетчика тактов, а прямой и инверсный выходы дополнительного триггера подключены к управляющим входам элемента коммутируемой задержки, включенного между информационным выходом приемного блока и входам преобразователя последовательного кода в параллельный.

Источники информации, принятые во внимание при экспертизе изобретения

1. Патент Франции № 1448131, кл, Н 04J, 1970,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МЕСТ ПОВРЕЖДЕНИЯ НАПОРНОГО ТРУБОПРОВОДА | 1992 |

|

RU2046251C1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1381584A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для отображения графической информации | 1985 |

|

SU1278929A1 |

| Цифровой компенсатор выпадений телевизионного сигнала яркости | 1985 |

|

SU1269274A1 |

Авторы

Даты

1977-07-15—Публикация

1974-04-30—Подача