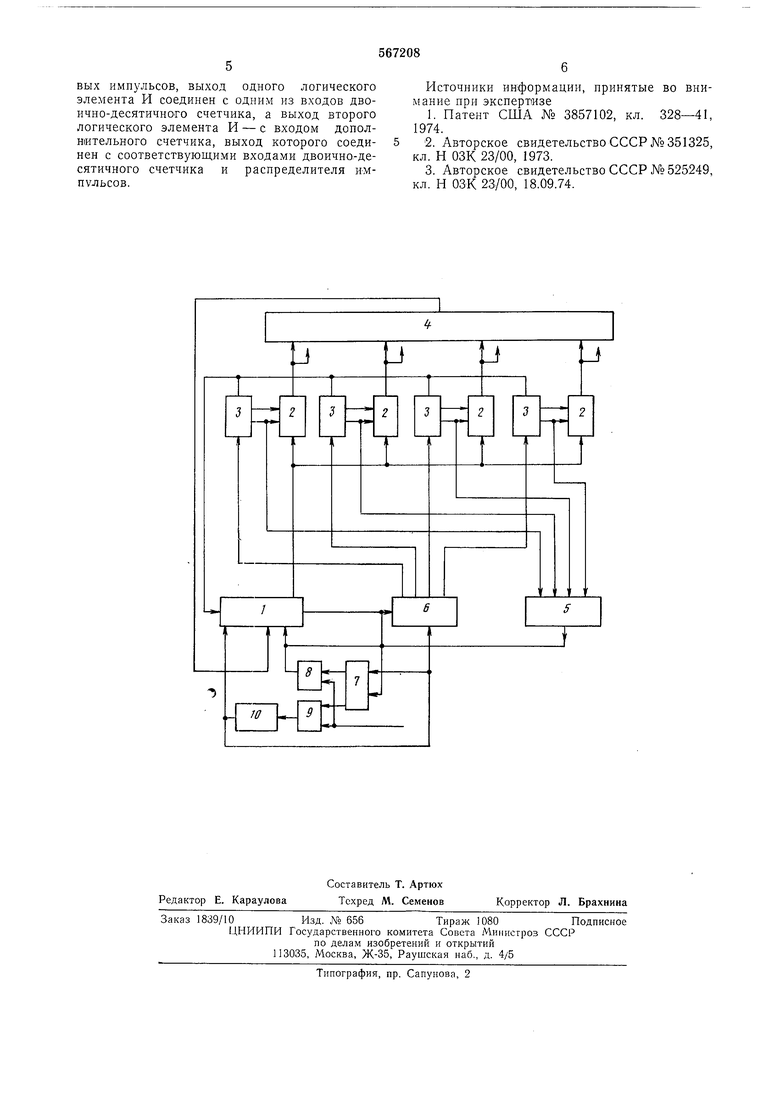

чик 1, регистры 2 хранения, элементы 3 задержки, селектор 4, элемент ИЛИ 5, распределитель 6 импульсов, триггер 7, элементы И 8, 9, буферный .счетчик 10. Выход счетчика 1 соединен с входами регистров 2, выходы которых через селектор 4 подключены к входаМ счетчика 1. Первые выходы элементов 3 задержки соединены с управляющим входом чтения регистров 2, вторые выходы элементов 3 задержки подключены к управляющим входам записи регистров 2 и входам элемента ИЛИ 5, третьи выходы соединены между собой и с входом сброса счетчика 1, а входы элементов 3 задержки Соединены с выходами распределителя 6 имлульсов. Выход переполнения счетчика 1 подключен к входу распределителя 6 и к входу установки в «1 триггера 7, выходы которого подключены к первым входам элементов И 8, 9, вторые входы последних соединены с входом счетчика. Выход элемента И 8 соединен с выходом элемента ИЛИ 5 и со счетным входом счетчика 1, выход элемента И 9 - се счетным входом буферного счетчика 10, выход последнего соединен с входом счетчика 1 и входами установки в «О триггера 7 и распределителя импульсов 6.

Счетчик работает следующим образом.

В исходном состоянии счетчики 1, 10, распределитель 6 импульсов, .регистры 2 и триггер 7 находятся в нулевом сОСтоянии, при этом имеется разрешающий потенциал «а входе элемента И 8.

При поступлении импульсов на вход счетчика появляются импульсы на выходе элемента И 8, которые поступают на счетный вход счетчика 1. Как только счетчик 1 досчитает до 10, на его выходе появляется импульс переполнения, который поступает на вход распределителя 6 импульсов и одновременно устанавливает «1 в триггере 7. На нервом выходе распределителя 6 пояВляется импульс, который поступает на вход первого элемента 3 задержки, на выходах которого появляются сигналы, сдвинутые во времени относительно друг друга. Первым импульсом с выхода элемента 3 задержки осуществляется чтение содержимого регистра 2 второго разряда, информация из регистра 2 через селектор 4 записывается в счетчик 1. . Второй импульс с выхода элемента 3 задержки через элемент ИЛИ 5 поступает на счетный вход счетчика 1, и таким образом к значению второго разряда будет добавлена «1. Одновременно второй импульс с выхода элемента 3 задержки поступает на управляющий вход записи регистра 2, разрешая запись в регистр 2 содержимого счетчика 1. Третьим импульсом с выхода элемента 3 задержки счетчик 1 устанавливается в нулевое состояние. Если лри добавлении «1 к значению второго разряда появится импульс переполнения, то появится сигнал на втором выходе раснределителя 6 импульсов, который поступит на вход второго элемента 3 задержки. К значению третьего разряда будет прибавлена «1, нри этом работа счетчика происходит, как описано выше, только в операциях участвуют второй элемент 3 задержки и регистр 2 третьего разряда. Если при добавлении «1 к значению третьего разряда появится имлульс переполнения, появится сигнал на третьем выходе распределителя 6 имлульсов и т. д. Первый же импульс переполнения счетчика

устанавливает в «1 триггер 7, при этом снимается разрешение с элемента И 8 и подается разрешение на первый вход элемента И 9. Входные импульсы проходят на выход элемента И 9 и поступают на вход буферного

счетчика 10. При появлении импульса перепоЛНения на выходе счетчика 10 распределитель 6 импульсов и триггер 7 будут установлены в «О, а в счетчик 1 запишется «1 в соответствующий разряд. Так как триггер 7 переключится в нулевое состояние, будет подано разрешение на элемент И 8 и последующие входные сигналы будут суммироваться в счетчике 1. Емкость буферного счетчика 10 выбирается, исходя из условия обеспечения требуемого быстродействия, и определяется количеством разрядов многоразрядного декадного счетчика и частотой входных сигналов. Целесообразно выбирать емкость буферного счетчика

10 дискретной 2 (2, 4, 8), в этом случае при появлении импульса переноса в буферном счетчике достаточно добавить «1 в соответствующий разряд двоично-десятичного счетчика 1.

В известном счетчике период следования входящих импульсов должен быть больше, чем время, необходимое для добавления «1 последовательно ко всем разрядам. Поскольку добавление «1 к содержимому одного

разряда занимают три такта (перенос содержимого регистра в счетчик, добавление «1 и перезапись, установление счетчика в «О), то общее время добавления «1 ко всем разрядам велико. Это существенно снижает быстродействие известного устройства. В предлагаемом счетчике во время добавления «1 к значению разрядов счет входных импульсов продолжается в буферном счетчике. Поскольку емкость буферного счетчика не может

быть больше 10, максимальное быстродействие предлагаемого счетчика в 10 раз больше, чем известного устройства.

Формула изобретения

Многоразрядный декадный счетчик по авт. св. № 525249, отличающийся тем, что, с целью повышения быстродействия, в него

введены дополнительный счетчик, два логических элемента И и триггер, причем входы триггера соединены с входами распределителя импульсов, выходы триггера - с первыми входами логических элементов И, вторые входы которых соединены с источником тактовых импульсов, выход одного логического элемента И соединен с одним из входов двоично-десятичного счетчика, а выход второго логического элемента И - с входом дополнительного счетчика, выход которого соединен с соответствующими входами двоично-десятичного счетч.ика и распределителя ИМПУЛЬСОВ.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3857102, кл. 328-41, 1974.

2.Авторское свидетельство СССР ЛЬ 351325, кл. Н ОЗК 23/00, 1973.

3.Авторское свидетельство СССР № 525249, кл. Н ОЗК 23/00, 18.09.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядный декадный счетчик | 1974 |

|

SU525249A1 |

| Пересчетное устройство | 1982 |

|

SU1046935A1 |

| Датчик времени | 1980 |

|

SU922706A2 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Устройство для считывания графической информации | 1983 |

|

SU1163343A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь двоичного кода в десятичный | 1976 |

|

SU691842A1 |

| Устройство для измерения скорости изменения частоты | 1989 |

|

SU1620952A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

Авторы

Даты

1977-07-30—Публикация

1976-03-29—Подача