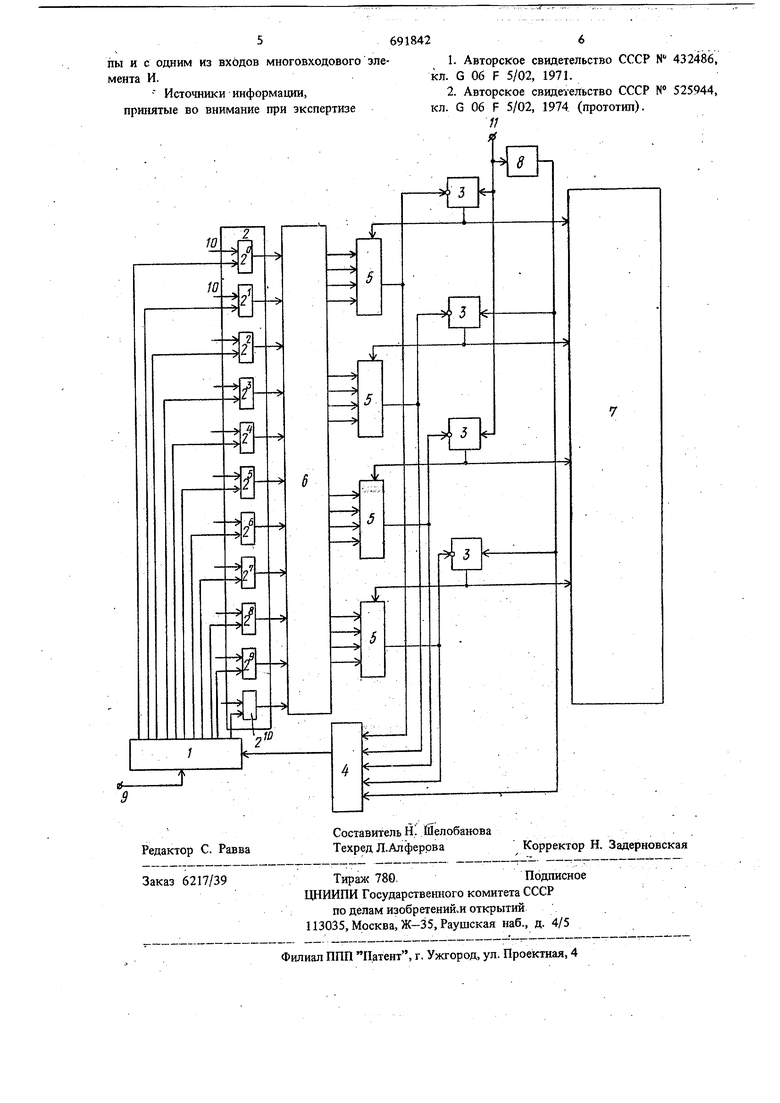

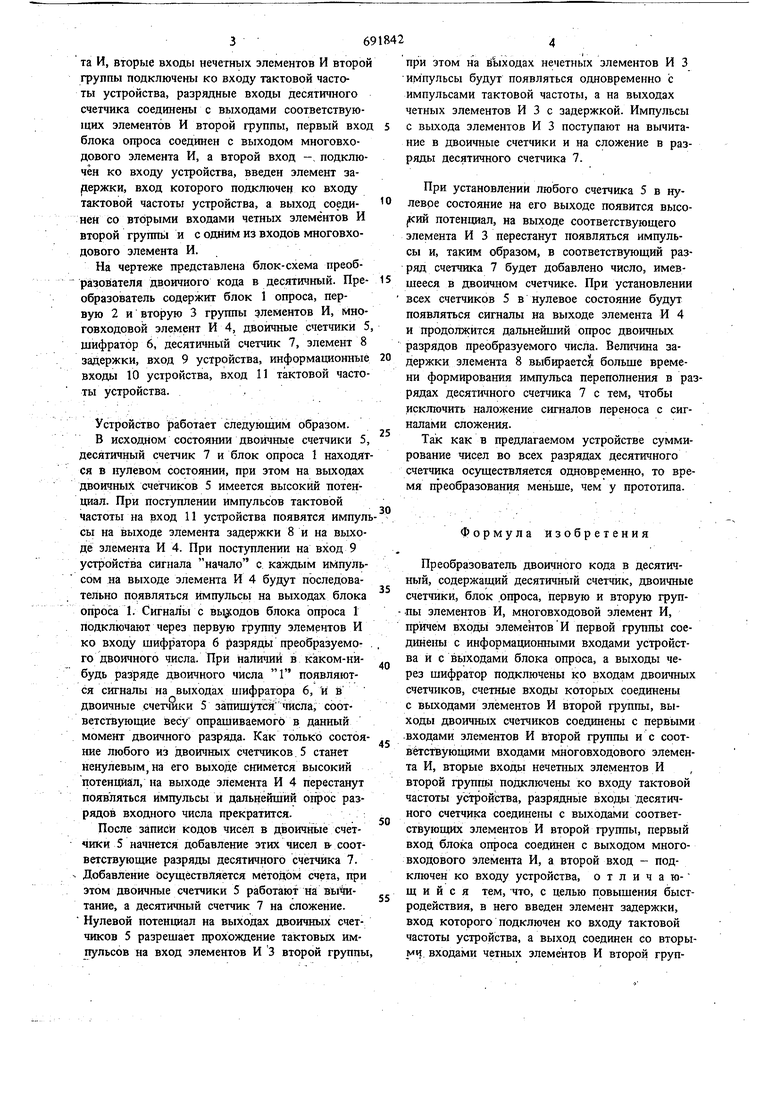

i : Изобретение относится к области вычислительной техники и мояЛт быть использованр , в устройствах цифровой автоматики. Известно устройство для преобразования двоичных чисел в десятичные, (5Ьдёр: кащеер егистр, блок опроса, сдвиговые регистры по числу декад, сятичный счетчик II. Однако данное устройство обладает невысоким быстродействием. Наиболее близким по технической сущности к предложенному является преобразователь двоичного кода в десятичный, содержащий десятичный счетчик, двоичные счетчики, блок опроса, первую и вторую группы злементов И многовхбдовой элемент И, причем входы злементов И первой группы соедине1п 1 с информационными входами устройства и с выходами блока опроса, а выходы через шифратор подключены ко входам двоичНьтх счётчиков, счетные входы которых соедгаены с выходами злементов И второй группы, выходы двонЧйьк счетчиков Соединены с первыми входами эле; ментов И второй группы и с соответствующими входами многовходового элемента И, вторые входы нечетных элементов И второй группы подключены ко -входу тактовой частоты устройства, первый, вход блока, опроса соединен с выходом Многовходово1;о элемента И, а второй вход - подключен ко входу устрой.ства 2.. Однако известное устройство также облада-. ет недостаточным быстродействием. Целью настоящего изобр.етения является повышение быстродействия преобразователя. Это достигается тем, что в преобразователь даоичного кода в десятич ый, содержащий десятичный счетчик, двоичные счетчики, блок опроса, первую и вторую группы элементов И.. мнОговходовой элемент И, причем входы элементов И первой группы соедимены с информацио1ШЬ1МИ входами устройства и с выходами блока опроса, а выходы через шифратор подключены ко входам двоичных счетчиков, счетные входы которых соединёньг с выходами элементов И второй группы, выходы двоичных счетчиков соединены с первыми входами элементов И второй группы и с соответствующ11ми входами многовходового злемен36та И, вторые входы нечетных элементов И второй группы подключены ко входу тактовой частоты устройства, разрядные входы десят№шого счетчика соединены с выходами соответствующих элементов И второй группы, первый вход блока опроса соединен с выходом многовходового элемента И, а второй вход -, подключен ко входу устройства, введен элемент зарержки, вход которого подключен ко входу тактовой частоты устройства, а выход соединен со вторыми входами четных элементов И второй группь и с одним из входов многовходового элемента И. На чертеже представлена блок-схема преобразователя двоичного кода в десятичный. Преобразователь содержит блок 1 опроса, первую 2 и вторую 3 группы элементов И, многовходовой элемент И 4, двоичные счетчики 5 шифратор 6, десятичный счетчик 7, элемент 8 задержки, вход 9 устройства, информационные входы 10 устройства, вход 11 тактовой частоты устройства.. Устройство работает следующим образом. в исходном состоянии двоичные счетчики 5, десятичный счетчик 7 и блок опроса 1 находят ся в нулевом состоянии, при этом на выходах двоичных счетчиков 5 имеется высокий потенциал. При поступлении импульсов тактовой частоты на вход 11 устройства появятся импуль сы на выходе элемента задержки 8 и на выходе элемента И 4. При поступлении на вход 9 устр ойства сигнала начало с каждым импульсом на выходе элемента И 4 будут последовательно появляться импульсы на выходах блока опроса 1. Сигналы с блока опроса Г подключают через первую группу элементов И ко входу шифратора 6 разряды преобразуемого двоичного числа. При наличии в каком-нибудь разряде двоичного числа 1 появляются сигналы на выходах шифратора 6, и в двоичные счетчики 5 запишутсй чйсла, соответствующие весу опрашиваемого в данный момент двоичного разряда. Как только состояние любого из двоичных счетчиков. 5 станет ненулевым, на его выходе снимется высокий потенизйал, па вь1ходе элемента И 4 перестанут появляться импульсы и дальнейший опрос разрядов входного числа прекратится.: После записи кодов чисел в двоичные счетчики 5 начнется добавление этих чисел в- соответствующие разряды десятичного счетчика 7. Добавление Осуществляется методом счета, при этом двоичные счетчики 5 работают на вычитание, а десятичный счетчик 7 на сложение. Нулевой потенциал на выходах двоичных счетчиков 5 разрешает прохождение тактовых импульсов на вход элементов И 3 второй группы при этом на йь1ходах нечетных элементов И 3 импульсы будут появляться одновременно с импульсами тактовой частоты, а на выходах четных элементов И 3 с задержкой. Импульсы с выхода элементов И 3 поступают на вычитание в двоичные счетчики и на сложение в разряды десятичного счетчика 7. При установлении любого счетчика 5 в нулевое состояние на его выходе появится высо ий потенциал, на выходе соответствующего элемента И 3 перестанут появляться импульсы и, таким образом, в соответствующий разряд счетчика 7 будет добавлено число, имевшееся в двоичном счетчике. При установлении всех счетчиков 5 в нулевое состояние будут появляться сигналы на выходе элемента И 4 и продолжится дальнейший опрос двоичных разрядов преобразуемого числа. Величина задержки элемента 8 выбирается больше времени формирования импульса переполнения в разрядах десяттного счетчика 7 с тем, чтобы исключить наложение сигналов переноса с сигналами сложения. Так как в предлагаемом устройстве суммирование чисел во всех разрядах десятичного счетчика осуществляется одновременно, то время преобразования меньше, чем у прототипа. Формула изобретения Преобразователь двоичного кода в десятичный, содержащий десятичный счетчик, двоичные счетчики, блок опроса, первую и вторую группы элементов И, многовходовой элемент И, причем входы элементов И первой группы соединены с информационными входами устройства и с вькодами блока опроса, а выходы через шифратор подключены ко входам двоичных счетчиков, счетные входы которых соединены с выходами элементов И второй группы, выходы двоичных счетчиков соединены с первыми входами элементов И второй группы и с соответствующими входами многовходового элемента И, вторые входы нечетных элементов И второй группЬ подключены ко входу тактовой частоты устройства, разрядные входы десятичного счетчика соедине1п 1 с выходами соответствующих элементов И второй группы, первый вход блока опроса соединен с выходом многовходового элемента И, а второй вход - подключен ко входу устройства, отличающ и и с я тем, что, с целью повышения быстродействия, в него введен элемент задержки, вход которого подключен ко входу тактовой частоты устройства, а выход соединен со вторыми, входами четных элементов И второй груп56918426

пы и с одним из входов многовходового эле-1. Авторское сввдетельство СССР N 432486,

мента И.кл. G 06 F 5/02, 1971.

Источники информации,2. Авторское свидетельство СССР N 525944,

принятые во внимание при экспертизекл. G 06 F 5/02, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в десятичный | 1974 |

|

SU525944A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Устройство для считывания графическойиНфОРМАции | 1974 |

|

SU807349A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU691843A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Статистический анализатор отклонений напряжения сети | 1985 |

|

SU1262524A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU771660A1 |

Авторы

Даты

1979-10-15—Публикация

1976-06-01—Подача