1

Изобретение относится к вычислительной технике и. может быть применено для построния функииоиальных преобразователей и спеииализированнык вычислительных устройств.

. Известен интерполятор, осуществляющий интерполяцию функции полиномами высокого порядка и содержащий устройство двоичного умножения асинхронного типа, двоичный счетчик, сумматор, постоянное, запоминающее устройство (ПЗУ), регистры, адресное устройство, кодирующее устройство, выхоаное устройство, вентильные схемы и блок управления 1 . , Недостатками этого устройства являются большое количество аппаратуры и низкое быстродействие, так как для каждой из функций необходимо хранить в ПЗУ множество заранее определенных параметров, используя которые вычисляется искомая функция путем вьтолнения множества сложных операцнй.

Известен также электронный функциональный генератор с управлением, использующий способ интерполяции по координатам точек перегиба и содержащий блок памяти, интерполятор, компаратор и блок управления 2 .

Недостатками этого устройства являются сложность блока;интерполяции и низкое быст .родействие, так как в устройстве вначале производится последовательный подбор точек перегиба и затем выполняется вычисление по интерполяционной формуле, содержащей сложные операции (типа умножения и деления).

Наиболее близким по технической сущности к изобретению является устройство для Воспроизведения функций,содержащее блок памяти, вход которого соединен f выходом счетчика, вход которого соединен с входом устройства 3 .

Недостатком этого устройства является большое количество оборудования, так как оно содержит четыре регистра, дешифратор и блок памяти емкостьюWop Nбит. и имеет низкое быстродействие, обусловленное множеством пересылок между регистрами, дешифратором и блоком naMSjTH.

Целью изобретения является сокращение объема оборудования и повышение быстродействия устройства.

Достигается это тем, что в устройство введены триггер, два элемента И, элемент g ИЛИ и элемент- НЕ, причем выход блока памэти соединен с первым входом первого элемента И и входом триггера, выход которого соединен с первым входом второго элемента И, второй вход которого соединен че-jy рез элемент НЕ с вторым входом первого . элемента И и входом устройства, выходы п рвого и второго элементов И соединены с входами элемента ИЛИ, выход которого под-( ключей к выходу устройства.j5

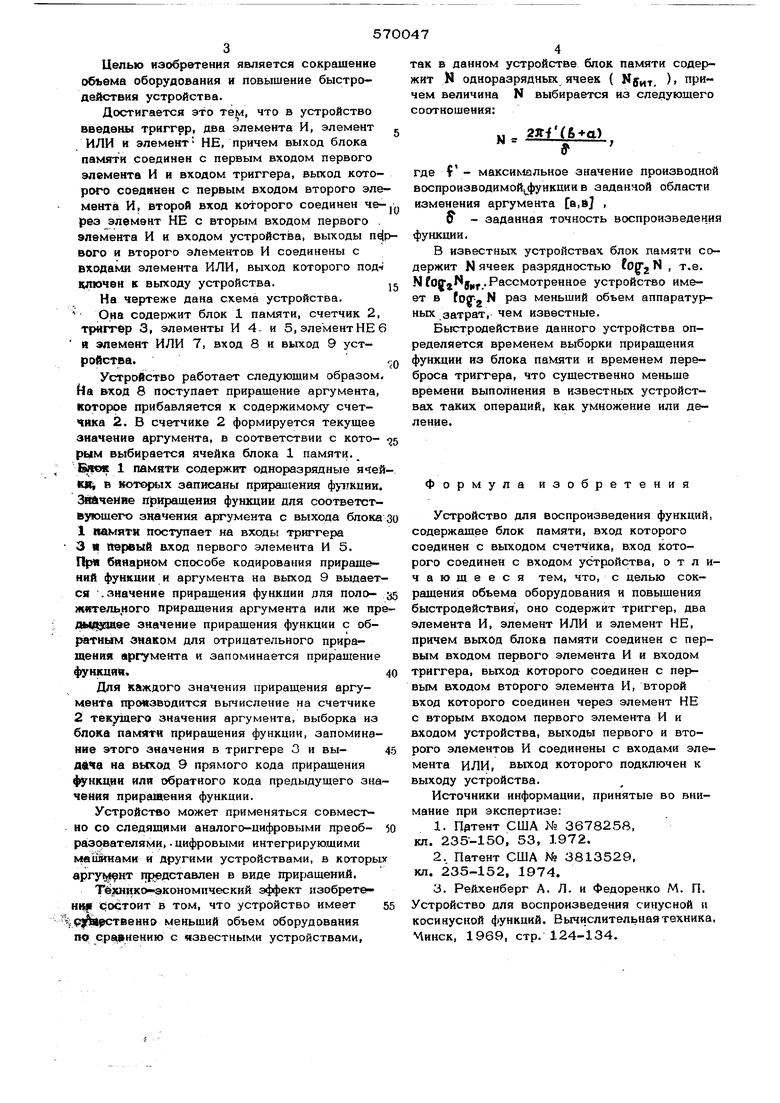

На чертеже дана схема устройства. Она содержит блок 1 памяти, счетчик 2,

триггер 3, элементы И 4. и 5, элемент НЕ 6 я элемент ИЛИ 7, вход 8 и выход 9 устройства.

Устройство работает следующим образом. Йа &ХОД 8 поступает приращение аргумента, которое прибавляется к содержимому счетчика 2. В счетчике 2 формируется текущее значение аргумента, в соответствии с кото- рым выбирается ячейка блока 1 памяти. БЙКЯЕ 1 памяти содержит одноразрядные ячейки; в к торых записаны прирашения функции. 3«1дчеНве приращения функции для соответствующего значения аргумента с выхода блока зо 1 памяти поступает на входы триггера 3 ш первый аход первого элемента И 5. При бинарном способе кодирования приращений функции и аргумента на выход 9 выдается .значение приращения функции для поло- 35 жительного приращения аргумента или же преды заее значение приращения функции с обргатным знаком для отрицательного прирашения аргумента и запоминается приращение ФУНКЦИИ.40

Для каждого значения приращения аргуweHlra производится вычисление на счетчике 2 текущего значения аргумента, выборка из блока памяти приращения функции, запоминание этого значения в триггере О и вы-45 дача на выход 9 прямого кода приращения функции или обратного кода предыдущего значения прирашения функции.

Устройство может применяться совместно со следящими аналого-цифровыми преоб- 50 разователя1у1и цифровыми интегрирующими мвийнами и другими устройствами, в которых apryt HT представлен в виде приращений.

Технико-экономический эффект изобретеН1|}1 (состоит в том, что устройство имеет 55 5 }Й11рственнЕ) меньший объем оборудования п9 срв(9нению с «звестными устройствами,

так в данном устройстве блок памяти содержит N одноразрядных ячеек ( , ) причем величина N выбирается из следующего соотношения:

U - 23ti(b+a} N ,

где f - максимальное значение производной воспроизводимой(ункциив заданной области изменения аргумента а,и ,

- заданная точность воспроизведени функции.

В известных устройствах блок памяти содержит N ячеек разрядностью Ogj N , т.е. N fOfjNj,Рассмотренное устройство имеет в , N раз меньший объем аппаратурных затрат, чем известные.

Быстродействие данного устройства определяется временем выборки приращения функции из блока памяти и временем переброса триггера, что существенно меньше времени выполнения в известных устройствах таках операций, как умножение или деление.

Формула изобретения

Устройство для воспроизведения функций, содержащее блок памяти, вход которого соединен с выходом счетчика, вход которого соединен с входом устройства, отличающееся тем, что, с целью сокращения объема оборудования и повышения быстродействия, оно содержит триггер, два элемента И, элемент ИЛИ и элемент НЕ, причем выход блока памяти соединен с первым входом первого элемента И и входом триггера, выход которого соединен с первым входом второго элемента И, второй вход которого соединен через элемент НЕ с вторым входом первого элемента И и входом устройства, выходы первого и второго элементов И соединены с входами элемента ИЛИ, выход которого подключен к выходу устройства.

Источники информации, принятые во внимание при экспертизе:

1.Патент США № 3678258, кл. 235-15О, 53, 1972.

2.Патент США № 3813529, кл. 235-152, 1974.

3.Рейхенберг А. Л. и Федоренко М. П. Устройство для воспроизведения синусной и косинусной функций. Вычислительная техника, Минск, 1969, стр. 124-134.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатный линейно-круговой интерполятор | 1984 |

|

SU1156008A1 |

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Линейный интерполятор | 1985 |

|

SU1282084A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| Цифровой линейный интерполятор | 1987 |

|

SU1434406A1 |

| Цифровой линейный интерполятор | 1985 |

|

SU1254507A1 |

| Интерполятор | 1986 |

|

SU1396140A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

Авторы

Даты

1977-08-25—Публикация

1976-01-30—Подача