ков буферной памяти и управления буферной памятью.

Кроме того, блок задания ускоренной работы буферной памяти содержит два триггера, выходы которых подключены соответственно к первому и второму выходам блока, единичные входы - соответственно к выходам первого и второго элементов И, нервые входы которых соединены с выходом третьего элемента И, входами подключенного через элементы НЕ к входам блока с первого по четвертый и к нятому, шестому и восьмому входам блока, девятый вход которого соединен с вторыми входами нервого и второго элементов И, седьмой вход - с третьим входом первого элемента И, десятый вход - с нулевыми входами триггеров.

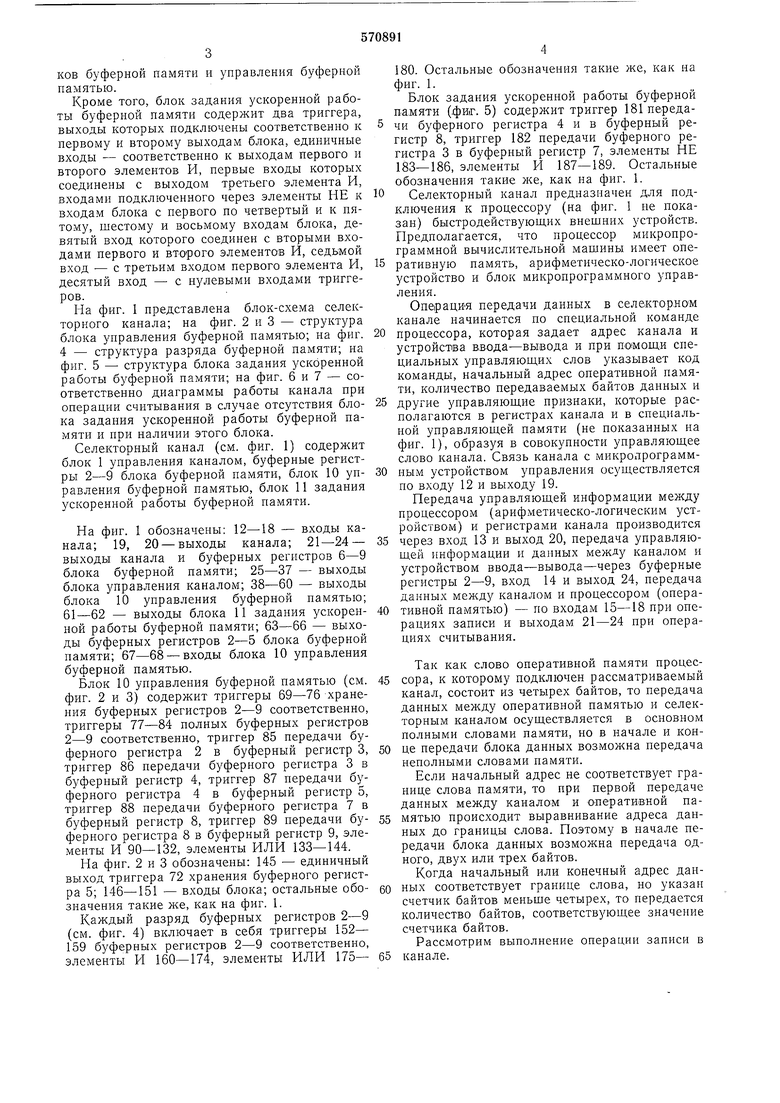

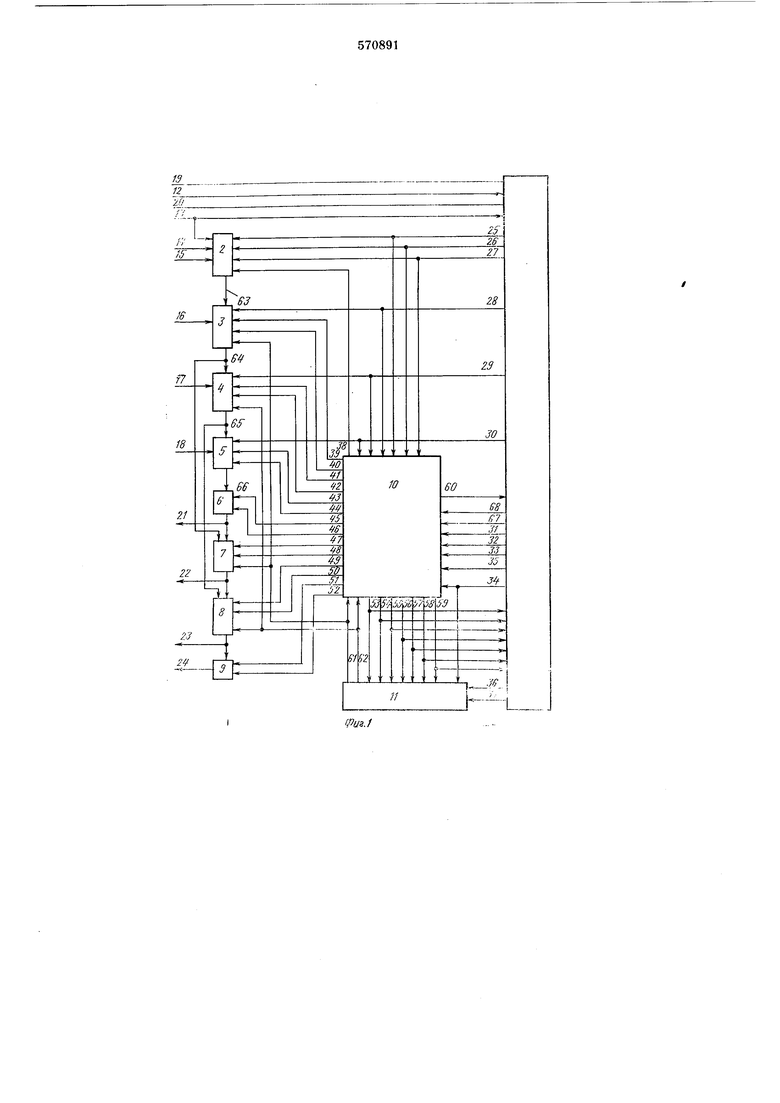

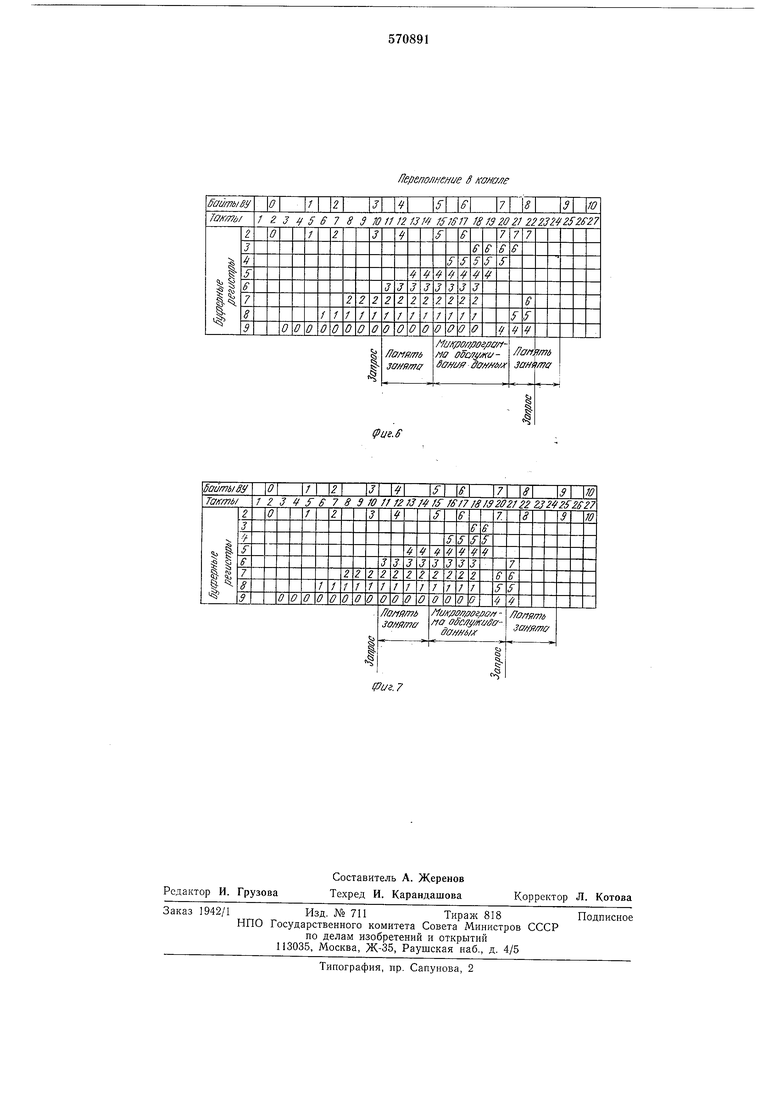

На фиг. 1 представлена блок-схема селекторного канала; на фиг. 2 и 3 - структура блока управления буферной памятью; на фиг. 4 - структура разряда буферной памяти; на фиг. 5 - структура блока задания ускоренной работы буферной памяти; на фиг. 6 и 7 - соответственно диаграммы работы канала при операции считывания в случае отсутствия блока задания ускоренной работы буферной памяти и при наличии этого блока.

Селекторный канал (см. фиг. 1) содержит блок 1 управления каналом, буферные регистры 2-9 блока буферной памяти, блок 10 управления буферной памятью, блок И задания ускоренной работы буферной памяти.

На фиг. 1 обозначены: 12-18 - входы канала; 19, 20 - выходы канала; 21-24- выходы канала и буферных регистров 6-9 блока буферной памяти; 25-37 - выходы блока управления каналом; 38-60 - выходы блока 10 управления буферной памятью; 61-62 - выходы блока 11 задания ускоренной работы буферной памяти; 63-66 - выходы буферных регистров 2-5 блока буферной памяти; 67-68 - входы блока 10 управления буферной памятью.

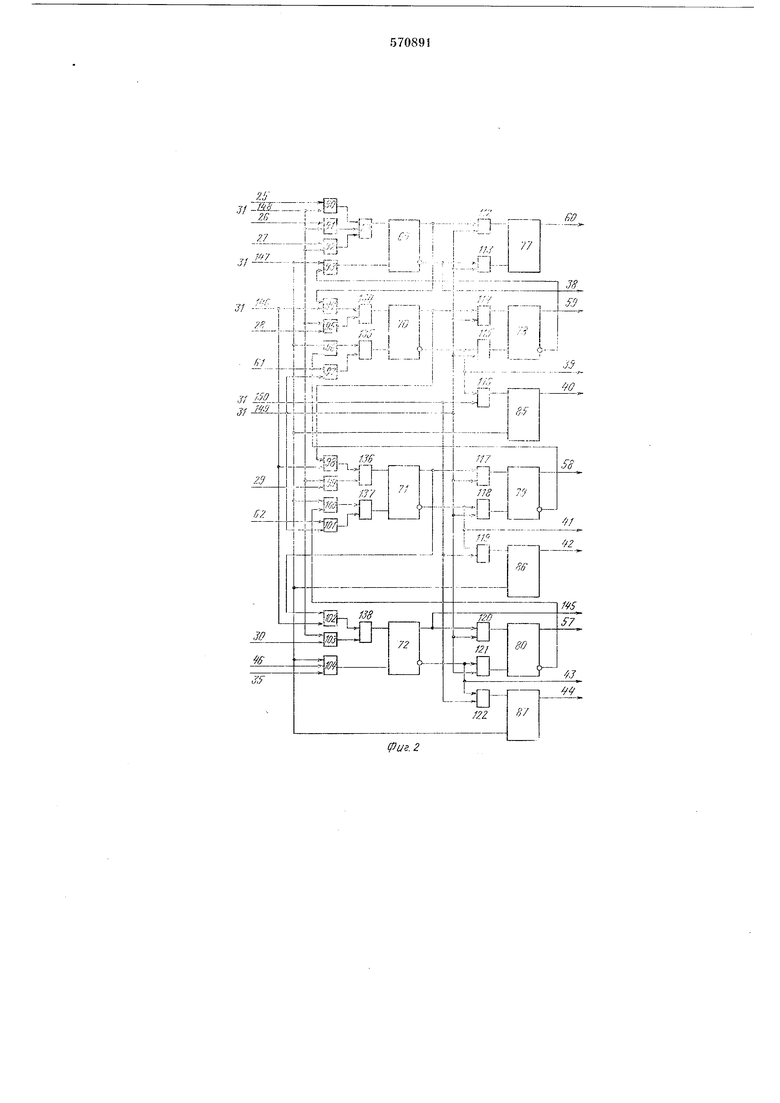

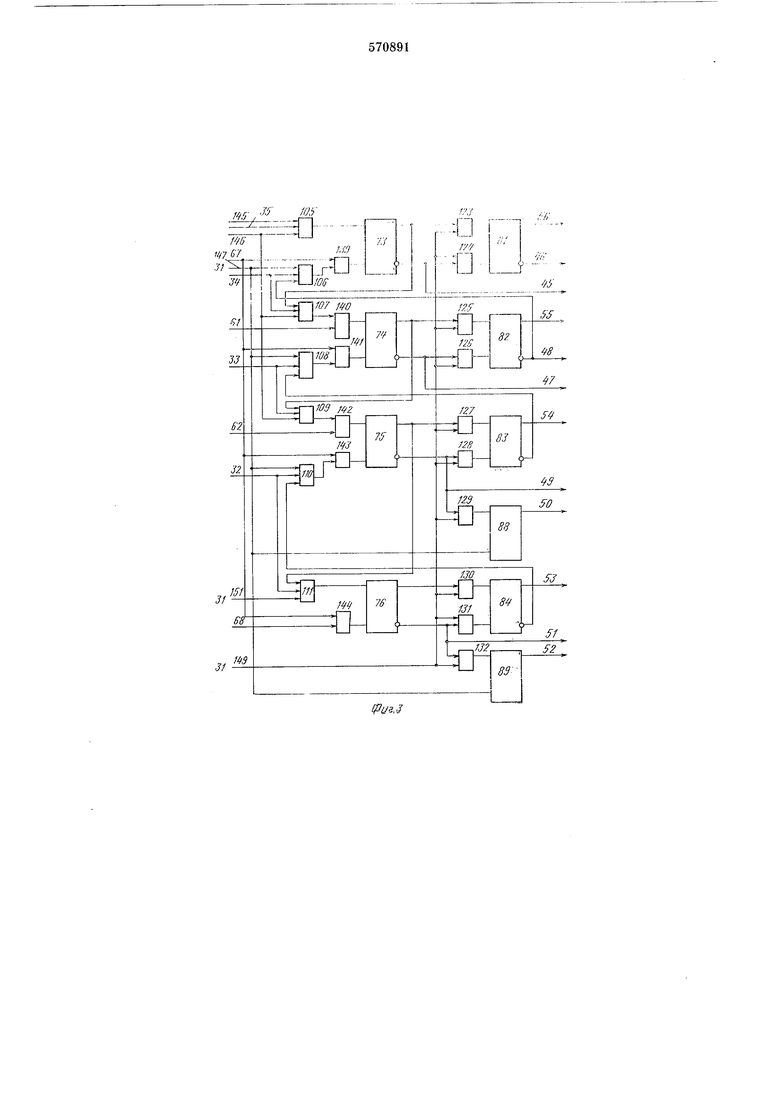

Блок 10 управления буферной памятью (см. фиг. 2 и 3) содержит триггеры 69-76 хранения буферных регистров 2-9 соответственно, триггеры 77-84 полных буферных регистров 2-9 соответственно, триггер 85 передачи буферного регистра 2 в буферный регистр 3, триггер 86 нередачи буферного регистра 3 в буферный регистр 4, триггер 87 передачи буферного регистра 4 в буферный регистр 5, триггер 88 передачи буферного регистра 7 в буферный регистр 8, триггер 89 нередачи буферного регистра 8 в буферный регистр 9, элементы И 90-132, элементы ИЛИ 133-144.

На фиг. 2 и 3 обозначены: 145 - единичный выход триггера 72 хранения буферного регистра 5; 146-151 - входы блока; остальные обозначения такие же, как на фиг. 1.

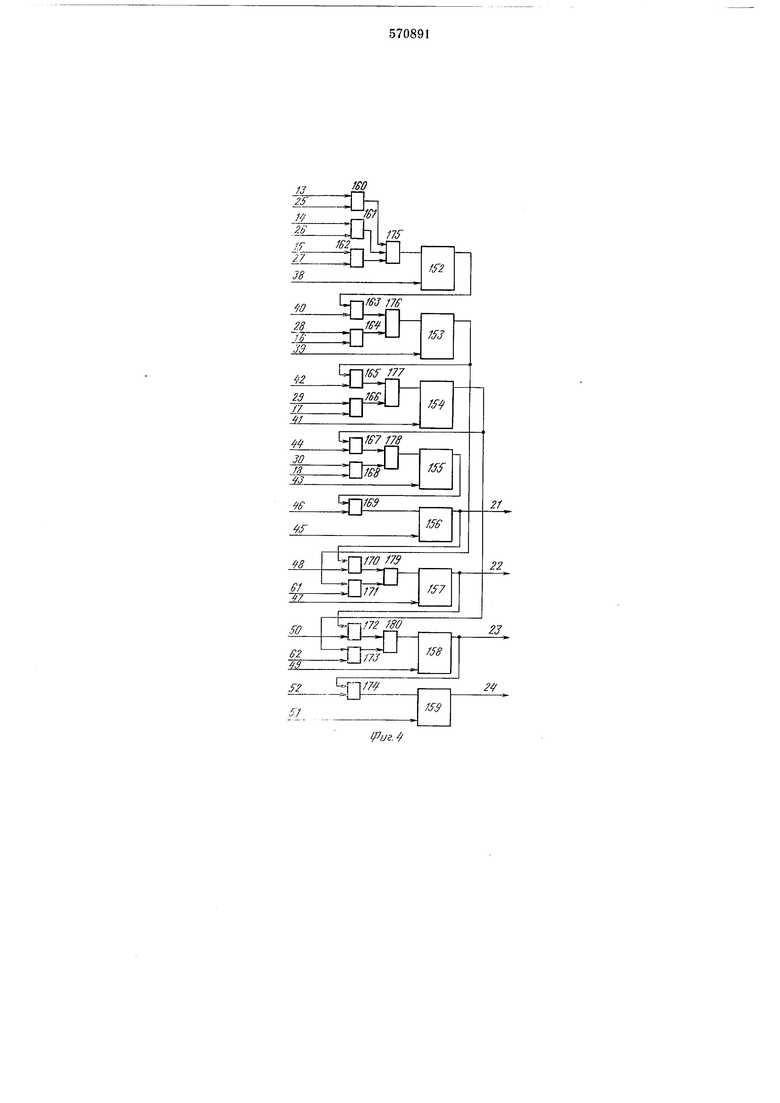

Каждый разряд буферных регистров 2-9 (см. фиг. 4) включает в себя триггеры 152- 159 буферных регистров 2-9 соответственно, элементы И 160-174, элементы ИЛИ 175-

180. Остальные обозначения такие же, как на фиг. 1.

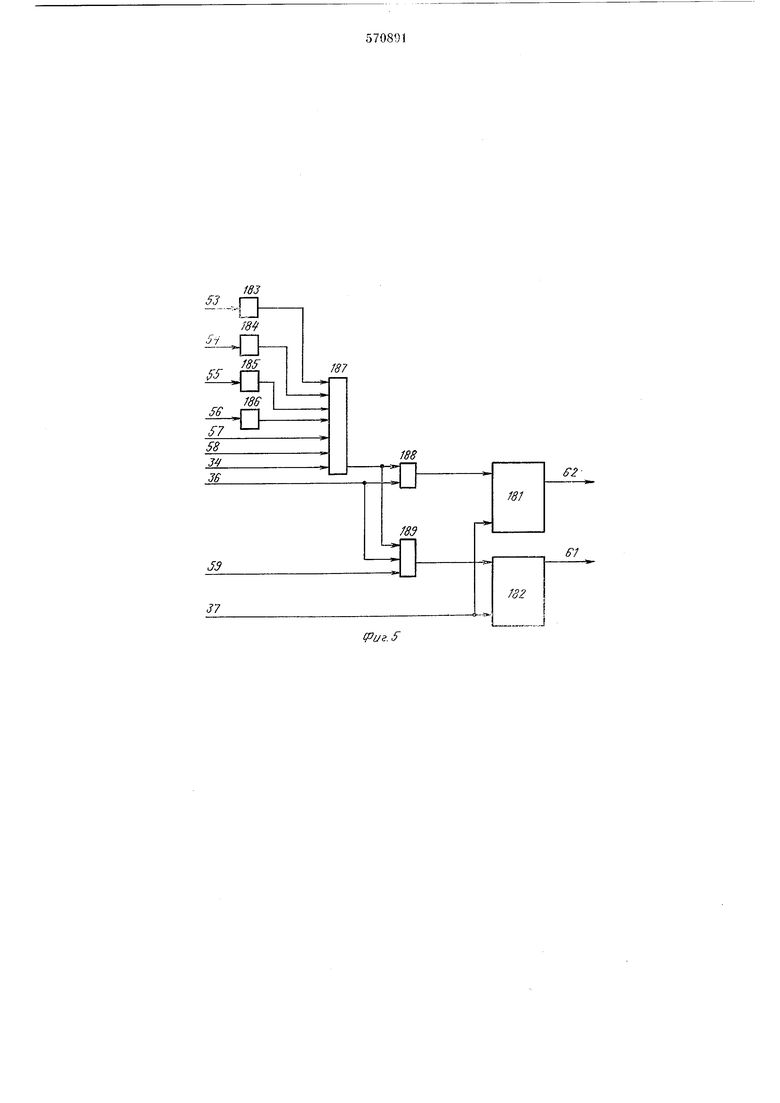

Блок задания ускоренной работы буферной памяти (фиг. 5) содержит триггер 181 передачи буферного регистра 4 и в буферный регистр 8, триггер 182 передачи буферного регистра 3 в буферный регистр 7, элементы НЕ 183-186, элементы И 187-189. Остальные обозначения такие же, как на фиг. 1.

Селекторный канал предназначен для подключения к процессору (на фиг. 1 не показан) быстродействующих внешних устройств. Предполагается, что процессор микропрограммной вычислительной машины имеет оперативную память, арифметическо-логическое устройство и блок микропрограммного управления.

ОперациЯ передачи данных в селекторном канале начинается по специальной команде процессора, которая задает адрес канала и устройства ввода-вывода и при специальных управляющих слов указывает код команды, начальный адрес оперативной памяти, количество передаваемых байтов данных и другие управляющие признаки, которые располагаются в регистрах канала и в специальной управляющей памяти (не показанных на фиг. 1), образуя в совокупности управляющее слово канала. Связь канала с микропрограммным устройством управления осуществляется по входу 12 и выходу 19.

Передача управляющей информации между процессором (арифметическо-логическим устройством) и регистрами канала производится через вход 13 и выход 20, передача управляющей информации и данных между каналом и устройством ввода-вывода-через буферные регистры 2-9, вход 14 и выход 24, передача данных между каналом и нроцессором (онеративной памятью) - по входам 15-18 при операциях записи и выходам 21-24 при операциях считывания.

Так как слово оперативной памяти процессора, к которому подключен рассматриваемый канал, состоит из четырех байтов, то передача данных между оперативной памятью и селекторным каналом осуществляется в основном полными словами памяти, но в начале и конце передачи блока данных возможна передача неполными словами намяти.

Если начальный адрес не соответствует границе слова намяти, то при первой передаче данных между каналом и оперативной памятью происходит выравнивание адреса данных до границы слова. Поэтому в начале передачи блока данных возможна передача одного, двух или трех байтов.

Когда начальный или конечный адрес данных соответствует границе слова, но указан счетчик байтов меньше четырех, то передается количество байтов, соответствующее значение счетчика байтов.

Рассмотрим выполнение операции записи в канале.

Запрос на микропрограммное прерывание для выполнения микропрограммы обслуживания данных вырабатывается в блоке 1 управления каналом в тот момент, когда освобождаются четыре буферных регистра 2-5 пли когда освобождаются любые три буферных регистр а 2-5 и хотя бы один буферный регистр 6-9, так как к моменту передачи байтов данных буферные регистры 2-5 становятся «пустыми. Микропрограмма обслуживания данных обеспечивает необходимую корректировку управляющего слова канала и по входам 15-18 передачу данных из оперативной памяти в канал. Если передается полное слово, то байты данных принимаются в буферные регистры 2-5, а если - неполное слово, например два байта, то в зависимости от адреса данных байты принимаются в буферные регистры 2 и 3, 3 и 4, 4 и 5. Таким образом, каждому байту слова памяти соответствует свое место в буферных регистрах 2-5. После приема из оперативной памяти в буферные регистры 2-5 байты данных сдвигаются до буферного регистра 9, откуда они выдаются в устройство ввода-вывода, после чего сбрасывается по выходу блока 1 управления каналом регистр 9. Операция записи в канале обычно заканчивается тогда, когда счетчик байтов достигает нуля, после передачи всех байтов данных из буферных регистров 2-9 в устройство ввода-вывода.

При выполнении операции считывания, байты данных с входных шин интерфейса принимаются по входу 14 в буферный регистр 2 и продвигаются к буферным регистрам 9-6.

Если адрес данных соответствует границе слова {код состояния двух младших разрядов адреса равен 00) и счетчик байтов больше или равен четырем, то нулевой, первый, второй и третий байты данных продвигаются соответственно в буферные регистры 9, 7, 8 и 6. А есЛИ| адрес данных соответствует границе слова и счетчик байтов меньше четырех, например два, то нулевой и первый байты данных продвигаются соответственно в буферные регистры 9 и 8, после чего на выходе 35 блока 1 управления каналом вырабатывается отрицательный сигнал полного слова в буферных регистрах 6-9, запреш,аюш,ий продвижение байтов данных с буферных регистров 2-5 в буферные регистры 6-9.

Когда адрес данных не соответствует границе слова, т. е. код состояния двух младших разрядов адреса равен 01, 10 или 11, то первый продвигаемый байт данных располагается в соответствии с адресом в буферных регистрах 8, 7 или 6, для чего в блоке 1 управления каналом на выходах 32, 33 или 34 вырабатываются отрицательные сигналы, запреш,ающие продвижение байтов даипых соответственно в буферные регистры 9, 8 или 7. После заполнения необходимого количества буферных регистров, устанавливается на выходе 35 блока 1 отрицательный сигнал полпого слова в буферных регистрах 6-9, запрещающий продвижение байтов данных в регистры 6-9.

Запрос на микропрограммное прерывание для выполнения микропрограммы обслуживания данных при передаче в оперативную память полного слова вырабатывается при заполнении буферных регистров 7-9 и хотя бы одного буферного регистра 2-6, а при передаче неполного слова - при заполнении необходимого количества байтов в буферных регистрах 6-9. Микропрограмма обслул ивания данных производит необходимую корректировку управляющего слова канала и по выходам 21-24 передачу байтов данных в оперативную

память, после чего сбрасывает буферные регистры 6-9 по выходу блока 1 управления каналом. Операция считывания в канале заканчивается, когда счетчик байтов становится равным количеству байтов в буферных регистрах

2-9.

Машинный такт процессора, в который входит предлагаемый канал, состоит из четырех основных тактовых синхроимпульсов (ТИь ТИз, ТИз, ТИ4) и четырех задержанных тактовых синхроимпульсов (THi , ТИ 7И.

33

™4j.

Рассмотрим работу буферных регистров при операции считывания (фиг. 2, 3, 4). По сигналу приема с входа 14 сиихроимп)льсом с входа 148 (ТИз ) через элементы И 91, ИЛИ 133 устанавливается триггер 69 хранения буферного регистра 2, снимается сигнал с выхода 38 сброса буферного регистра 2, тем самым разрешая занесение байта данных с входа 14 через элементы И 161, ИЛИ 175 в буферный регистр 2. В конце такта синхроимпу льсов с входа 149 (ТИ4) устанавливается через элемент И 112 триггер 77 полного буферного регистра 2.

В следующем машинном такте, если код состояния двух младших разрядов адреса равен 00, синхроимпульсами с входов 146, 151 (ТИ или ТИ1 , Tnj или ТИ2) устанавливаются через элементы И 94, 98, 102, 105, 107, 109, 111 поочередно триггеры 70-76 хранения буферных регистров 3-9, снимаются поочередно сигналы с выходов 39, 41, 43, 45, 47, 49, 51 сброса буферных регистров, тем самым разрешая сдвиг байта данных с буферного регистра 2 в буферные регистры 3-9, если перед этим они были «пусты. Сдвиг байта данных осуществляется по управляющим сигналам с выходов 40, 42, 44, 46, 48, 50, 52, вырабатываемым блоком 10. Последующим тактовым синхроимпульсом с входа 147 (ТИ2) сбрасывается через элементы И 93, 96, 100, 104, 106, 108, 110 каждый предыдуший триггер хранения по последующему пустому буферному регистру.

В конце такта синхроимпульсом с входа 149 (ТИ4) устанавливается через элемент И 130 триггер 84 полного буферного регистра 9 и сбрасывается через элемент И 113 триггер 77 полного буферного регистра 2. А если код

состояния лТ,вух младших разрядов равен 01,

10, 11, то байт данных сдвигается соот ветственно до буферных регистров 9, 8, 7, так как на выходе блока 1 устанавливаются соответственно отрицательные сигналы с выходов 32, 33, 34, запрещающие установку последующего триггера 76, 75, 74 хранения и сброс предыдущего триггера 76, 74, 73.

В любом случае, при передаче полного или неполного слова из канала в оперативную память, после заполнения необходимого количества байтов данных в буферных регистрах 6-9, устанавливается на выходе 35 блока 1 отрицательный сигнал полного слова, который запрещает установку триггера 73 хранения буферного регистра 6 и сброс триггера 72 хранения буферного регистра 5. Одновременно с установкой отрицательного сигнала с выхода 35 всегда устанавливается отрицательный сигнал с выхода 34.

Микропрограмма обслуживания данных корректирует управляющее слово канала, передает содержимое буферных регистров 6-9 в оперативную память, сбрасывает буферные регистры 6-9 и в конце выполнения анализирует условие зацепления по данным, когда счетчик байтов стал нулевым при указанном признаке зацепления по данным в канале. Когда условия цепочки данных нет, то в конце микропрограммы обслуживания данных сбрасываются отрицательные сигналы с выходов 35, 34 и последующие байты данных сдвигаются к буферным регистрам 6-9. Если условие зацепления по данным выполняется, то микропрограмма обслуживания данных не заканчивается, а сигнал с выхода 35 снимается и производится загрузка нового управляющего слова (адреса данных, счетчика байтов и других признаков) в канал, после чего осуществляется возврат к прерванной микропрограмме. Таким образом за время выполнения зацепления по данным следующий байт данных продвигается только до буферного регистра 7, так как отрицательный сигнал с выхода 34 остается включенным. После зацепления байты данных располагаются в буферных регистрах 6-9 в соответствии с состоянием младших раз1рядов в адрес данных.

При операциях записи отрицательные сигналы с выходов 32-35 не включатся и на работу блока 10 управления буферной памятью не влияют.

Блок 11 задания ускоренной работы буферной памяти ( фиг. 5) работает следующим образом.

Когда освобол даются нли свободны буферные регистры 6-9 и заполнены буферные регистры 4 и 5 в случае отсутствия отрицательного сигнала с выхода 34, то включается элемент И 187 и синхроимпульсом с выхода 36 (ТИз) через элемент И 188 устанавливается триггер 181 передачи буферного регистра 4 в буферный регистр 8. А если заполнен буферный регистр 3, то через элемент И 189 одновременно устанавливается регистр 182 передачи буферного регистра 3 в буферный регистр 7. Таким образом в одном мащинном такте производится сдвиг содерл имого буферного регистра 5 в буферный регистр 9 и передача буферных регистров 4, 3 соответственно в буферные регистры 8, 7. Отметим, что передача буферного регистра 3 в буферный регистр 7 возможна только тогда, когда заполнены регистры 4 и 5, а буферного регистра 4 в регистр 8, когда заполнен буферный регистр 5.

Указанные передачи буферных регистров позволяют быстрее освобождать буферные регистры 2-5 при операциях считывания и быстрее загружать эти же регистры в операциях

записи или, другими словами, блок задания ускоренной работы буферной памяти включается в работу, когда устройство ввода «опережает канал или когда канал «отстает от устройства вывода. Поэтому при относительно

малой скорости передачи данных в операциях счнтывапия блок 11 не включается в работу вообще, а в операциях записи включается только в начале передачи блока данных, когда буферные регистры 6-9 не заполнены, поеле передачи байтов данных из оперативной памяти в буферные регистры 2-5.

Во время зацепления по данным в онерациях считывания блок 11 задания ускоренной работы буферной памяти не включается в работу, так как отрицательный сигнал с выхода 34 блокирует включение элемента И 187.

На фит. 6 представлена диаграмма работы канала при операции считывания в случае отсутствии блока 11 задания ускоренной работы

буферной памяти в канале, а на фиг. 7 - с блоком 11. Внещнее устройство (ВУ) передает байты в канал со скоростью 650 кб/с. Длительность мащинного такта равна 600 не, длительность микропрограммы обслуживания данных - 6 тактам, время ожидания освобождения оперативной памяти - 4 тактам. Как видно из фиг. 6, канал не успевает очищать буферные регистры 6-9 и сдвигать байты с регистров 2-5 с такой скоростью передачи данных. Очевидно, что для обеспечения такой скорости канала необходимо было бы увеличить количество буферных регистров, что привело бы к увеличению оборудования, усложнению схемы счета байтов в буферных регистрах, усложнению схемы формирования запроса.

Введение блока 11 задания ускоренной работы буферной памяти позволяет увеличить пропускную способность канала ЭВМ. ЕС-1022

с 500-550 кб/с до 650-700 кб/с при машинном также соответственно 600-650 не. Этот же результат можно было бы получить введя в канал дополнительно два буферных регистра. Но это в свою очередь не увеличило бы

более пропускную способность канала 650- 700 кб/с даже при сокращении микропрограммы обслуживания данных до цикла оперативной памяти (4 такта), что обеспечивает блок 11 задания ускоренной работы буферной памяти.

При необходимости аналогичным образом можно сделать передачу буферного регистра 2 в буферный регистр 6.

Формула изобретения

1. Селекторный канал, содержащий блок управления каналом, .соединенный первым и вторым входами, первым и вторым выходами соответственно с первым и вторым входами и первым и вторым выходами канала, третий, четвертый, пятый, шестой и седьмой входы и третий, четвертый, пятый и шестой выходы которого соединены с соответствующими входами и выходами блока буферной памяти, блок управления буферной памятью, соединенный двухсторонними связями с блоком управления каналом, выходы которого и выходы блока управления буферной памятью подключены к соответствующим входам блока буферной памяти, от л и ч а ю ил и и ся тем, что, с целью повышения быстродействия, в него введен блок задания ускоренной работы буферной памяти, входы которого с первого по десятый соединены с соответствующими выходами блоков управления буферной памятью и управления каналом, первый и второй выходы подключены к

соответствующим входам блоков буферной памяти и управления буферной памятью.

2. Селекторный канал поп. 1, отличающийся тем, что блок задания ускоренной работы буферной памяти содержит два триггера, выходы которых подключены соответственно к первому и второму выходам блока, единичные входы - соответственно к выходам первого и второго элементов И, первые входы которых соединены с выходом третьего элемента И, входы которого подключены соответственно через элементы НЕ к входам блока с первого по четвертый и к пятому, шестому и восьмому входам блока, девятый вход которого соединен с вторыми входами первого и второго элементов И, седьмой вход - с третьим входом первого элемента И, десятый вход - с нулевыми входами триггеров.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3400371, кл. 340-172.5, 1968.

2.Патент Великобритании № 1048525, кл. G 4А, 1966.

S3

28

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Селекторный канал | 1974 |

|

SU525081A1 |

| Устройство для управления каналами | 1976 |

|

SU641436A1 |

| Устройство для управления диагностикой каналов | 1973 |

|

SU526876A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Селекторный канал | 1973 |

|

SU517019A1 |

е

17

18

з1

JfO

fl

66

2

3

1

fB

7

8

f3 Ж

-IL J2

29

30

60

67

32 33 J5

J4

r68S9

Ш

-I ./ -. i

лж:1г::;:;Пй Ьт

.771 „Ьц j-i--i

щ-7|---i--J

-----7 i

Г

.

П ill

i j I i

RO

J8

-4j I

-I .r58/7 лГ/

--П- 1j

/// f/

/«80

.

fZ

Авторы

Даты

1977-08-30—Публикация

1975-10-22—Подача