(54) СЕЛЕКТОРНЫЙ КАНАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Устройство для обмена данными между оперативной памятью и внешним устройством | 1984 |

|

SU1180908A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Селекторный канал | 1975 |

|

SU570891A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

1

Изобретение относится к вычислительной технике, в частности к селекторным каналам вычислительных машин и может быть использовано апя управления обменом информацией междувнешними устройствами процессором.

Известен селекторный канал, содержащий блок управления каналом, блок буферных решстров, первые и вторые входы которых соединены соответственно с первым третьим, вторым, четвертым входами канала, первый, второй, третий, четвертый выходы которого соединены соответственно с первым выходом блока упрявления каналом и вторым выходом блока буферных регистров, вторым выходом блока управления каналом, первым выходом блока буферных регистров, выходом коммутатора считывания (обратного считывания), первый вход которого и первые входы регистра команд и блока управления блоком буферных регистров соединены соответственно с выход регистра команд и третьим выходом блока управления , третий вход которого соединен с выходом регистра команд, вторые входы регистрг команд и коммутатора считывания (обратного считывания) соединены со вторым выходом блока буферных регистров, третий и четвертый входы которого соединены соотБетстьенно с первым входом канала и первым ВЬЕХОДОМ блока управления блоком буферных регистров.

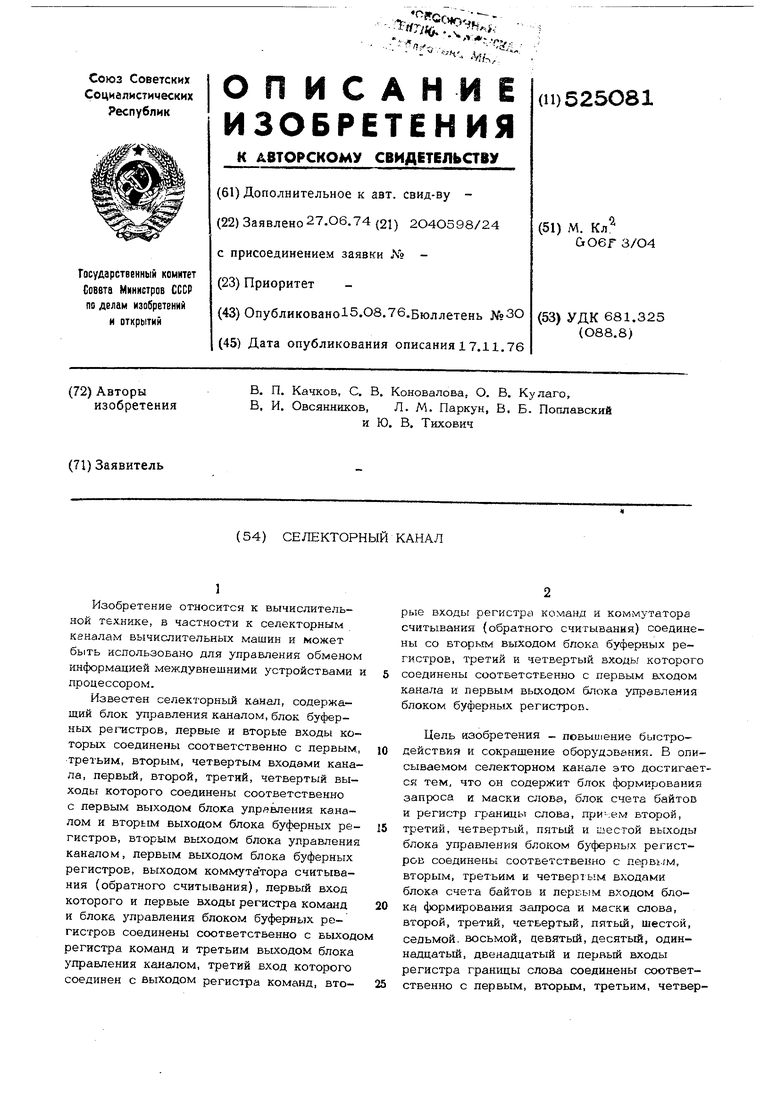

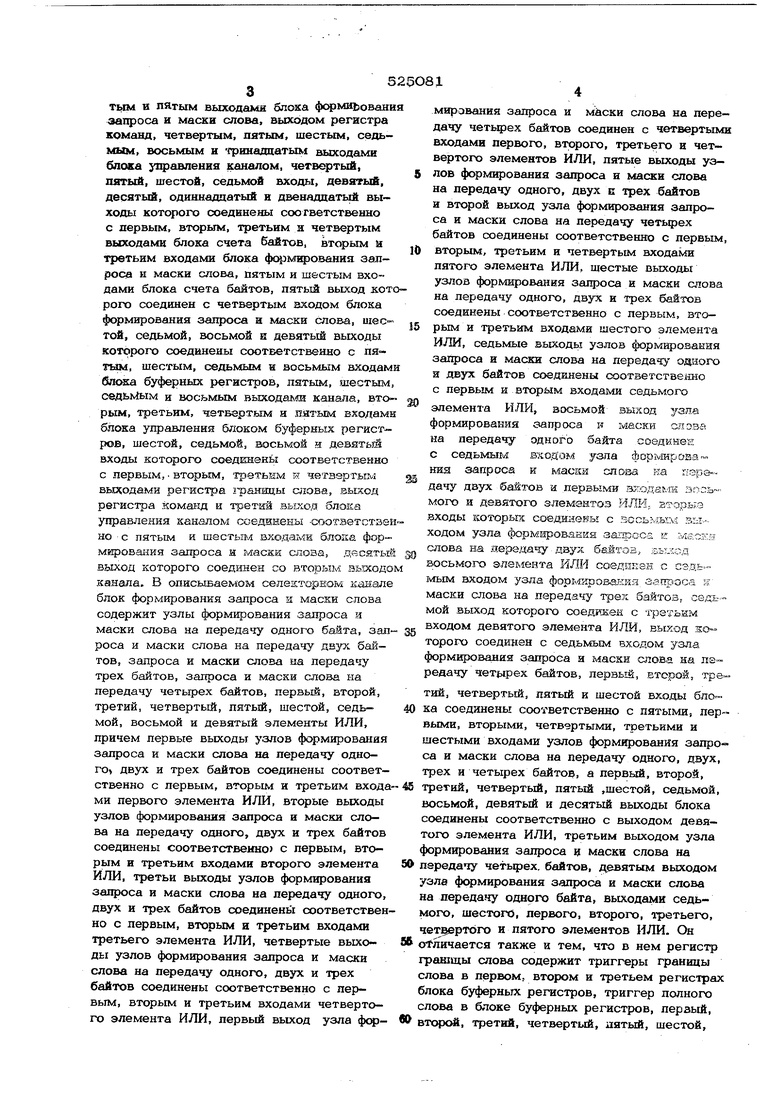

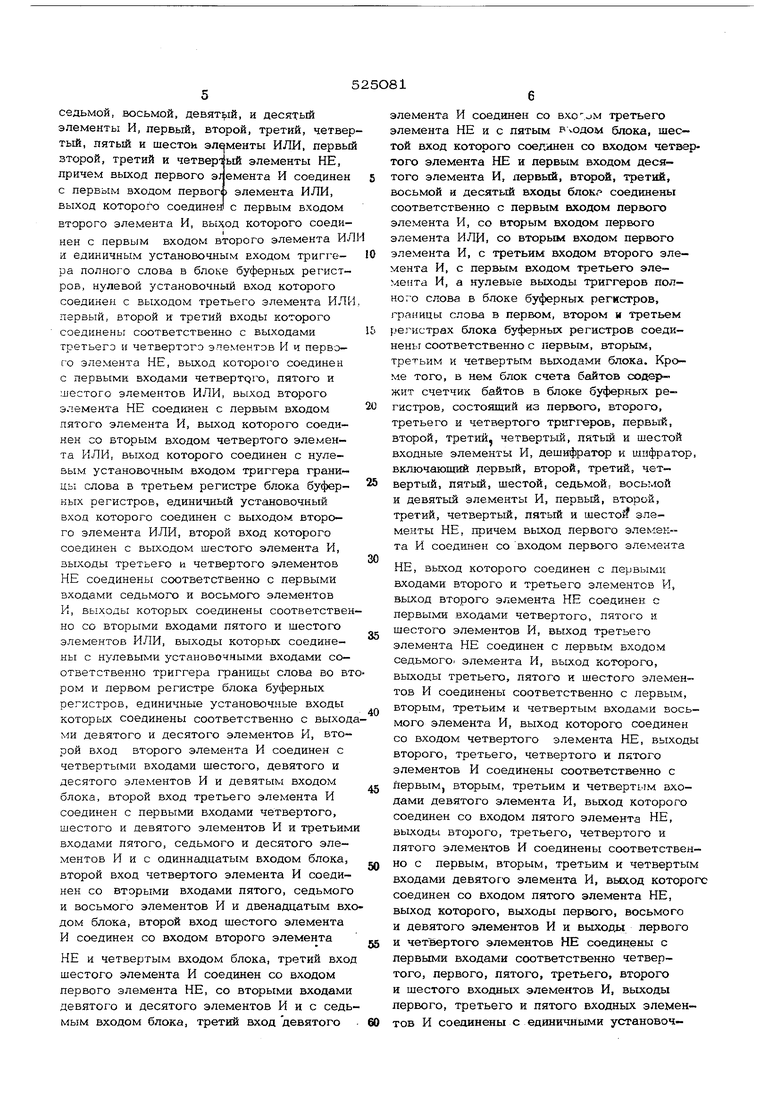

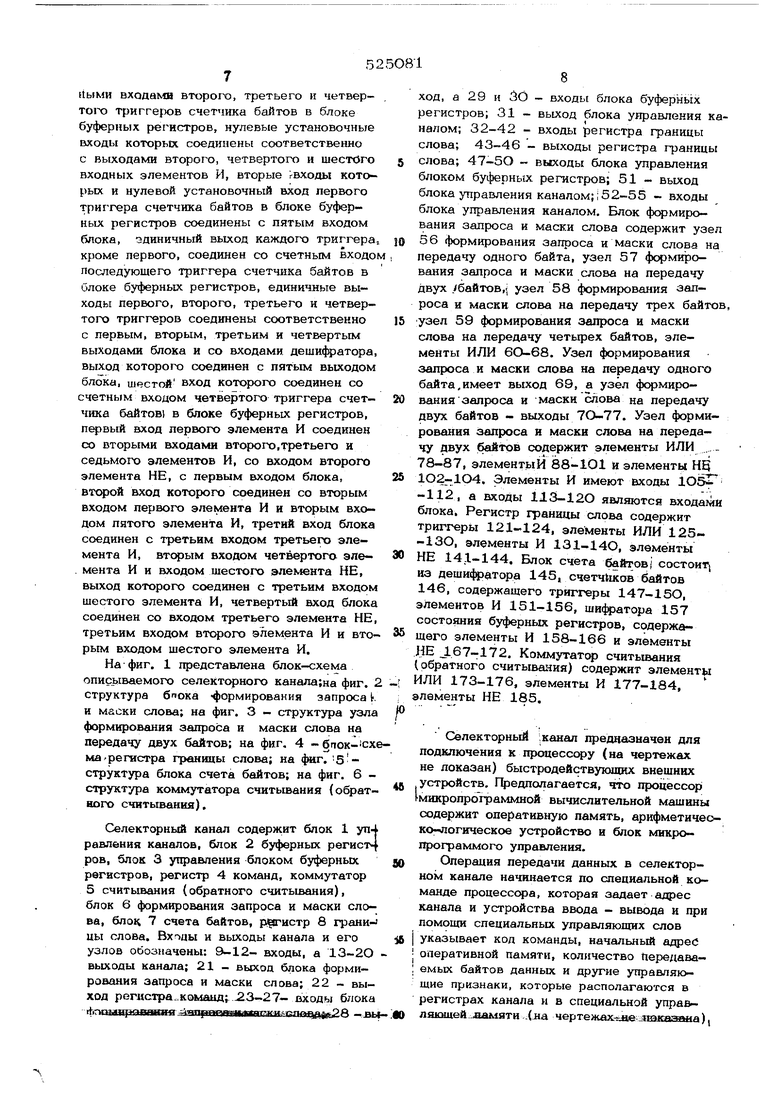

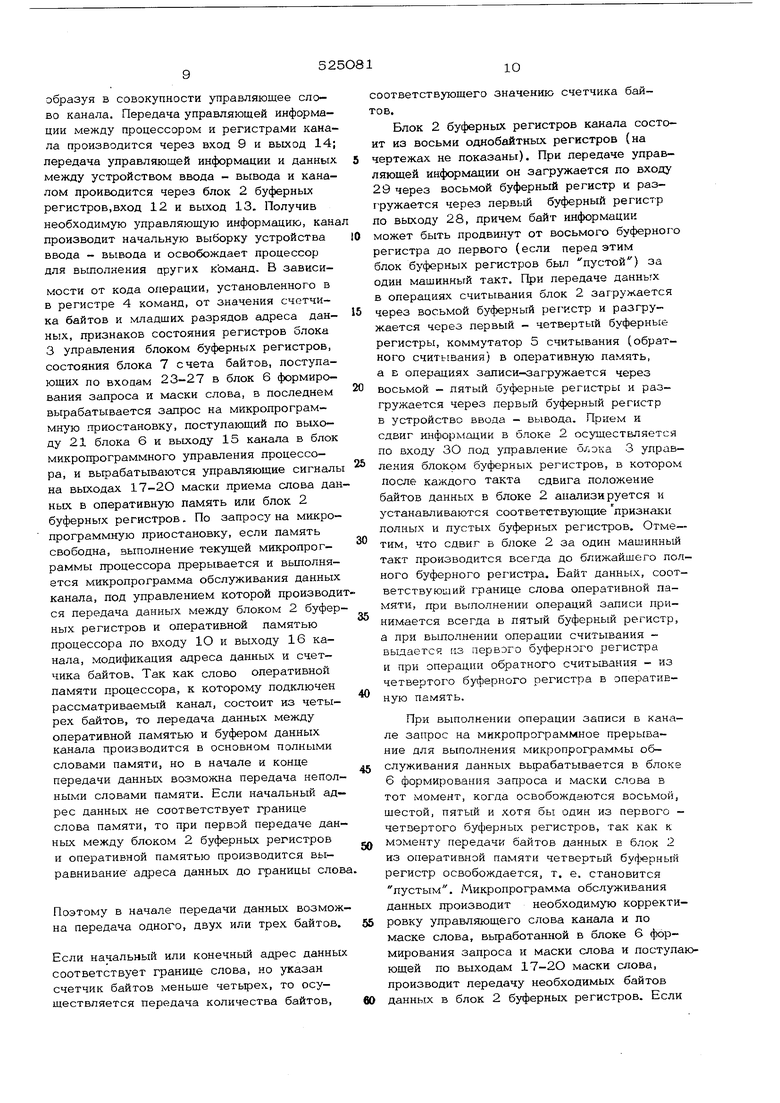

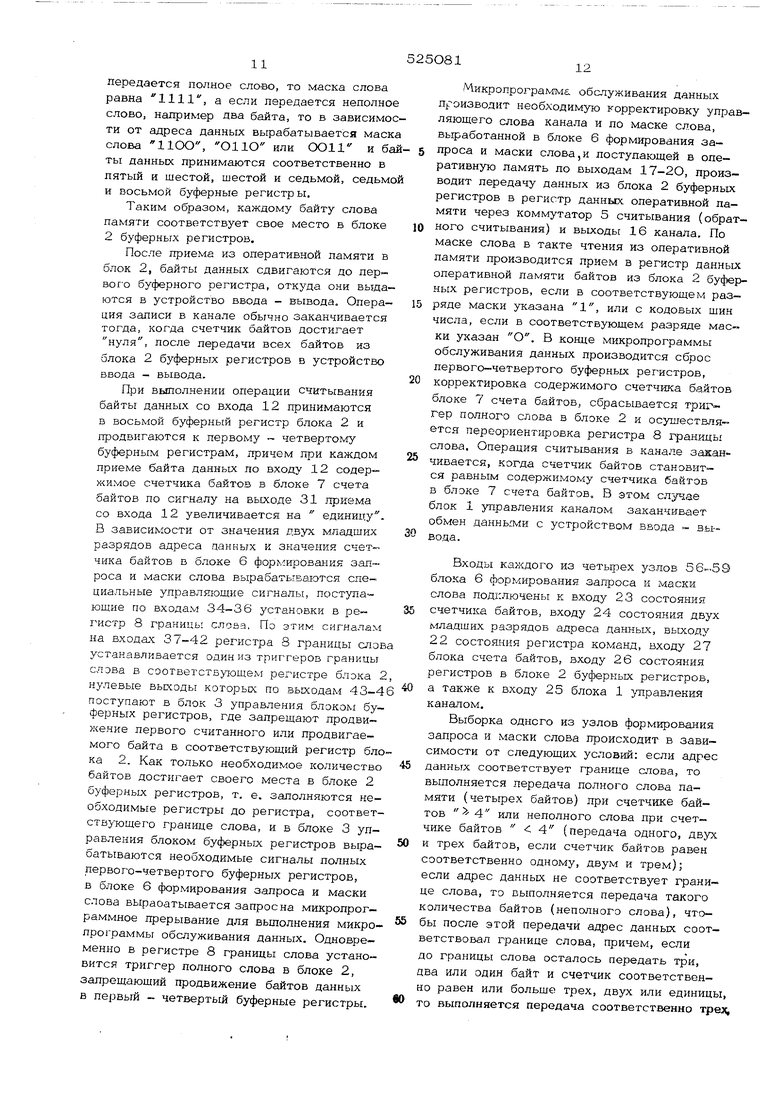

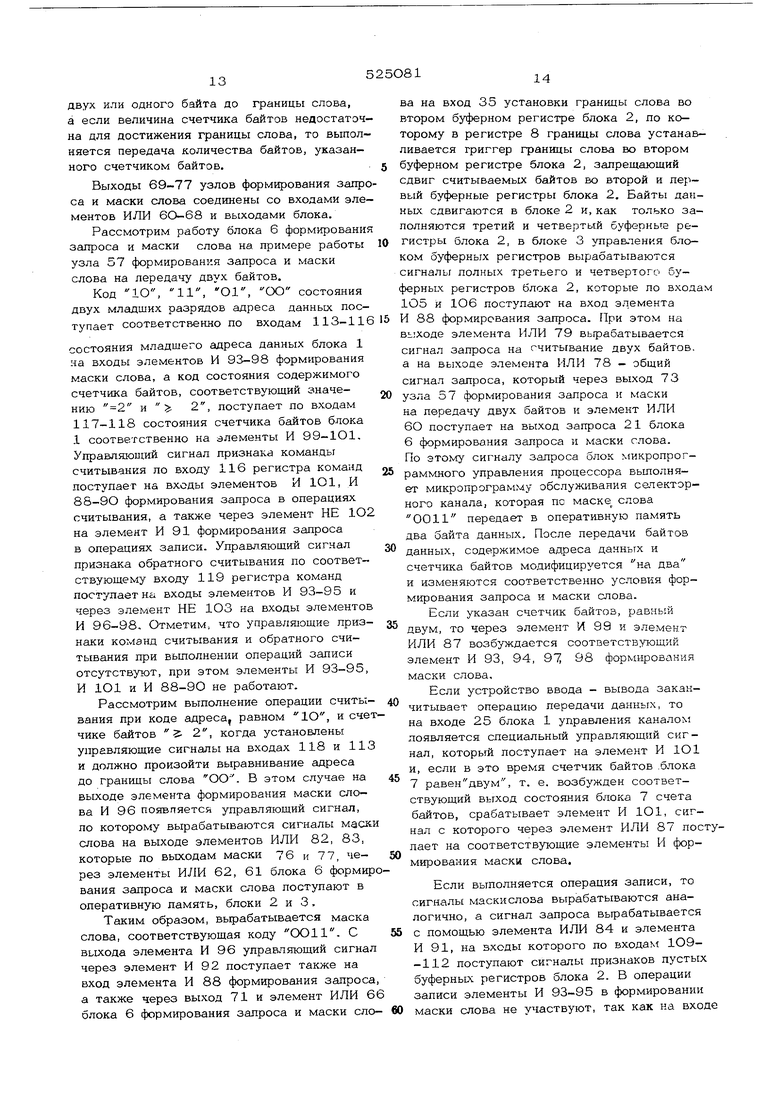

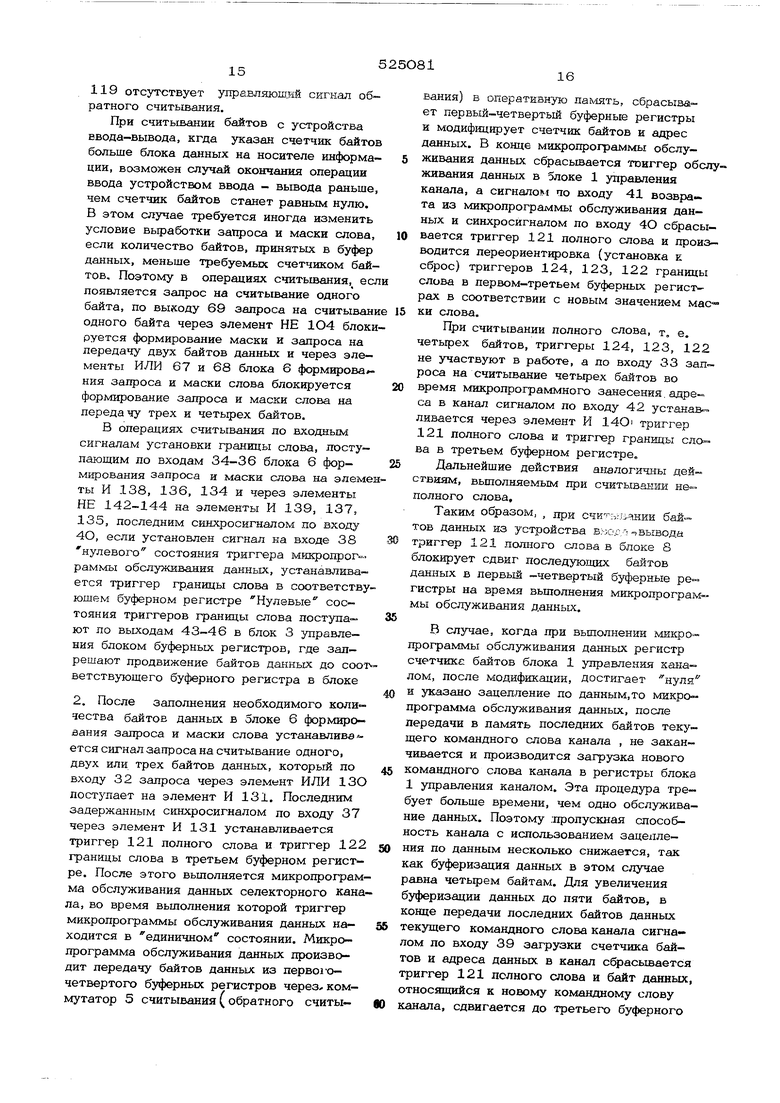

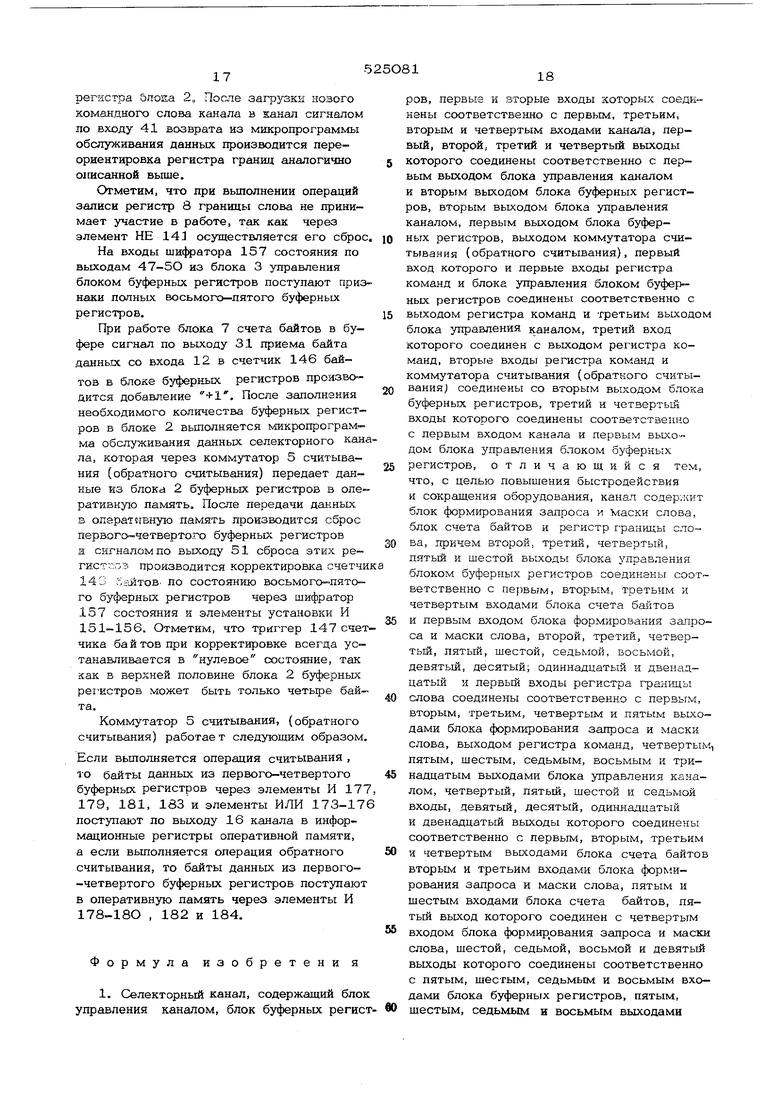

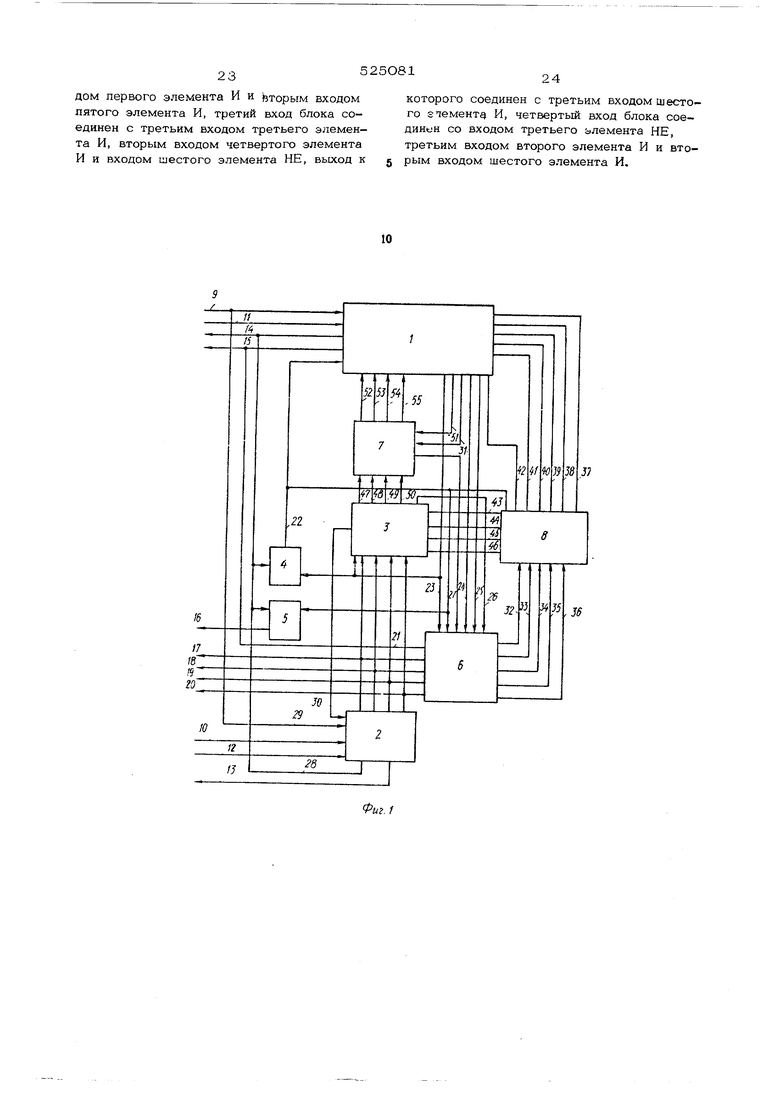

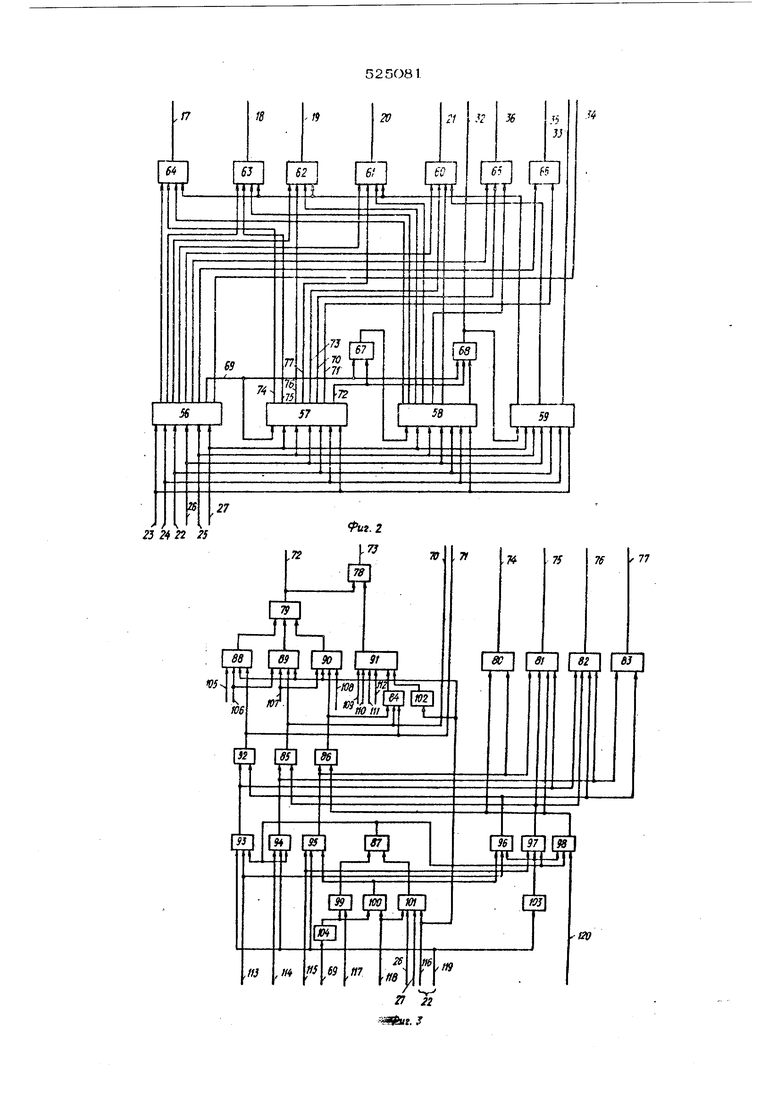

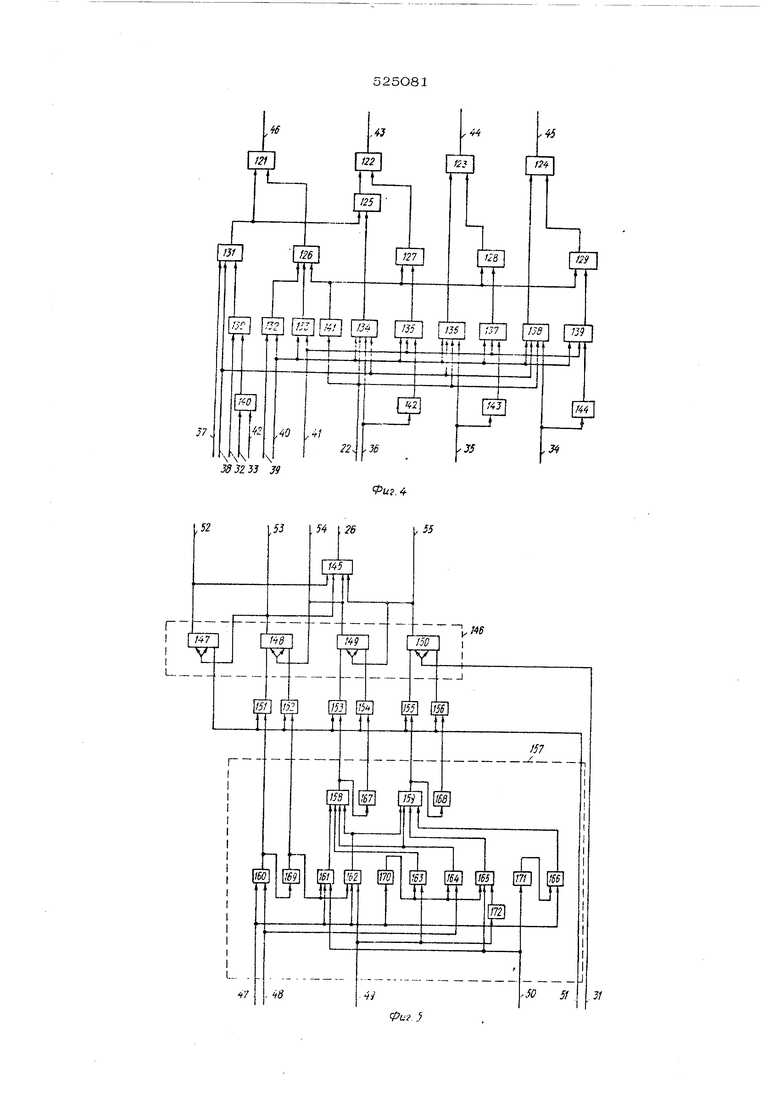

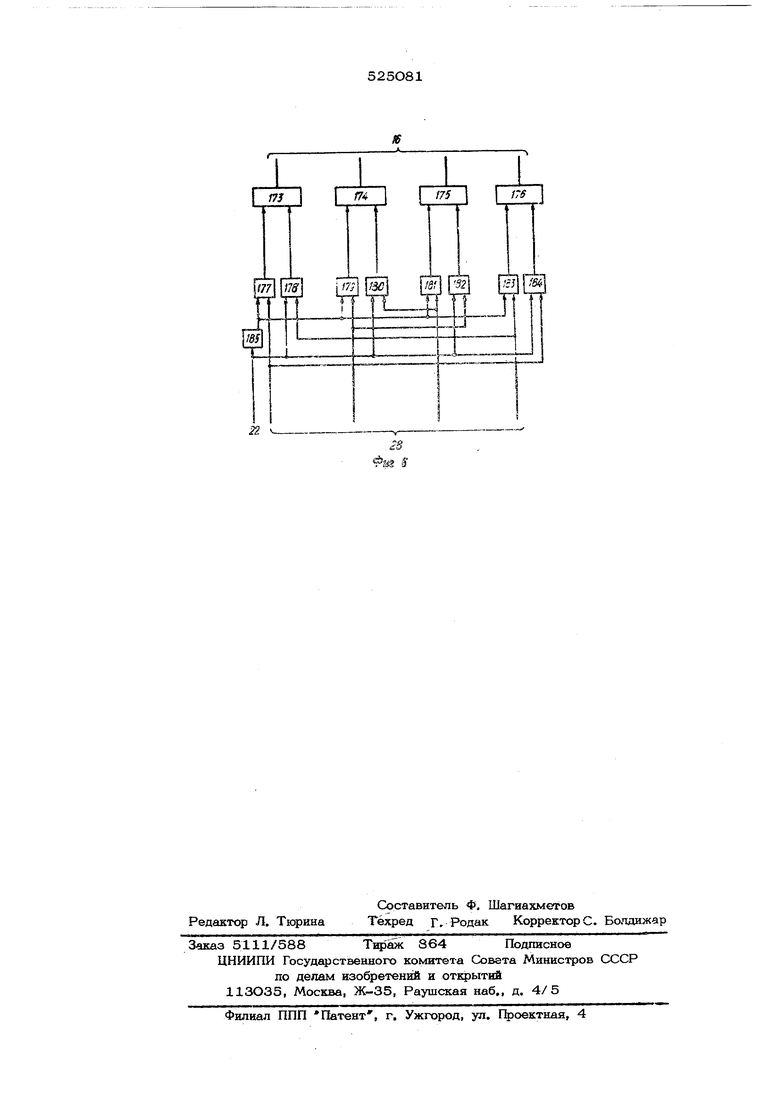

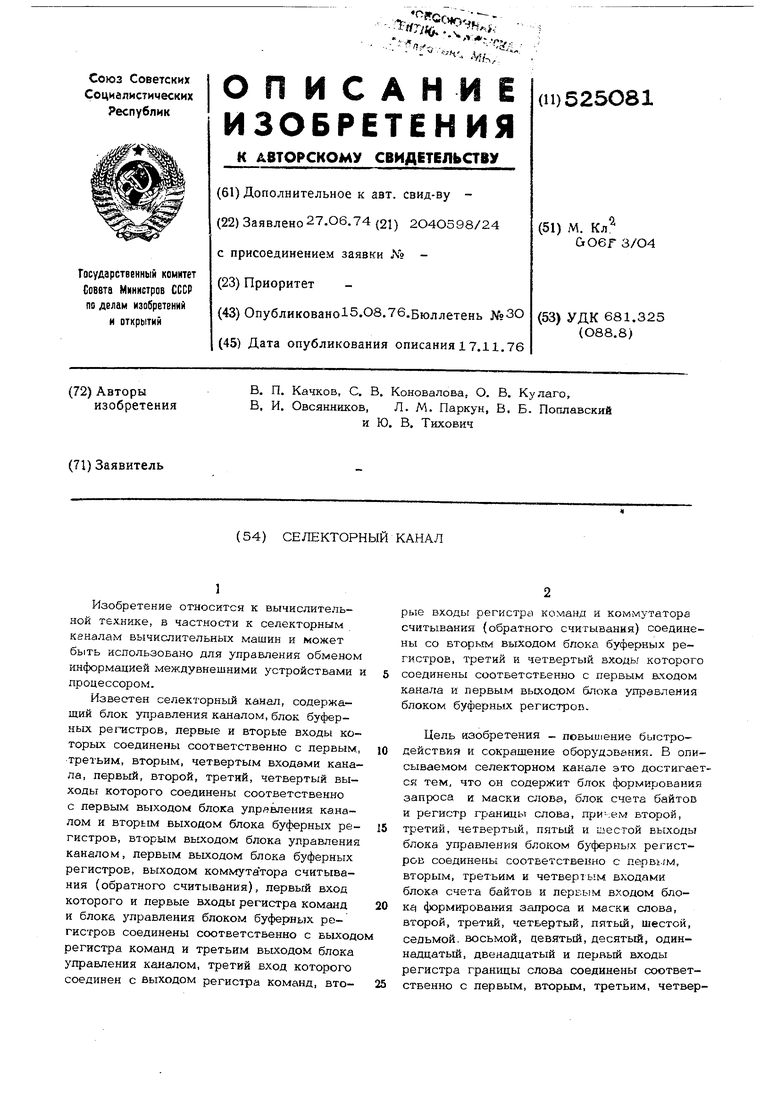

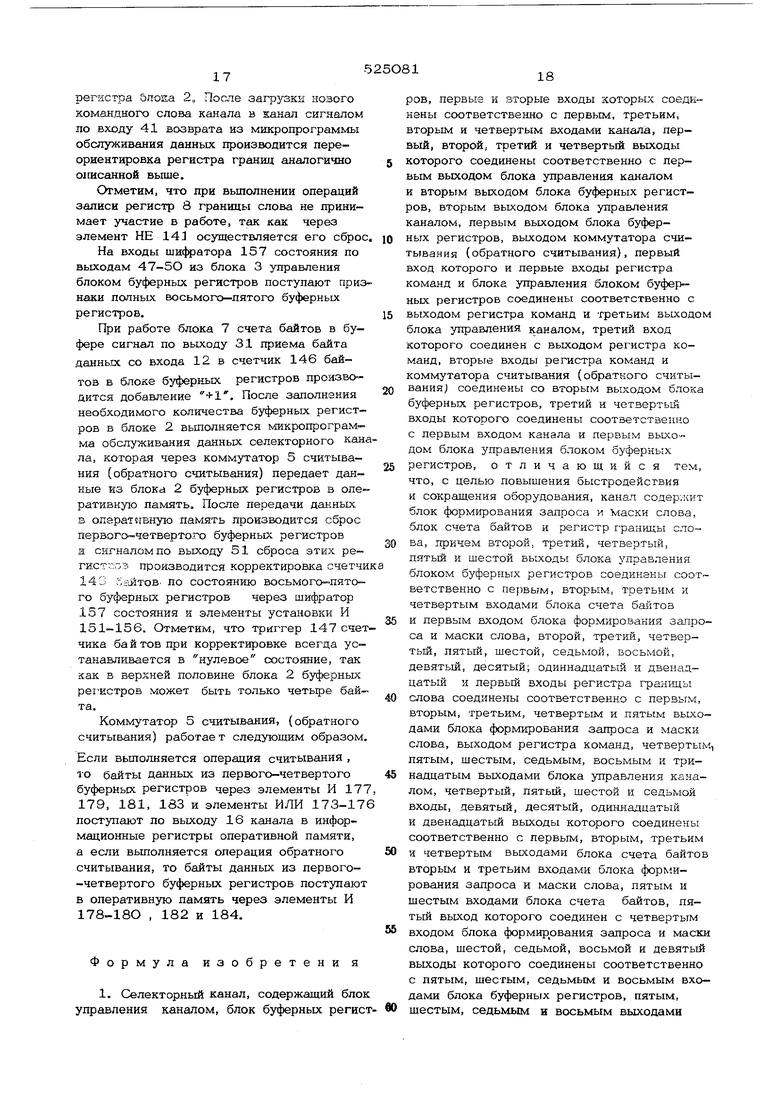

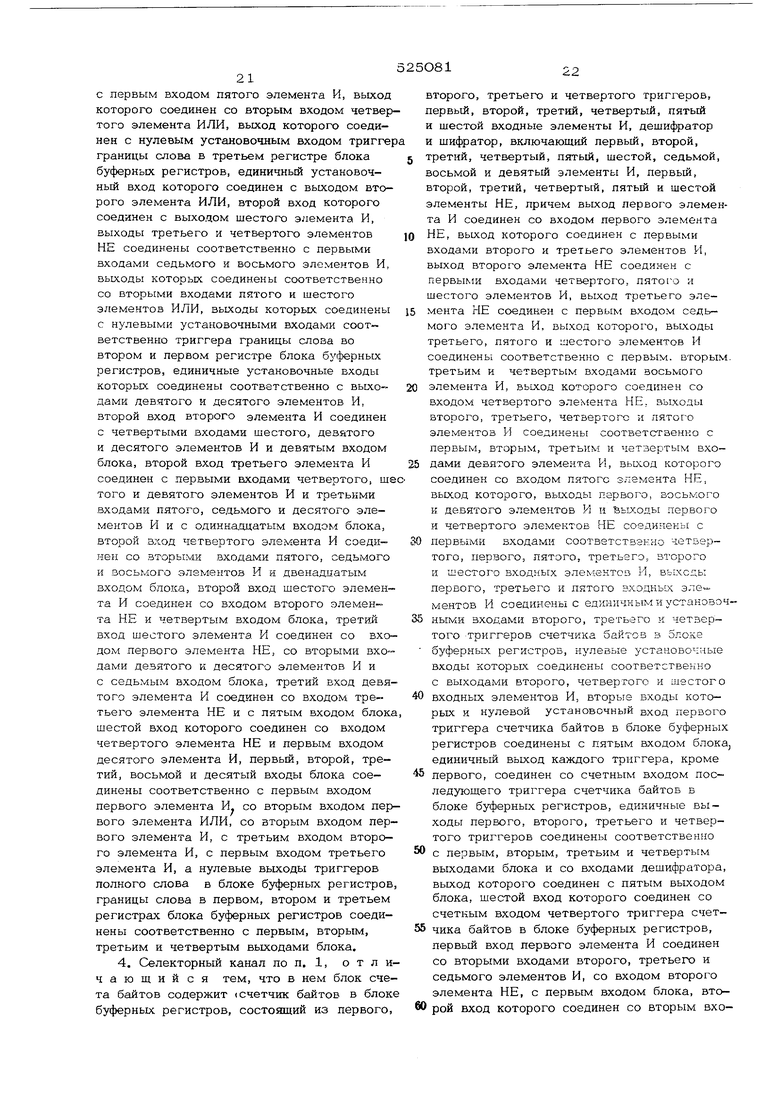

Цель изобретения повьшюние быстродействия и сокращение оборудования. В описываемом селекторном канапе это достигается тем, что он содержит блок формирования запроса и маски слова, блок счета байтов и регистр границы слова, при-:ем второй, третий, четвертый, пятый и шестой выходы блока управления блоком буферных регистров соединены соответственно с первим, вторым, третьим и четвертьм входами блока, счета байтов и первым входом блокц формирования запроса и маски слова, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый и первый входы регистра границы слова соединены соответственно с первым, вторым, третьим, четверTbiM и пягым выходами блока фсфмиьовани запроса н маски слова, выходом регистра команд, четвертым, пятым, шестым, седьмым, восьмым и финадцатым выходами блока управления каналом, , оятый, шестой, седьмой входы, девятый, десятый, одиннадцатый и двенадцатый выходы которого соединены соответственно с первым, вторым, третьим н четвертым выходами блока счета байтов, вторым и третьим входами блока форм1фования запроса и маски слова, пятым и шестым входами блока счета байтов, пятый выход кот рого соединен с четвертым входом блока фсфмирования запроса и маски слова, шестой, седьмой, восьмой & девятый выходы которого соединены соответственно с пятым, шестым, седьмым н восьмым входам блсжа буферных регистров, пятым, шестым седьмым и восьмым выходами канала, вто рым, третьим, четвертым н дятым входам блока управления блоком буферных регистров, шестой, седьмой, восьмой а девятый входы которого соединены соответственно с первым, вторым, третьим w. четвертым выходами регистра 1раницы слова, выход регистра команд и третий выход блока управления каналом ссединены -соотаетстзе но с пятым и шестым входами блока формирования запроса Н маскк слова, д-зсятьш выход которого соединен со вторым выходо канала. В описьшаемом селекторЕом канале блок формирования запроса и маски слова содержит узлы формирования запроса и маски слова на передачу одного байта, заП роса и маски слова на передачу двух байтов, запроса и маски слова на передачу трех байтов, запроса и маски слова на передачу четырех байтов, первьШ, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы ИЛИ, причем первые выходы узлов формирования запроса и маски слова на передачу одного двух и трех байтов соединены соответственно с первым, вторым и третьим ми первого элемента ИЛИ, вторые выходы узлов формирования запроса и маски слова на передачу одного, двух и трех байтов соединены соответственно с первым, вторым и третьим входами второго элемента ИЛИ, третьи выходы узлов формирования запроса и маски слова на передачу одного, двух и трех байтов соединеньх соответствен но с первым, вторым и третьим входами третьего элемента ИЛИ, четвертые выходы узлов формирования запроса и маски слова на передачу одного, двух и трех байтов соединены соответственно с первым, вторым и третьим входами четвертого элемента ИЛИ, первый вьиод узла фqpмирования запроса и слова на передачу четьфех байтов соединен с четвертыми входами первого, второго, третьего и четвертого элементов ИЛИ, пятые выходы узлов формирования запроса и маски слова на передачу одного, двух в орех байтов и второй выход узла формирования запроса и маски слова на передачу четьфех байтов соединены соответственно с первым, вторым, третьим и четвертым входами пятого элемента ИЛИ, шестые выходы узлов формирования запроса и маски слова на передачу одного, двух и трех байтов соединены соответственно с первым, вторым и третьим входами шестого элемента ИЛИ, седьмые выходы узлов (|юрмирования запроса и маски слова на передачу одного а двух байтов соединены соответственно с первым и .вторым входами седьмого элемента ИЛИ, восьмой выход узла формирования запроса и маски слова на передачу одного байта соединен с седьмым входом узла фор шрова, ния запроса к маски слова ка кэра-дачу двух байтов и первыми 3jr.o,rfat.ffi згоьмого и девйтого элементов ИЛИ., вторыа входы которьн соедине{ ы с зссьмьп-з зы-ходом узла формирования за:сфоса к г ьасжн слова на нередачу двух байтов, .Бь:и::од восьмого элемента ИЛИ соединен с сэдьмым входом узла формирования заггроса ж маски слова на передачу трек байтов, седьмой выход которого соедикен с третьим входом девятого элемента ИЛИ, выход жоторого соединен с седьмым входом узла формирования запроса и маски слова на па™ редачу четырех байтов, первый, второй, тре- тий, четвертый, пятый и шестой входы бло™ ка соединены соответственно с пятыми, пер™ выми, вторыми, четвертыми, третьими и естыми входами узлов формирования запроса и маски слова на передачу одного, двух, рех и четырех байтов, а первый, второй. входа-- 45 третий, четвертый, пятый ,шестой, седьмой. восьмой, девятый и десятый выходы блока соединены соответственно с выходом девятого элемента ИЛИ, третьим выходом узла формирования запроса и маски слова на передачу четьфех. байтов, девятым выходом узла формирования запроса и маски слова на передачу однрго байта, выходами седьмого, шестого, первого, второго, третьего, четвертого и пятого элементов ИЛИ. Он обличается также и тем, что в нем регистр грашщы слова содержит триггеры границы слова в первом, втором и третьем регистрах блока буферных регистров, триггер полного слова в блоке буферных регистров, первый. вторЫ, третий, четвертый, аятый, шестой. седьмой, .восьмой, девят хй, и десятый элементы И, первый, второй, третий, четве тый, пятый и шестой элементы ИЛИ, первы второй, третий и четвертый элементы НЕ, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом второго элемента И и единичным установочным входом триггера полного слова в блоке буферных регистров, нулевой установочный вход которого соединен с выходом третьего элемента ИЛ первый, второй и третий входы которого соединены соответственно с выходами третьего и четвертого элементов И и первого элемента НЕ, выход которого соединен с первыми входами четвертдго пятого и шестого элементов ИЛИ, выход второго элемента НЕ соединен с первым входом пятого элемента И, выход которого соединен со вторым входом четвертого элемента ИЛИ, выход которого соединен с нулевым установочным входом триггера границы слова в третьем регистре блока буферных регистров, единичный установочный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом шестог-о элемента И, выходы третьего и четвертого элементов НЕ соединены соответственно с первыми входами седьмого и восьмого элементов И, выходы которых соединены соответстве но со вторыми входами пятого и шестого элементов ИЛИ, выходы которых соединены с нулевыми установочными входами соответственно триггера границы слова во в ром и первом регистре блока буферных регистров, единичные установочные входы которых соединены соответственно с выход ми девятого и десятого элементов И, второй вход второго элемента И соединен с четвертыми входами шестого, девятого и десятого элементов И и девятым входом блока, второй вход третьего элемента И соединен с первыми входами четвертого, шестого и девятого элементов И и третьим входами пятого, седьмого и десятого элементов И и с одиннадцатым входом блока, второй вход четвертого элемента И соединен со вторыми входами пятого, седьмог и восьмого элементов И и двенадцатым вх дом блока, второй вход шестого элемента И соединен со входом второго элемента НЕ и четвертым входом блока, третий вхо шестого элемента И соединен со входом первого элемента НЕ, со вторыми входами девятого и десятого элементов И и с седь мым входом блока, третий вход девятого элемента И соединен со входим третьего элемента НЕ и с пятым вводом блока, шестой вход которого соединен со входом четвертого элемента НЕ и первым входом десятого элемента И, первый, втсфой, третий, восьмой и десятый входы блок.- соединены соответственно с первым входом первого элемента И, со вторым входом первого элемента ИЛИ, со вторым входом первого элемента И, с третьим входом второго элемента И, с первым входом третьего элемента И, а нулевые выходы триггеров полного слова в блоке буферных регистров, границы слова в первом, втором и третьем регистрах блока буферных регистров соединены соответственно с первым, вторым, третьим и четвертым выходами блока. Кроме того, в нем блок счета байтов содержит счетчик байтов в блоке буферных регистров, состоящий из первого, второго, третьего и четвертого триггеров, первый, второй, третий, четвертый, пятый и шестой входные элементы И, дешифратор и шифратор, включающий первый, второй, третий, четвертый, пятьЕЙ, шестой, седьмой, восьмой и девятый элементы И, первый, второй, третий, четвертый, пятый и шестой элементы НЕ, причем выход первого элемента И соединен со входом первого элемента НЕ, выход которого соединен с первыми входами второго и третьего элементов И, выход второго элемента НЕ соединен с первыми входами четвертого, пятого и шестого элементов И, выход третьего элемента НЕ соединен с первым входом седьмого элемента И, выход которого, выходы третьего, пятого и шестого элементов И соединены соответственно с первым, вторым, третьим и четвертым входами восьмого элемента И, выход которого соединен со входом четвертого элемента НЕ, выходы второго, третьего, четвертого и пятого элементов И соединены соответственно с первым, вторым, третьим и четвертым входами девятого элемента И, выход которого соединен со входом пятого элемента НЕ, выходы второго, третьего, четвертого и пятого элементов И соединены соответственно с первым, вторым, третьим и четвертым входами девятогхэ элемента И, выход которого соединен со входом пятого элемента НЕ, выход которого, выходы первого, восьмого и девятого элементов И и выходдл первого и четвертого элементов НЕ соединены с первыми входами соответственно четвертого, первого, пятого, третьего, второго и шестого входных элементов И, выходы первого, третьего и пятого входных элементов И соединены с единичными установочslbiMH вхолакш второго, третьего и четверТО1Х) тригге юв счетчика байтов в блоке буферных регистров, нулевые установочные входы KOTopbtx соединень соответственно с выходами второго, четвертого и шестого входных элементов И, вторые гвходы которых и нулевой установочный вход первого триггера счетчика байтов в блоке буферных регистров соединены с пятым входом блока, эдиничный выход каждого триггера кроме первого, соединен со счетным входо последующего триггера счетчика байтов в блоке буферных регистров, единичные выходы первого, второго, третьего и четвертого триггеров соединены соответственно с первым, вторым, третьим и четвертым выходами блока и со входами деши(} атора, выход которого соединен с пятым выходом блока, шестой вход которого соединен со счетным входом четвертого триггера счетчика байтов в блоке буферных регистров, первый вход первого элемента И соединен со вторыми входами второго,третьего и седьмого элементов И, со входом второго элемента НЕ, с первым входом блока, вход которого соединен со вторым входом первого элемента И и вторым входом пятого элемента И, третий вход блока соединен с трютьим входом третьего эле- мента И, вторым входом четвертого элемента И и входом шестого элекюнта НЕ, выход которого соединен с третьим входом шестого элемента И, четвертый вход блока соединен со входом трютьего элемента НЕ третьим входом второго элемента И и вторым входом шестого элемента И, На-фиг. 1 представлена блок-схема описываемого селекторного канала;на фиг. структура бпока -формирования запроса k и маски слова; на фиг. 3 - структура узла формирования запроса и маски слова на передачу двух байтов; на фиг, 4 - баок-сх ма регистра грвницы слова; на фиг. 5структура блока счета байтов; на фиг. 6 структура коммутатора считывания {обратного считывания). Селекторный канал содержит блок 1 уп4 равления каналов, блок 2 буферных регистр ров, блок 3 утфавления блоком буферных регистров, регистр 4 команд, коммутатор 5 считывания (обратного считьшания), блок 6 формирования запроса и маски слова, блок 7 счета байтов, 8 границы слова. Входы и выходы канала и его узлов обозначены: 9-12- входы, а 13-2О выходы канала; 21 - выход блока формирования запроса и маски слова; 22 - выход регистра„комаид; 3-27- входы блока фтлгк|тД i8 - ход, а 29 и ЗО - входы блока буферных регистров; 31 - выход блока управления каналом; 32-42 - входы регистра границы слова; 43-46 - выходы регистра границы слова; 47-5О - выходы блока управления блоком буферньгх регистров; 51 - выход блока управления каналом;;52-55 - входы блока управления каналом. Блок фс мирования запроса и маски слова содержит узел 56 формирования запроса и маски слова на передачу одного байта, узел 57 формирования запроса и маски слова на передачу двух /байтов,-; узел 58 формирования запроса и маски слова на передачу трех байтов, узел 59 формирования запроса и маски слова на передачу четьфех байтов, элементы ИЛИ 60-68. Узел формирования запроса и маски слова на передачу одного байта,имеет выход 69, а узел формирования запроса и маски слова на передачу двух байтов - выходы 7О-77. Узел формирования запроса и маски слова на передачу двух байтов содержит элементы ИЛИ . 78-87, элементыЙ 88-101 И элементы HS 1О2-1О4, Элементы И имеют входы 1О5 -112, а входы 1J.3-12O являются входами блока. Регистр границы слова содержит триггеры 121-124, элементы ИЛИ 125-13О, элементы И 131-14О, элементы НЕ 141-144. Блок счета байтов) cocтoи из дешифратора 145, счетч11ков байтов 146, содержащего триггеры 147-150, элементов И 151-156, шифратора 157 состояния буферных регистров, содержащего элементы И 158-166 и элементы УЕ J.67-172. Коммутатор считывания (обратного считывания) содержит элементы ИЛИ 173-176, элементы И 177-184, элементы НЕ 185. Селекторны .канал предназначен для подключения к процессору (на чертежах не показан) быстродействующих внешинх устройств, предполагается, что процессор ьмикропрограммной вычислительной машины содержит оперативную память, арифметичеоКС-Логическое устройство и блок мнкропрюграммого управления. Операция передачи данных в селекторном канале начинается по специальной команде процесссч а, которая задает адрес канала и устройства ввода - вывода и при помощи специальных управляющих слов I указывает код команды, начальный адрес оперативной памяти, количество Передава- ; емых байтов данных и другие управлякьщие признаки, которые располагаются в регистрах канала н в специальной упра&ляюшей.лишяти (ла чер тежах-йде--1шкааана) образуя в совокупности управляющее слово канала. Передача управляющей информации между процессором и регистрами кана ла производится через вход 9 и выход 14 передача управляющей информации и данных между устройством ввода - вывода и каналом проиводится через блок 2 буферных регистров,вход 12 и выход 13. Получив необходимую управляющую информацию, кан производит начальную выборку устройства ввода - вывода и освобождает процессор для выполнения аругих команд. В зависимости от кода операции, установленного в в регистре 4 команд, от значения счетчика байтов и младших разрядов адреса дан ных, признаков состояния регистров блока 3 управления блоком буферных регистров, состояния блока 7 счета байтов, поступающих по вхоцам 23-27 в блок 6 формирования запроса и маски слова, в последнем вырабатывается запрос на микропрограммную приостановку, поступающий по выходу 21 блока 6 и выходу 15 канала в блок микропрограммного управления процессора, и вырабатываются управляющие сигнал на выходах 17-2О маски приема слова да ных в оперативную память или блок 2 буферных регистров. По запросу на микропрограммную приостановку, если память свободна, выполнение текущей микропрограммы процессора прерывается и вьшолняется микропрограмма обслуживания данных канала, под управлением которой производи ся передача данных между блоком 2 буфер .ных регистров и оперативной памятью процессора по входу 1О и выходу 16 канала, модификация адреса данных и счетчика байтов. Так как слово оперативной памяти процессора, к которому подключен рассматриваемый канал, состоит из четырех байтов, то передача данных между оперативной памятью и буфером данных канала производится в основном полными словами памяти, но в начале и конце передачи данных возможна передача неполными словами памяти. Если начальный адрес данных не соответствует границе слова памяти, то при первой передаче дан ных между блоком 2 буферных регистров и оперативной памятью производится выравнивание адреса данных до границы слов Поэтому в начале передачи данных возмож на передача одного, двух или трех байтов. Если начальный или конечный адрес данных соответствует границе слова, но указан счетчик байтов меньше четырех, то осуществляется передача количества байтов, оответствующего значению счетчика байов. Блок 2 буферных регистров канала состоит из восьми однобайтных регистров (на чертежах не показаны). При передаче управляющей информации он загружается по входу 29 через восьмой буферный регистр и разгружается через первый буферный регистр по выходу 28, причем байт информации может быть продвинут от восьмого буферного регистра до первого (если перед этим блок буферных регистров был пустой) за один машинный такт. Гфи передаче данных в операциях считывания блок 2 загружается через восьмой буферный регистр и разгружается через первый - четвертый буферные регистры, коммутатор 5 считывания (обратного считывания) в оперативную память, а в операциях записи-загружается через восьмой - пятый буферные регистры и разгружается через первый буферный регистр в устройство ввода - вывода. Прием и сдвиг информации в блоке 2 осущестЕУЛяется по входу ЗО под управление блока 3 управления блоком буферных регистров, в котором после каждого такта сдвига положение байтов данных в блоке 2 анализируется и устанавливаются соответствующие признаки полных и пустых буферных регистров. Отме- ТИМ, что сдвиг в блоке 2 за один машинный такт производится всегда до ближайшего полного буферного регистра. Байт данных, соответствующий границе слова оперативной памяти, при выполнении операций записи принимается всегда в пятый буферный регистр, а при выполнении операции считывания выдается кз первого буферного регистра и при операции обратного считывания - из четвертого буферного регистра в оперативную память. При выполнении операции записи в канале запрос на микропрограммное прерывание для выполнения микропрограммы обслуживания данных вырабатывается в блоке 6 формирования запроса и маски слова в тот момент, когда освобождаются восьмой, шестой, пятый и хотя бы один из первого четвертого буферных регистров, так как к моменту передачи байтов данных в блок 2 из оперативной памяти четвертый буферный регистр освобождается, т. е. становится пустым. Микропрограмма обслуживания данных производит необходимую корректировку управляющего слова канала и по маске слова, вьфаботанной в блоке 6 формирования запроса и маски слова и поступаюющей по выходам 17-2О маски слова, производит передачу необходимых байтов данных в блок 2 буферных регистров. Если передается полное слово, то маска слова равна 1111, а если передается неполно слово, например два байта, то в зависимо ти от адреса данных вырабатывается маск слова НОО, ОНО или ООН и ба ты данных принимаются соответственно в пятый и шестой, шестой и седьмой, седьм и восьмой буферные регистр ы. Таким образом, каждому байту слова памяти соответствует свое место в блоке 2 буферных регистров. После приема из оперативной памяти в блок 2, байты данных сдвигаются до первого буферного регистра, откуда они выда ются в устройство ввода - вывода. Операция записи в канале обычно заканчивается тогда, когда счетчик байтов достигает нуля, после передачи всех байтов из блока 2 буферных регистров в устройство ввода - вывода. При вьшолнении операции считывания байты данных со входа 12 принимаются в восьмой буферный регистр блока 2 и продвигаются к первому четвертому буферным регистрам, причем при каждом приеме байта данных по входу 12 содержимое счетчика байтов в блоке 7 счета байтов по сигналу на выходе 31 приема со входа 12 увеличивается на единицу. В зависимости от значения двух младших разрядов адреса аанных к значения счетчика байтов в блоке 6 формирования запроса и маски слова вырабатываются сяециальные управляющие сигналы, поступающие по входам 34-36 установки в регистр 8 границь слова, По этим сигналам на входах 37-42 регистра 8 границы сло устанавливается один из триггеров границы слова в соответствующем регистре блэка нулевые выходы которых по выходам 43-4 поступают в блок 3 управления блоком буферных регистров, где запрещают продвижение первого считанного или продвигаемого байта в соответствующий регистр бл ка 2. Как только необходимое количество байтов достигает своего места в блоке 2 буферны-х регистров, т. е. заполняются необходимые регистры до регистра, соответ ствующего границе слова, и в блоке 3 управления блоком буферных регистров вырабатываются необходимые сигналы полных первого-четвертого буферных регистров, в блоке б формирования запроса и маски слова выраоатывается запрос на микропрограммное прерывание для вьшолнения микро программы обслуживания данных. Одновременно в регистре 8 границы слова установится триггер полного слова в блоке 2, запрещающий продвижение байтов данных в первый - четвертый буферные регистры. Микропрограмма обслуживания данных производит необходимую корректировку управляющего слова канала и по маске слова, выработанной в блоке 6 формирования запроса и маски слова,и поступающей в оперативную память по выходам 17-2О, производит передачу данных из блока 2 буферных регистров в регистр данных оперативной памяти через коммутатор 5 считывания (обратного считывания) и вьLxoды 16 канала. По маске слова в такте чтения из оперативной памяти производится прием в регистр данных оперативной памяти байтов из блока 2 буферных регистров, если в соответствующем разряде маски указана 1, или с кодовых щин числа, если в соответствующем разряде мас ки указан О. В конце микропрограммы обслуживания данных производится сброс первого-четвертого буферных регистров, корректировка содержимого счетчика байтов блоке 7 счета байтов, сбрасывается триггер полного слова в блоке 2 и осуществляется переориентировка регистра 8 границь слова. Операция считывания в канале заканчивается, когда счетчик байтов становится равным содержимому счетчика байтов в блоке 7 счета байтов В этом случае блок 1 управления каналом заканчивает обмен данными с устройством ввода - вывода. Входы каждого из четырех узлов 56-59 блока 6 формирования запроса и маски слова подключены к входу 23 состояния счетчика байтов, входу 24 состояния двух младщих разрядов адреса данньк, выходу 22 состояния регистра команд, входу 27 блока счета байтов, входу 26 состояния регистров в блоке 2 буферных регистров, а также к входу 25 блока 1 -правления каналом. Выборка одного из узлов формирования запроса и маски слова происходит в зависимости от следующих условий: если адрес данных соответствует границе слова, то выполняется передача полного слова памяти (четырех байтов) при счетчике байтов -4 или неполного слова при счетчике байтов 4 (передача одного, двух и трех байтов, если счетчик байтов равен соответственно одному, двум и трем); если адрес данных не соответствует границе слова, то выполняется передача такого количества байтов (неполного слова), чтобы после этой передачи адрес данньк соответствовал границе слова, причем, если до границы слова осталось передать три, два или один байт и счетчик соответственно равен или больще трех, двух или единицы, то выполняется передача соответственно трех. двух или одного байта до границы слова, а если величина счетчика байтов недостаточ на для достижения границы слова, то выпол няется передача количества байтов, указанного счетчиком байтов. Выходы 69-77 узлов формирования запр са и маски слова соединены со входами эле ментов ИЛИ 6О-68 и выходами блока. Рассмотрим работу блока 6 формировани запроса и маски слова на примере работы узла 57 формирования запроса и маски слова на передачу двух байтов. Код Ю, 11, Ol, 00 состояния двух младших разрядов адреса данных пос113-11тупает соответственно по входам состояния младшего адреса данных блока 1 на входы элементов И 93-98 формирования маски слова, а код состояния содержимого счетчика байтов, соответствующий значению 2 и 2, поступает по входам 117-118 состояния счетчика байтов блока 1 соответственно на элементы И 99-1О1Управляювдий сигнал признака команды считывания ло входу 116 регистра команд поступает на входы элементов И 1О1, И 88-9О формирования запроса в операциях считывания, а также через элемент НЕ 1О на элемент И 91 формирования запроса в операциях записи. Управляющий сигнал признака обратного считывания по соответствующему входу 119 регистра команд поступает на входы элементов И 93-9 5 и через элемент НЕ ЮЗ на входы элементов И 96-98, Отметим, что управляющие признаки команд считывания и обратного считьшания при вьшолнении операций записи отсутствуют, при этом элементы И 93-95, И 1О1 и И 88-9О не работают. Рассмотрим выполнение операции считывания при коде адреса, равном Ю, и сче чике байтов г- 2, когда установлены управляющие сигналы на входах 118 и 113 и должно произойти выравнивание адреса до границы слова ОО. В этом случае на выходе элемента формирования маски слова И 96 появляется управляющий сигнал, по которому вырабатываются сигналы маск слова на выходе элементов ИЛИ 82, 83, которые по выходам маски 76 и 77, через элементы ИЛИ 62, 61 блока 6 формир вания запроса и маски слова поступают в оперативную память, блоки 2 и 3. Таким образом, вырабатывается маска слова, соответствующая коду ООН. С выхода элемента И 96 управляющий сигнал через элемент И 92 поступает также на вход элемента И 88 формирования запроса а также через выход 71 и элемент ИЛИ 6 блока 6 формирования запроса и маски ело ва на вход 35 установки границы слова во втором буферном регистре блока 2, по которому в регистре 8 границы слова устанавливается триггер границы слова во втором буферном регистре блока 2, запрещающий сдвиг считываемых байтов во второй и первый буферные регистры блока 2. Байты данных сдвигаются в блоке 2 и, как только заполняются третий и четвертый буферные регистры блока 2, в блоке 3 управления блоком буферных регистров вырабатываются сигналы полных третьего и четвертого буерных регистров блока 2, которые по входам 1О5 и 1О6 поступают на вход элемента И 88 формирования запроса. При этом на выходе элемента ИЛИ 79 вырабатывается сигнал запроса на считывание двух байтов, а на выходе элемента ИЛИ 78 - общий сигнал запроса, который через выход 73 узла 57 формирования запроса и маски на передачу двух байтов и элемент ИЛИ 6О поступает на выход запроса 21 блока 6формирования запроса и маски слова. По этому сигналу запроса блок микропрограммного управления процессора выполняет микропрограмму обслуживания селекторного канала, которая по маске слова ООН передает в оперативную память два байта данных. После передачи байтов данных, содержимое адреса данных и счетчика байтов модифицируется на два и изменяются соответственно условия формирования запроса и маски слова. Если указан счетчик байтов, равный двум, то через элемент И 99 и элемент ИЛИ 87 возбуждается соответствующий элемент И 93, 94, 97, 98 формирования маски слова. Если устройство ввода - вывода заканчитывает операцию передачи данных, то на входе 25 блока 1 управления каналом появляется специальный управляющий сигнал, который поступает на элемент И 1О1 и, если в это время счетчик байтов .блока 7равен двум, т. е. возбужден соответствующий выход состояния блока 7 счета байтов, срабатывает элемент И 1О1, сигнал с которого через элемент ИЛИ 87 поступает на соответствующие элементы И формирования маски слова. Если выполняется операция записи, то сигналы маски слова вырабатываются аналогично, а сигнал запроса вьфабатывается с помощью элемента ИЛИ 84 и элемента И 91, на входы которого по входам 1О9-112 поступают сигналы признаков пустых буферных регистров блока 2. В операции записи элементы И 93-95 в формировании маски слова не участвуют, так как на входе 119 отсутствует управляющий сигнал обратного считывания. При считывании байтов с устройства ввода-вывода, кгда указан счетчик байто больше блока данных на носителе информа ции, возможен случай окончания операции ввода устройством ввода - вывода раньше чем счетчик байтов станет равным нулю. В этом случае требуется иногда изменить условие вьфаботки запроса и маски слова, если количество байтов, принятых в буфер данных, меньше требуемых счетчиком бай тов. Поэтому в операциях считьшания, ес появляется запрос на считывание одного байта, по вьмсоду 69 запроса на считыван одного байта через элемент НЕ 1О4 блок руется формирование маски и запроса на передачу двух байтов данных и через элементы ИЛИ 67 и 68 блока 6 формирова ния запроса и маски слова блокируется формирование запроса и маски слова на переда чу трех и четьфех байтов. В операциях считывания по входным сигналам установки границы слова, поступающим ло входам 34-36 блока 6 формирования запроса и маски слова на элеме ты И 138, 136, 134 и через элементы НЕ 142-144 на элементы И 139, 137, 135, последним синхросигналом по входу 4О, если установлен сигнал на входе 38 нулевого состояния триггера мшфолрог- раммы обслуживания данных, устанавливается триггер гр.аницы слова в соответству ющем буферном регистре Нулевые состояния триггеров граншхы слова доступают ло выходам 43-46 в блок 3 управления блоком буферных регистров, где зал- решают продвижение байтов данных до соот ветствующего буферного регистра в блоке 2. После заполнения необходимого количества байтов данных в блоке 6 формирования запроса и маски слова устанавлнва ется сигнал запроса на считывание одного, двух или трех байтов данных, который по входу 32 запроса через элемент ИЛИ 13О поступает на элемент И 131. Последним задержанным синхросигналом по входу 37 через элемент И 131 устанавливается триггер 121 полного слова и триггер 122 границы слова в третьем буферном регистре. После этого вьшолняется микропрограм ма обслуживания данных селекторного кана ла, во время вьшолнения которой триггер микропрограммы обслуживания данных на- ходится в единичном состоянии. Микропрограмма обслуживания данных производит передачу байтов данных из nepBOiOчетвертого буферных регистров через коммутатор 5 считывания ( обратного считывания) в оперативную память, сбрасывает первый-четвертый буферные регистры и модифицирует счетчик байтов н адрес данных. В конце микропрограммы обслуживания данных сбрасьшается тоиггер обслуживания данных в блоке 1 управления канала, а сигналом по входу 41 возврата из микропрограммы обслуживания данных и синхросигналом по входу 4О сбрасывается триггер 121 полного слова и производится переориентировка (установка к сброс) триггеров 124, 123, 122 границы слова в первом-третьем буферных регистрах в соответствии с новым значением мае- ки слова. При считывании полного слова, т, е. четырех байтов, триггеры 124, 123, 122 не участвуют в работе, а по входу 33 зап роса на считывание четьфех байтов во время микропрограммного занесения адреса в канал сигналом ло входу 42 устанавливается через элемент И 14Oi триггер 121 полного слова и триггер границы слова в третьем буферном регистре. Дальнейшие действия аналогичны действиям, вьшолняемым при счйтыв.знии не. полного слова. Таким образом, , при сч:и -ьгц.чнии байтов данных из устройства вмодо- вывода триггер 121 полного слова в блоке 8 блокирует сдвиг последующих байтов данных в первый -четвертый буферные ре- гистры на время вьшолнения микропрограммы обслуживания данных. В случае, когда при вьшолнении микропрограммы обслуживания данных регистр счетчике байтов блока 1 управления каналом, после модификации, достигает нуля и указано зацепление по данным, то микропрограмма обслуживания данных, после передачи в память последних байтов текущего командного слова канала , не заканчивается и производится загрузка нового командного слова канала в регистры блока 1 управления каналом. Эта процедура требует больше времени, чем одно обслуживание данных. Поэтому .-пропускная способность канала с использованием зацепления по данным несколько снижается, так как буферизация данных в этом случае равна четьфем байтам. Для увеличения буферизации данных до пяти байтов, в конце передачи последних байтов данных текущего командного слова канала сигналом ло входу 39 загрузки счетчика байтов и адреса данных в канал сбрасывается триггер 121 лслного слова и байт данных, тносящийся к новому командному слову анала, сдвигается до третьего буферного регистра блока 2, После загрузки нового командного слова канала в канал сигналом по входу 41 возврата из микропрограммы обслуживания данных производится переориентировка регистра гранш аналогично описанной вьпие. Отметим, что при вьшолнении операций записи регистр 8 границы слова не принимает участие в работе, так как через элемент НЕ 143 осуществляется его сбро На входы ши(} атора 157 состояния по выходам 47-5О из блока 3 управления блоком буферных регистров поступают приз наки полных восьмого-пятого буферных регистров. При работе блока 7 счета байтов в буфере сигнал по выходу 31 приема байта данньпс со входа 12 в счетчик 146 байтов в блоке буферных регистров производится добавление , После заполнения необходимого количества буферных регистров в блоке 2 вьшолняется микропрограмма обслуживания данных селекторного кан ла, которая через коммутатор 5 считывания (обратного считывания) передает данные из блока 2 буферных регистров в опе ративную память. После передачи данных в оперативную память производится сброс первого-четвертого буферных регистров а сигналом по выходу 51 сброса этих ре- производится корректировка счетч 143 байтов, по состоянию восьмого-пятого буферных регистров через шифратор 157 состояния и элементы установки И 151-156. Отметим, что триггер 147 сче чика байтов при корректировке всегда устанавливается в нулевое схэстояние, так как в верхней половине блока 2 буферных регистров может быть только четьфе байта. Коммутатор 5 считывания, (обратного считывания) работае т следующим образом Если вьшолняется операция считывания , то байты данных из первого-четвертого буферных регистров через элементы И 17 179, 181, 183 и элементы ИЛИ 173-17 постзшают по выходу 16 канала в информационные регистры оперативной памяти, а если вьшолняется операция обратного считывания, то байты данных из первого-четвертого буферных регистров поступают в оперативную память через элементы И 178-18О , 182 и 184. Формула иаобретени я 1. Селекторный канал, содержаший бло управления каналом, блок буферных регис ров, первые и вторые входы которых соединены соответственно с первым, третьим, вторым и четвертым входами канала, первый, второй; третий и четвертый выходы которого соединены соответственно с первым выходом блока управления каналом и вторым выходом блока буферных регистров, вторым выходом блока управления каналом, первым выходом блока буферных регистров, выходом коммутатора считывания (обратного считывания), первый вход которого и первые входы регистра команд и блока управления блоком буферных регистров соединены соответственно с выходом регистра команд и третьим выходом блока управления каналом, третий вход которого соединен с выходом регистра команд, вторые входы регистра команд и коммутатора считывания (обратного считывания соединены со вторым выходом блока буферных регистров, третий и четвертый входы которого соединены соответственно с первым входом канала и первым выходом блока управления блоком буфернь;х регистров, отличающийся тем, что, с целью повышения быстродействия и сокращения оборудования, канал содержит блок формирования запроса и маски слова, блок счета байтов и регистр границы слова, причем второй, третий, четвертый, пятый и шестой выходы блока управления блоком буферных регистров соединены соответственно с первым, вторым, третьим и четвертым входами блока счета байтов и первым входом блока формирования запроса и маски слова, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый; одиннадцатый и двенадцатый и первый входы регистра границы слова соединены соответственно с первым, вторым, третьим, четвертым и пятым выходами блока формирования запроса и маски слова, выходом регистра команд, четвертым, пятым, шестым, седьмым, восьмым и тринадцатым выходами блока управления каналом, четвертый, пятый, шестой и седьмой входы, девятый, десятый, одиннадцатый и двенадцатый выходы которого соединены соответственно с первым, вторым, третьим и четвертым выходами блока счета байтов вторым и третьим входами блока формирования запроса и маски слова, пятым и щестым входами блока счета байтов, пятый выход которого соединен с четвертым входом блока формирования запроса и маски слова, шестой, седьмой, восьмой и девятый выходы которого соединены соответственно с пятым, щестым, седьмым и восьмым входами блока буферных регистров, пятым. шестым, седьмым и восьмым выходами

канала, вторьгм, третьим, четвертым и пятым входами блока управления блоком буферных регистров, шестой, седьмой, восьмой и девятый входы которого соединены соответственно с первым, вторым, третьим и четвертым выходами регистра границы слова, выход регистра команд и третий выход б.юка управления каналом соединены соответственно с пятым и шестым входами блока формирования запроса и маски слова, десят выход которого соединен со вторым выходом канала. 2. Селекторный канал по п. 1, отл чающийся тем, что в нем блок формирования запроса и маски слова содер .ivUT узлы формирования запроса и маски слова на передачу одного байта, запроса и маски слова на передачу двух байтов, зап роса и маски слова на передачу трех байт запроса и маски слова на передачу четыре За и тоБ , первый, второй, третий, четвертый пятый, шестой, седьмой, восьмой и девяты элементы ИЛИ, причем первые выходы узл формирования запроса и маски слова на пе редачу одного, двух и трех байтов соедине ны соответственно с первым , вторым и третьим входами первого элемента ИЛИ, вторь е выходы узлов формирования запроса и маски слова на передачу одного, двух и трех байтов соединены соответственно с первым, BTopbiM и третьим входами второго элемента ИЛИ, третьи выходы узлов формирования запроса и маски слова на передачу одного ,двух и трех байтов соединены соответственно с первым, вторым и третьим входами третьего элемента ИЛИ, четвертые выходы узлов формирования за росе и маски слова на передачу одного, дв и трех байтов соединены соответственно с первым, вторым и третьим входами четвер элемента ИЛИ, первый выход узла формирования запроса и маски слова на передачу четырех байтов соединен с чет- верными входами первого, второго, третьего к четвертого элементов ИЛИ, пятые вы ходы узлов формирования запроса и маски слова на передачу одного, двух и трех оай-ов и второй вьгход узла формирования запроса и маски слова на передачу четырех байтов соединены соответственно с пер вьг.1, вторым, третьим и четвертым входами ЛИТОГО элемента ИЛИ, шестые выходы узлоа формирования запроса и маски слова на лередачу одного, двух и трех байтов соединены соответственно с первым, вторых и третьим входами шестого элемента ИЛИ седьмые выходы узлов формирования залро а и маски слова на передачу одного f байтов соединены соответственно ..т и вторым входами седьмого элемента ИЛИ, восьмой выход узла формирования запроса и маски слова на передачу одного байта соединен с седьмым входом узла формирования запроса и маски слова на передачу двух байтов и первыми входами восьмого и девятого элементов ИЛИ, вторые входы которых соединены с восьмым выходом узла формирования запроса и маски слова на передачу двух байтов, выход восьмого элемента ИЛИ соединен с седьмым входом узла формирования запроса и маски слова на передачу трех байтов, седьмой выход которого соединен с третьим входом девятого элемента ИЛИ, выход которого соединен с седьмым входом узла формирования запроса и маски слова на передачу четырех байтов, первый, второй, третий, четвертый, пятый и шестой входы блока соединены соответственно с пятыми, первыми, вторыми, четвертыми, третьими и шестыми входами узлов формирования запроса и маски спова на передачу одного, двух, трех и четырех байтов, а первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый выходы блока соединены соответственно с выходом девятого элемента ИЛИ, третьим выходом узла формирования запроса и маски слова на передачу четырех байтов, девятым выходом узла формирования запроса и маски слова на передачу одного байта, выходами седьмого, шестого, первого, второго, третьего, четвертого и пятого элементов ИЛИ, 3, Селекторный канал по л. 1, о т л ичаюш;ий ся тем, что в нем регистр границы слова содержит триггеры границы слова в первом, втором и третьем регистрах блока буферных регистров, триггер полного слова в блоке буферных регистров, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый элементы И, первый, второй,третий, четвертый, пятый и шестой элементы ИЛИ, первый, второй, третий и четвертый элементы НЕ, причем выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом второго элемента ИЛИ и единичным установочным входом триггера полного слова в блоке буферных регистров, нулевой установочный вход которого соединен с выходом третьего элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с выходами третьего и четвертого элементов И и первого элемента НЕ, выход которого соединен с первыми входами четвертого, пятого и шестого элементов ИЛИ, выход второго элемента НЕ соединен с первым входом пятого элемента И, выход которого соединен со вторым входом четвер того элемента ИЛИ, выход которого соединен с нулевым установочным входом тригге границы слова в третьем регистре блока буферньк регистров, единичньй установочный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом шестого элемента И, выходы третьего и четвертого элементов НЕ соединены соответственно с первыми входами седьмого и восьмого элементов И, выходы которых соединены соответственно со вторыми входами пятого и шестого элементов ИЛИ, выходы которых соединены с нулевыми установочными входами соответственно триггера границы слова во втором и первом регистре блока буферных регистров, единичные установочные входы которых соединены соответственно с выходами девятого и десятого элементов И, второй вход второго элемента И соединен с четвертыми входами шестого, девятого и десятого элементов И и девятым входом блока, второй вход третьего элемента И соединен с первыми входами четвертого, ш того и девятого элементов И и третьими входами пятого, седьмого и десятого элементов И и с одиннадцатым входом блока, второй вход четвертого элемента И соединен со вторыми входами пятого, седьмого и восьмого элементов И и двенадцатым входом блока, второй вход шестого элемента И соединен со входом второго элемента НЕ и четвертым входом блока, третий вход шестого элемента И соединен со вхо дом первого элемента НЕ, со вторыми входами девятого и десятого элементов И и с седьмым входом блока, третий вход девя того элемента И соединен со входом третьего элемента НЕ и с пятым входом блок шестой вход которого соединен со входом четвертого элемента НЕ и первым входом десятого элемента И, первый, второй, третий, восьмой и десятый входы блока соединены соответственно с первым входом первого элемента И. со вторым входом пер вого элемента ИЛИ, со вторым входом пер вого элемента И, с третьим входом второго элемента И, с первым входом третьего элемента И, а нулевые выходы триггеров полного слова в блоке буферных регистров границы слова в первом, втором и третьем регистрах блока буферных регистров соединены соответственно с первым, вторым, третьим и четвертым выходами блока. 4. Селекторный канал по п. 1, отли чающийся тем, что в нем блок сче та байтов содержит счетчик байтов в блок буферных регистров, состоящий из первого торого, третьего и четвертого триггеров, ервый, второй, третий, четвертый, пятый шестой входные элементы И, дешифратор шифратор, включающий первый, второй, ретий, четвертый, пятый, шестой, седьмой, осьмой и девятый элементы И, первый, торой, третий, четвертый, пятый и шестой лементы НЕ, причем выход первого элемента И соединен со входом первого элемента НЕ, выход которого соединен с первыми входами второго и третьего элементов И, выход второго элемента НЕ соединен с первыми входами четвертого, пятого и шестого элементов И, выход третьего элемента НЕ соединен с первь м входом седьмого элемента И, выход которого, выходы третьего, пятого и шестого элементов И соединены соответственно с первым, вторым, третьим и четвертым входами восьмого элемента И, выход которого соединен со входом четвертого элемента НЕ. выходы второго, третьего, четвертого и пятого элементов И соединены соответственко с первым, вторым, третьим и четвертым входами девятого элемента И, вьосод которого соединен со входом пятого элемента НЕ, выход которого, вькоды первого, восьмого и девятого элементов И и febLKoab первого и четвертого элемектов НЕ соедимены с первыми входами соответствэкно четвертого, первого, пятого, третьего, второго и шестого входных элементов И, выхсдь: первого, третьего и пятого входных эле ментов И соединены с единичным и установочными входами второго, третьего и четвертого -триггеров счетчика байтов з блоке буферных регистров, нулевые установочные входы которых соединены соответсгвекко с выходами второго, четвертого и шестого входных элементов И, вторые входы которых и нулевой установочный вход первого триггера счетчика байтов в блоке буферных регистров соединены с пятым входом блока, единичный выход каждого триггера, кроме первого, соединен со счетным входом последующего триггера счетчика байтов в блоке буферных регистров, единичные выходы первого, второго, третьего и четвертого триггеров соединены соответственно с первым, вторым, третьим и четвертым выходами блока и со входами дешифратора, выход которого соединен с пятым выходом блока, шестой вход которого соединен со счетным входом четвертого триггера счетчика байтов в блоке буферных регистров, первый вход первого элемента И соединен со вторыми входами второго, третьего и седьмого элементов И, со входом второго элемента НЕ, с первым входом блока, вто- рой вход которого соединен со вторым вхо-

дом первого элемента И и вторым входом пятого элемента И, третий вход блока соединен с третьим входом третьего элемента И, вторым входом четвертого элемента И и входом шестого элемента НЕ, выход к

которого соединен с третьим входом шестого гаемента И, четвертый вход блока соединен со входом третьего элемента НЕ, третьим входом второго элемента И и вторым входом шестого элемента И.

.

121

.45

. 4

2г

J

ш

И

/;г Ь-Я ,j ..V/ № /л- ш r7j7l ;Л Пт

.

J7

А

J#

,л

хЛ

Г

w/i |йЛ Ш РИ Ш Ш

н Тт тг

г

м ед

,146

TFl I

//7

. /

ш

-да 5/

. J/

1

Авторы

Даты

1976-08-15—Публикация

1974-06-27—Подача