(54) СЕЛЕКТОРНЫЙ КАНАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Селекторный канал | 1973 |

|

SU519703A1 |

| Селекторный канал | 1973 |

|

SU491951A1 |

| Устройство для ввода и вывода информации | 1980 |

|

SU905811A1 |

| Мультиплексный канал | 1973 |

|

SU517022A1 |

| Система обмена | 1978 |

|

SU809138A1 |

| Устройство управления каналами | 1973 |

|

SU518769A1 |

| Устройство управления для селекторного канала | 1984 |

|

SU1238095A1 |

Данное изобретение относится к вычислительнбй технике, в частности к организации С1тэуктур селекторных каналов микропрораммных. вычислительных машин.

Иавастны селекторные каналы, содержа- шие счетчик адреса данных, счетчик байтов регистр состояния канала, блок управления интерфейсом, блок контроля последовательност- й сигналов интерфейса, блок контроля по четности,, блок контроля модификации, блок сборки регистров и блок управления каналом.

Цепь изобретения - повышение быстродействия канала и повышение его надежности.

Лрклпагаемый селекторный канал отличается тем, что он дополнительно содержит второй блок контроля модификации, элемент ИЛИ и блок временного контроля интерфейса, первый и второй управляющие Еходь которого собдинены с соответствующймн укравляюи.ями выходами блока улравлеикк канала и блока управления интерфейсом, выход блока временного контроля интерфейса подключен к соответствующему

установочному входу регистра состояния канала, другой(установочный вход которого соединен с выходом элемента ИЛИ , первый и второй входы которого подключены соответственно к выходам блока контроля , модификации . „ и второго блока к.,нтроi fi модификации, информационный и управляющие в коды и выходы -коррекции которого соединены соответственнр с информационным выходом счетчика байгов, управлшощим выходом блока управления канала и вторым управляющим входом счетчика байтов,

Это позволяет повысить быстродействие канала, контролировать одновременно правильность модификации адреса данных к счетчика байтов, контролировать временные соотношения сигналов интерфейса.

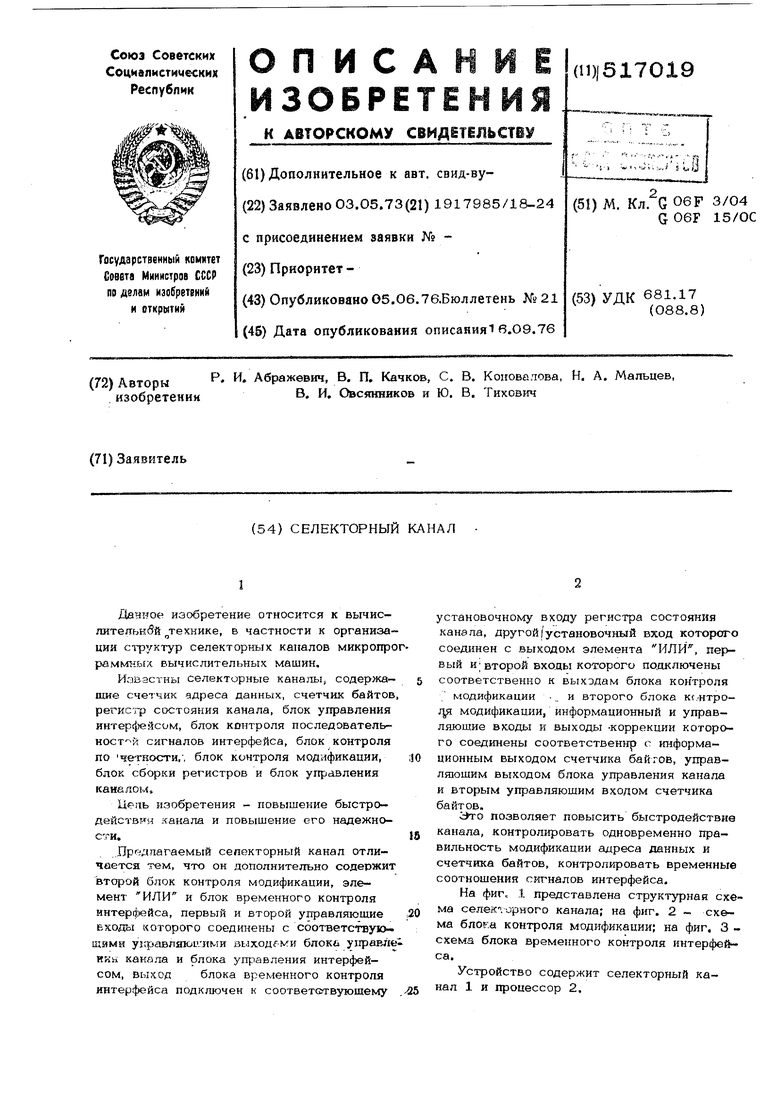

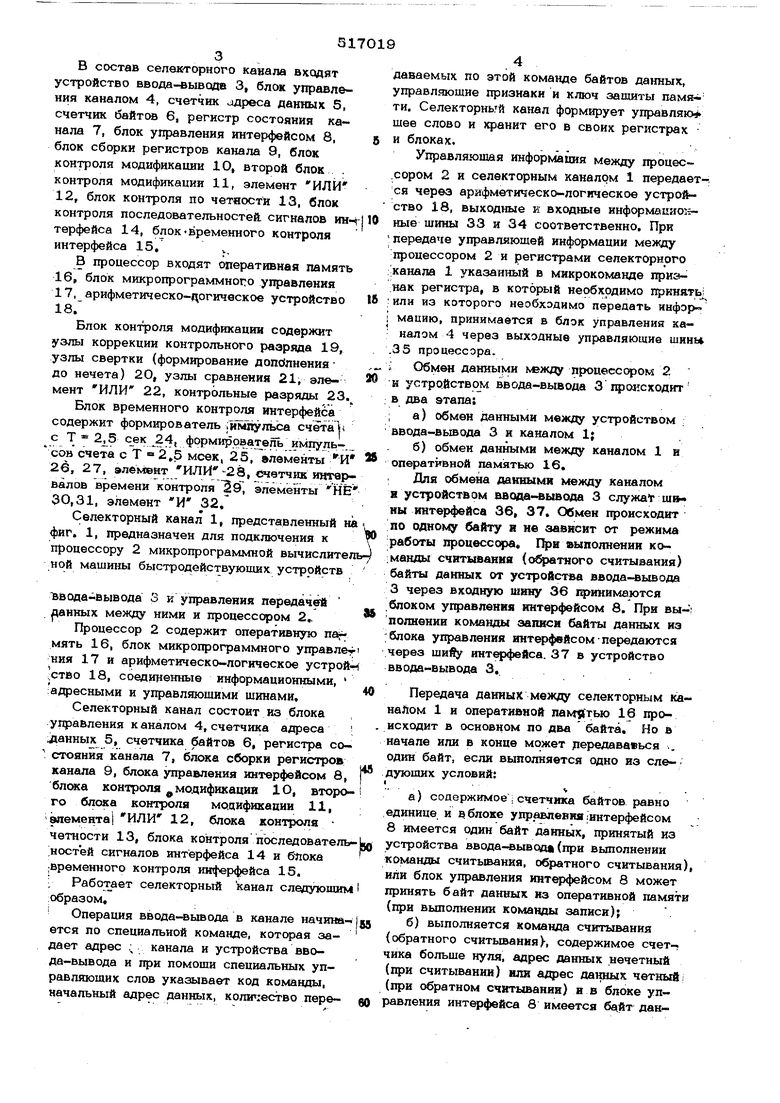

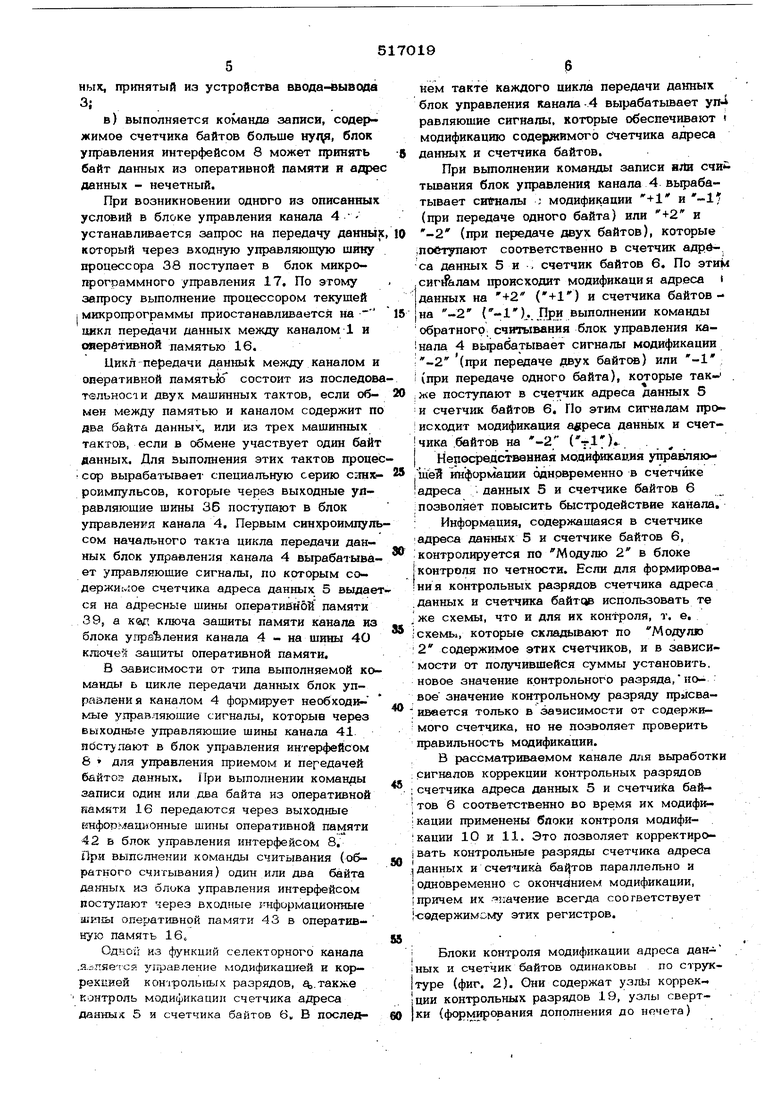

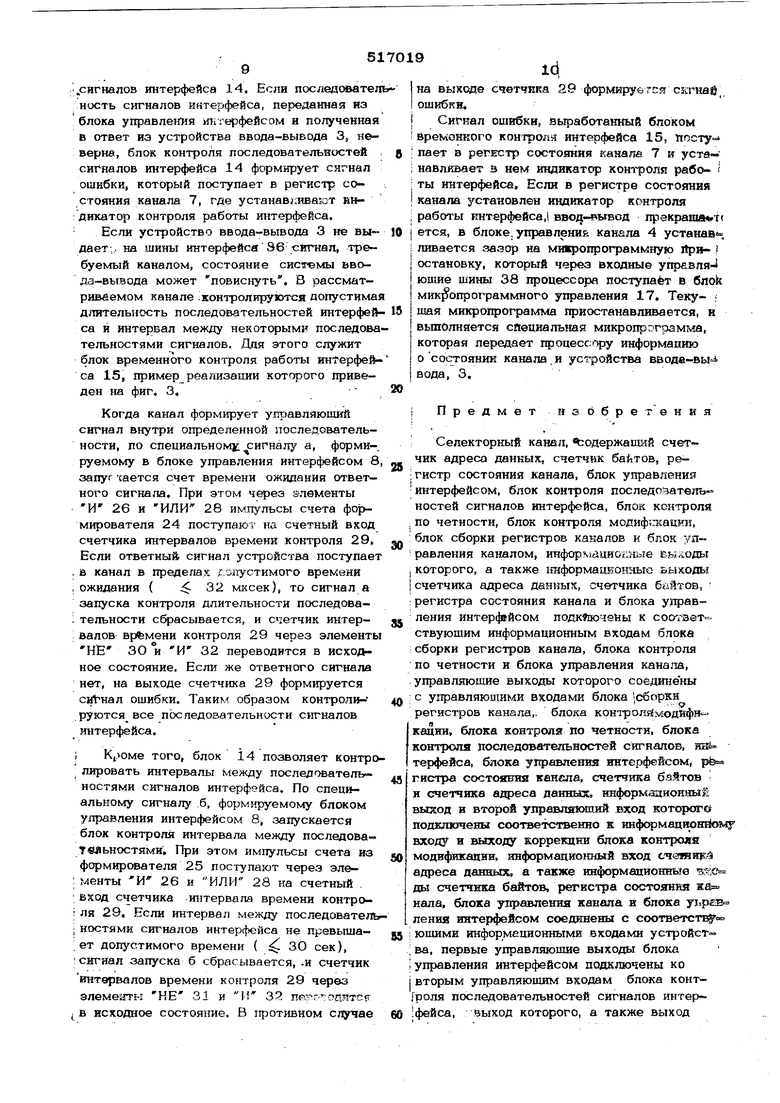

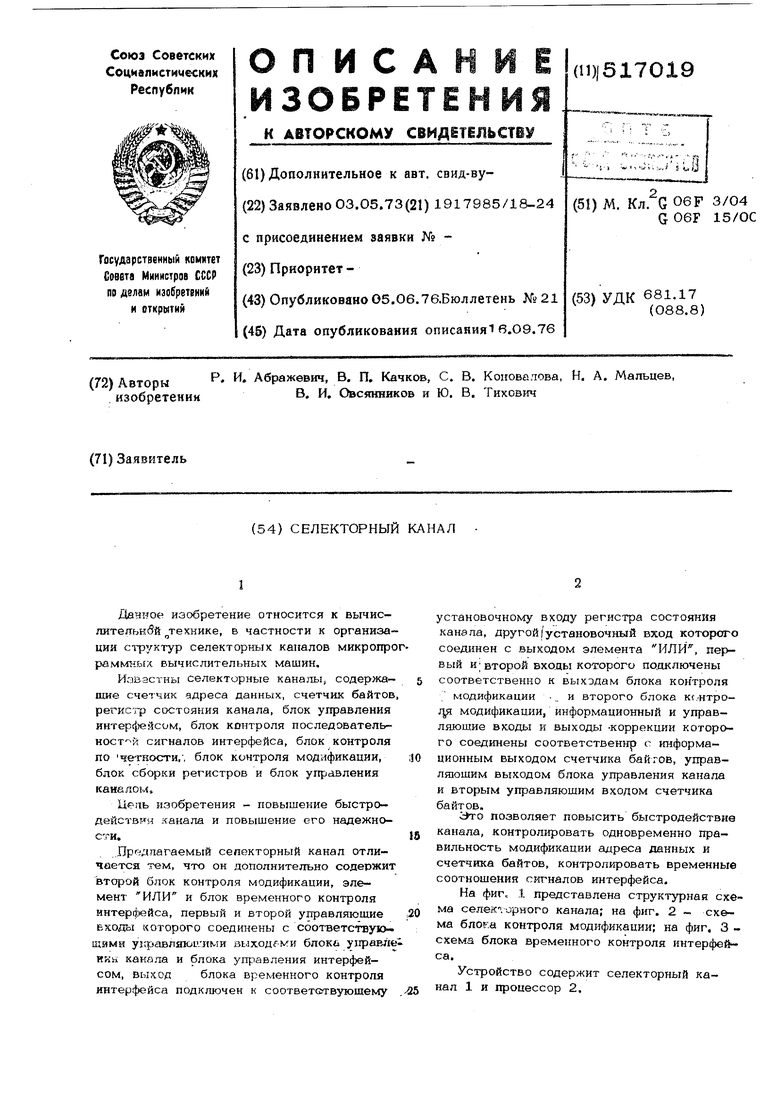

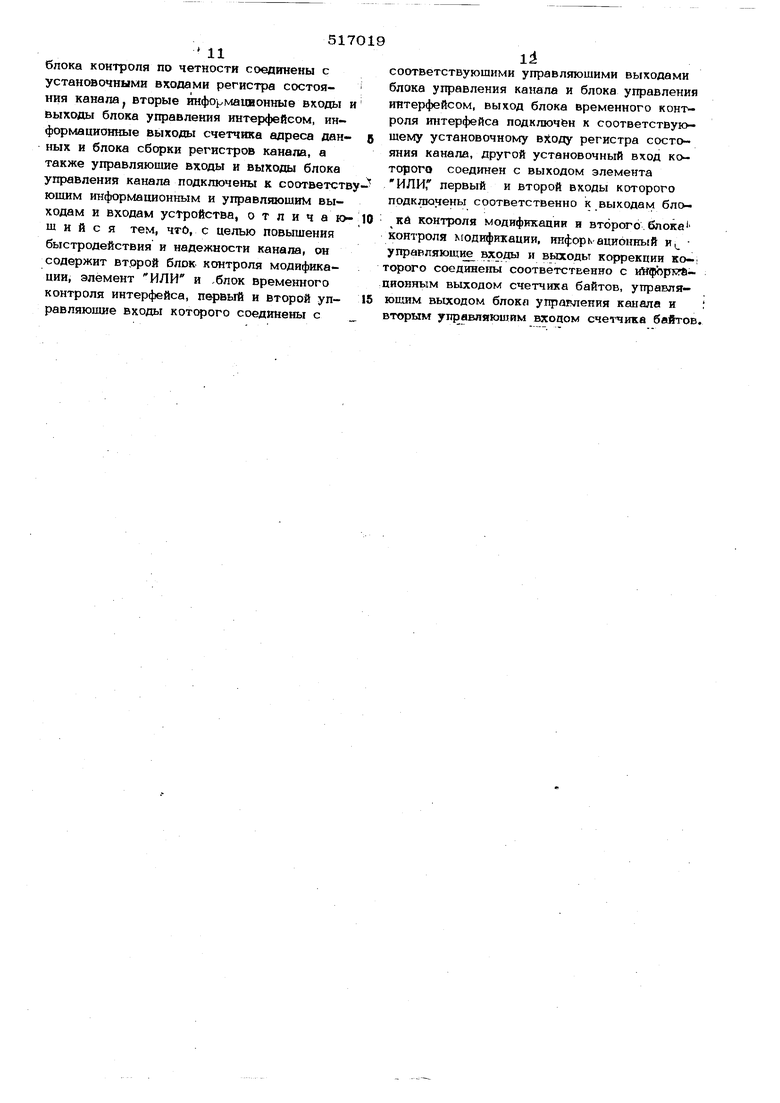

На фиг. 1 представлена структурная схема сележ-. орного канала; на фиг. 2 - схема блока контроля модификации; на фиг, 3 схема блока временного контроля интерфейса.

Устройство содержит селекторный канал 1 к процессор 2,

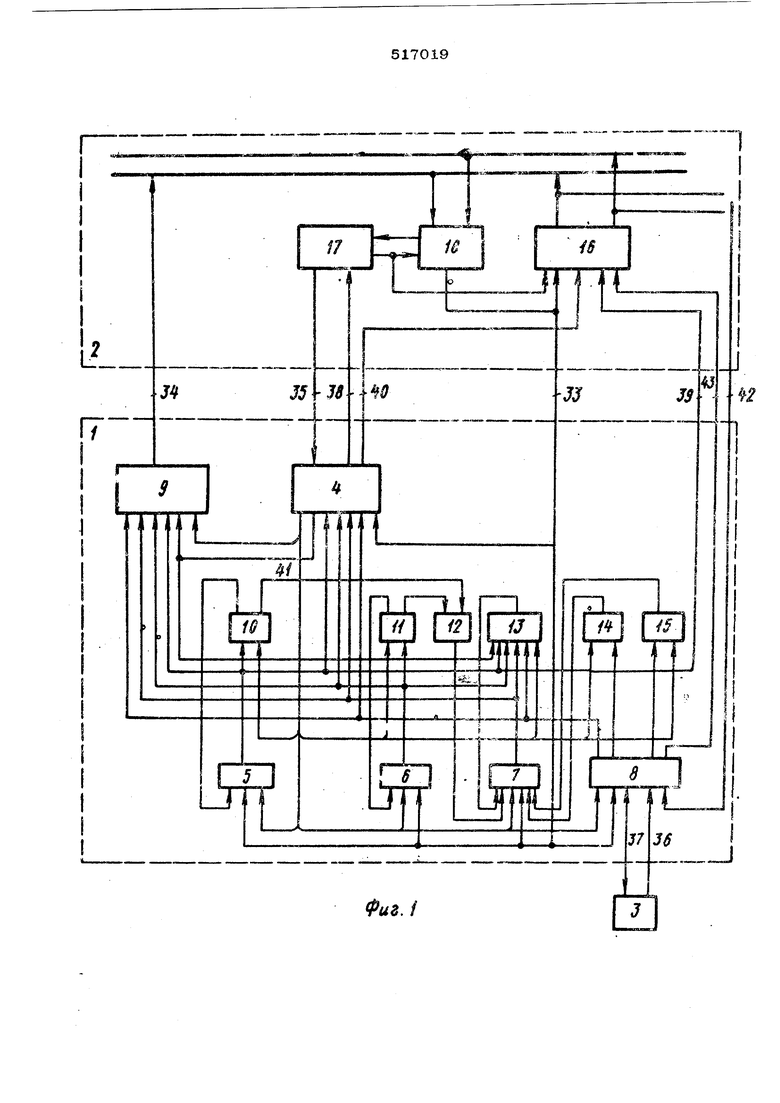

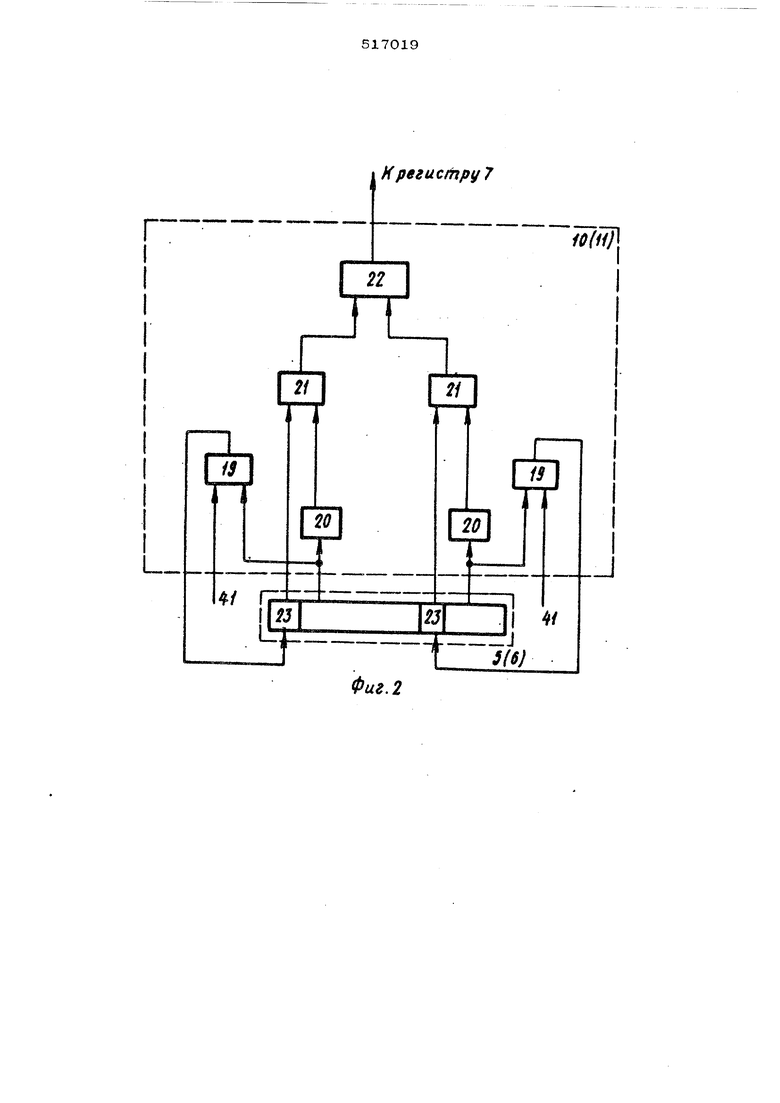

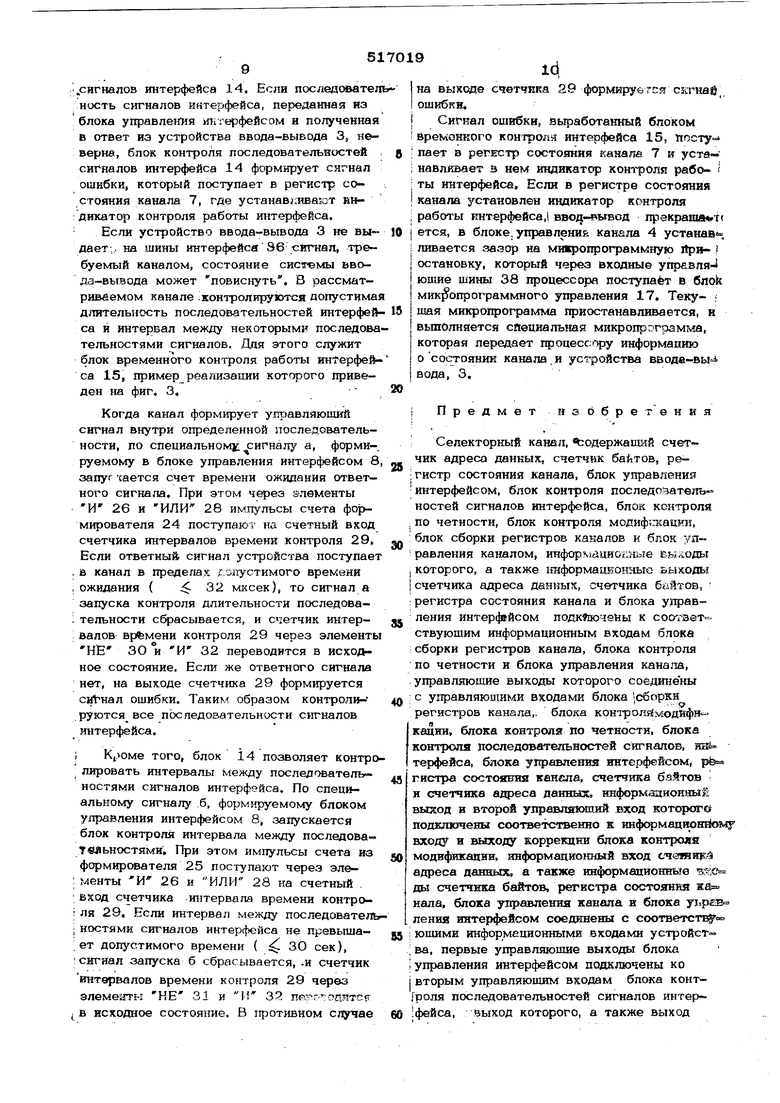

В состав селекторного канала входят устройство ввода-вывода 3, блок управления каналом 4, счетчик адреса датшх 5, счетчик байтов 6, регистр состояния канала 7, блок управления интерфейсом 8, блок сборки регистров канала 9, блок контроля модификации 10, второй блок . контроля модификации 11, элемент ИЛИ 12, блок контроля по четности 13, блок контроля последовательностей сигналов инн терфейса 14, блок-временного контроля интерфейса 15.,.. В процессор входят оперативная память 16, блок микропрограммного управления 17, арифметическо-догическое устройство 18/ Блок контроля модификации содержит узлы коррекции контрольного раарзда 19, узлы свертки (формирование допо лнеиия до нечета) 20, узлы сравнения 21, элемент ИЛИ 22, контрольные разряды 23. Блок временного контроля интерфейса содержит формирователь jliMhynbca счетаЪ с Т сек 24, формирователь импуль-., сов счета с Т мсек, 25, алементы И 26, 27, элемент ИЛИ-28, счетчик интервалов времени контроля 9, элементы НЕ 30,31, элемент И 32/ Селекторный канал 1, представленный ш фиг. 1, предназначен для подключения к процессору 2 микропрограммной вычислите, ной машины быстродействующих устройств :вьода-йывода 3 к управления передачей данных между ними и процессором 2.. Процессор 2 содержит оперативную п мять 16, блок микрохфограммного управлег ния 17 и арифметическо-логическое устрой ;ство 18, соединенные информационными, ;адресными и управляющими шинами. Селекторный канал состоит из блока управления каналом 4, счетчика адреса ланных 5, счетчика байтов 6, регистра состояния канала 7, блока сборки регистров канала 9, блока управления интерфейсом 8, блсжа контроля модификации Ю, второ контроля модификации 11, го блока элементаI ИЛИ 12, блока контроля четности 13, блока контроля последователь костей сигналов интерфейса 14 и бйока ;Временного контроля инферфейса 15. ; Работает селекторный канал следующим образом. Операция ввода-вывода в канале начина ется по специальной команде, которая задает адрес .; канала и устройства ввода-вывода и при помощи специальных управлгаощих слов указывает код команды, начальный адрес данных, коли :ество передаваемых по этой команде байтов данных, управляющие признаки и ключ защиты памяти. Селекторный канал формирует управляю шее слово и хранит его в своих регистрах и блоках.

Управляющая информагшя между процес.сором 2 и селекторным каналом 1 передает-, ся через арифметическо-логическое устройство 18, выходные к входные информаииоз ные шины 33 и 34 соответственно. При передаче управляющей информации между процессором 2 и регистрами селекторного канала 1 указанный в микрокоманде приэнак регистра, в который необходимо пркня.ть или из которого необходимо передать инфэрмаиию, принимается в блэк управления каналом 4 через выходные управляющие шин 35 процессора. Обмен данными между процессором 2 и устройством ввода-вывода 3 хфоисходит в два этапа: а) обмен данными между устройством ; ввода-вьшода 3 и каналом 1;. 6} обмен данными между каналом 1 и оперативной пам:ятью 16. . Для обмена данными между каналом в устройством ваода-вывода 3 служат шины интерфейса 36, 37. Обмен происходит по одному байту и ив зависит от режима :работы процессора. При выполнении ко:манды считывание (обратного считывания) байты данных от устройства ввода-вывода 3 через входную шину 36 пртшимаются блоком управления интерфейсом 8. При вы-: полыении команды записи байты данных из блока управления интерфейсом передаются через шийу интерфейса. 37 в устройство ввода-вывода 3.. Передача даииыХ между селекторным канатом 1 и оперативной 16 происходит в основном по два байта. Но в начале или в конце может дередавасься .. один байт, если выполняется одно из еле-. ДУюших условий: а) содержимое : счетчика байтов равно единице и в блоке управления интерфейсом 8 имеется один байт данных, принятый из устройства ввода-вывода (при выполнении команды считывания, обратного считывания), или блок управления интерфейсом 8 может принять байт данных из оперативной памяти (при выполнении команды записи); б) выполняется команда считывания (обратного считывания К содержимое счетчика больше нуля, адрес данных нечетный (при считывании) или адрес данных четный (при обратном считывании) ив блоке управления интерфейса 8 имеется байт данHbiJt, принятый из устройства ввода-вывода в) выполняется команда записи, содержимое счетчика байтов больше Hyiyj, блок управления интерфейсом 8 может принять байт данных из оперативной памяти и адре данных - нечетный. При возникновении одного из описанных условий в блоке управления канала 4 устанавливается запрос на передачу данны который через входную управляющую шину процессора 38 поступает в блок микропрограммного управления 17. По этому запросу выполнение процессором текущей I микропрограммы приостанавливается на цикл передачи данных между каналом 1 и ояеративной памятью 16. Цикл передачи дaнныk между каналом и оперативной память о состоит из последов тельное и двух машинных тактов, если обмен между памятью и каналом содержит п два байта данных, или из трек машинных тактов, если в обмене участвует один байт данных. Для выполнения этих тактов проце сор вырабатывает специальную серию сшх роимпульсов, которые через выходные управляющие шины 35 поступают в блок управлен1 я канала 4. Первым синхроимпул сом начального такта цикла передачи данных блок управления канала 4 вырабааыва ет управляющие сигналы, по которым содержии1ое счетчика адреса данных 5 выдае ся на адресные шины оперативнбй памяти 39, а кад ключа защиты памяти канала из блока упраЪления канала 4 - на шины 40 ключей защиты оперативной памяти. В зависимости от типа выполняемой команды Б цикле передачи данных блок упрааления каналом 4 формирует необходимые управляющие сигналы, которые через выходные управляющие шины канала 41. в блок управления интерфейсом 8 для управления приемом и передачей байтоз данных. При выполнении команды записи один или два байта из оперативной щамйти 16 передаются через выходные Ешформационные шины оперативной памяти 42 в блок управления интерфейсом 8. При выпслнении команды считывания (о&ратного считывания) один или два байта данных из блока управления интерфейсом поступают через входные гнформационные aimai оперативной памяти 43 в оператив- ную память 16. Одной из функций селекторного канала .я.йляегся уггравление модификацией и коррекцией конлрольных разрядов, .так.е контроль модификации счетчика адреса данных. 5 и счетчика байтов 6, В последнем такте каждого цикла передачи данных блок управления канала -4 вырабатьшает уп равляюшие сигналы, которые обеспечивают t модификацию содержимого счетчика адреса данных и счетчика байтов. При выполнении команды записи вЛи счи тывания блок управления канала 4 вьфабатывает св1гналы ; модификации +1 и -1 (при передаче одного байта) или +2 и -2 (при передаче двух байтов), которые .побтупают соответственно в счетчик адр.ёса данных 5 и , счетчик байтов 6. По этим происходит модификация адреса t данных на +2 (+1) и счетчика байтовна (-1). При выполнении команды обратного; считывания блок управления ка1нала 4 вьфабатывает сигналы модификации -2 (при передаче двух байтов) или -1 i (при передаче одного байта), которые так- . ;Же поступают в счетчик адреса данных 5 и счетчик байтов 6. По этим сигналам npt. I исходит модификация адреса данных и счет чика .байтов на -2 C-rl).. HenoqaeacTBaHHaH модификация упр авлян jiue информации одновременно в счетчике адреса данных 5 и счетчике байтов 6 : позволяет повысить быстродействие канала. : Информация, содержащаяся в счетчике ;адреса данных 5 и счетчике байтов 6, контролируется по Модулю 2 в блоке контроля по четности. Если для фог 1ирования контрольных разрядов счетчика адреса данных и счетчика байтов использовать те же схемы, что и для их контроля, т. е, схемь, которые складашают по Модулю 2 содержимое этих счетчиков, и в зависимости от получившейся суммы установить, новое значение контрольного разр$зда,новое значение контрольному разряду пр 1сваиввется только в зависимости от содержимого счетчика, но не позволяет проверить правильность модификации. В рассматриваемом канале для выработки сигналов коррекции контрольных разрядов счетчика адреса данных 5 и счетчика байтов 6 соответственно во время их модификации применены бйоки контроля модификации 10 и 11. Это позволяет корректировать контрольные разряды счетчика адреса данных и счетчика параллельно и одновременно с окончанием модификации, I причем их качение всегда соогветствует {-содержимому этих регистров. Блоки контроля модификации адреса данНык и счетчик байтов одинаковы по структуре (фиг. 2). Они содержат узлы коррек-. ции контрольных разрядов 19, узлы свертКИ (формирования дополнения до нечета) 2О, узлы сравнения 21 и элементы ИЛИ 22/. Сигналы коррекции соответствукэших контрольных paapsmoB 23 формируются, если: а)при модификации на f+1 один яз чtв ных разрядов соответствующего байта счет;чика адреса данных 5 переходит из нулево го состояния в единичное; б)при М01д11фикац)ни на-- |один из чет .нык разрядов, соотбетствующегй байта счетчика адреса данных 5 или счетчика бай тов 6 . перекроитI из единичного состояния в нулевое; в)tipH модификации на +2 один из нечетных разрядов младшего байта счетчика I адреса данных) 5 переходит из нулевого со Стояния в единичное (анализ старших байтов и коррекция их контрольных разрядов происходят так же, как и гфи модификации на +1); г)при модификации на -2 один из нечетных разрядов младшего байта счетчика адреса данных 5 или счетчика . байтов 6 | переходит из единичного состояния в нуле вое (анализ старших байтов и коррекция и контрольных разрядов происходят так же, как и при модификацщ на -I). В зависимости от вышеперечисленных ус .ловий блоки контроля модификации 1О, 11 вырабатывают сигналы коррекция ссютветствзг ггапих ЕОЕПрольных счетчика адрес данных 5 и счетчика байтов 6, После оконча шя модификапии счетчика адреса данных и счетчиаа байтов при помоши узлов свертки 20 формируются дополнения до нечетасодержимого каждого байта счетчика адреса данных и счетчика байтов, и полученные значения сравнивают ся узлами сравнения 21 с выходами соот- вё1тствуюших контрольных разрядов 23 счет чика адреса данных и счетчика байтов, установленных выходными сигналами узлов коррекции 19, Если эти разряды хотя бы в одном байте счетчика адреса данных или счетчика не совпадают, сигнал несовпадения через элемент ИЛИ 33 поступает в регистр состояния канала 7 и устанавливает в единичное состояние соответствующий индикатор контролй рабо-1 ты канала. Когда заканчивается цикл передачи дай-; ных одного Him двух байтов, блок упрввпвч ния канала 4 сбрасывает запрос на передачу даннык (если к этому моменту не сформирсюаливь условия следующего запроса на передачу данных), пройессор включает серию тактовых,сншфоимпульсоб ,.....|1ч..-.,--(1«..в..,.и,.,.... . ..,.-,,,. .i.i и продолжает выполнение прерванной микро фограммы до следующего запроса на передачу данных. СеиежторныА канал кроме ко.нтроля ностн модификации счетчика данных н счетчика байтов для Еонтршвг выполнения операции вводе-выводе содержит блок контропя ис четности 13, блок временного ко«траля работы интерфейсе 14 Q, блок коитро ля послеД1даатевьностб й сигналов 1гатерфейса 13. Ёлок контроля fco четности 13 вырайа-НЛ-вает сигнал ошибкЛ, если: а) при загрузке управляющей информации в канал содержимое передаваемого регистра имеет четное количество единиц; б) при передаче управляющей информации; и данных из блока управления интерфейсом S в устройство ввода-вывода 3 содержимое передаваемого регистра имеет четное количество единиц;. . .. в) при передаче управляющей инф эмаций и данных в канал из устройства 3 вводавывода содержимое передаваемого регистра имеет четное количество единиц. Сигнал ошибки с блока контроля по четности 13 поступает.в регистр состояния канала 7, в котором устанавливают инд катор контрохш работы интерфейса, если сигнал ошибка выработался при передаче управляющей информации между каналом и устройством ввода-вывода 3. В остальных случаях в регистре состояния канала 7 устанавливают индикатор контроля работы канала. При этом ввод-вывод прекращается, в блоке управления каналом 4 устанавливается запрос на микропрограммную приостановку, котсфый через входные управляющие шины ЗВдПОСтупают в .процессе 2, Выполнение текущей микропрограммы процессора приостанавливается, и выполняется специал микропрограмма, которая передает процессору информацию о состоянии -. канала и устройства ввода-вывода. Для контроля временных соотношений сигналов и последовательности сигналов интерфейса канал 1 содержит блок контро- ля последовательностей сигналов интерфейса 14 и блок временного контроля интерфейса 15, входы которых подключены к управления интерфейсом 8, предназнйченному для управления устройствами ввода-вывода 3, подсоединенньгми к каналу 1 через шйкы интерфейса 36 и 37. Устройство ввода-вывода 3 в ответ на сигналы, вырабатываемые блоком управления интерфейсом 8, формирует сигналы, Которые через шины интерфейса 36 постулают в блок управления интерфейсом. Bbf«оды управляющих триггеров последнего поступают в блок контроля последовательностей .сигналов интерфейса 14. Если последователь ность сигналов интерфейса, переданная из блока управления И1;г€ рфейсо и и полученная в ответ из устройства ввода-вывода 3, неверна, блок контроля последовательностей , д сигналов интерфейса 14 формирует сигнал ошибки, который поступает в регистр состояния канала 7, где устанав ивакзт индикатор контроля работы интерфейса. Если устройство ввода-вывода 3 не вы- 10 дает, на шины интерфейса 36 сигнал, тре буемый каналом, состояние системы ввода-вывода может повиснуть, В рассматриваемом канале контролируются допустимая длительность последовательностей интерфей- 15 са и интервал между некоторыми последова тельностями сигналов. Для этого служит блок временного контроля работы интерфей са 15, пример реализации которого приведен на фиг, 3, Когда канал формирует управляющий сигнал внутри определенной последовательности, по специальному сигналу а, формируемому в блоке управления интерфейсом 8 запуг чается счет времени ожидания ответного сигнала. При этом через элементы И 26 и ИЛИ 28 импульсы счета формирователя 24 поступают на счетный вход счетчика интервалов времени конпроля 29, Если ответный сигнал устройства поступае . в канал в пределах дояустимого времени .ожидания ( 32 мксек), то сигнал а запуска контроля длительности последова; тельности сбрасывается, и с 2етчик интервалов времени контроля 29 через элементы НЕ ЗО и И 32 переводится в исходное состояние. Если же ответного сигнала нет, на выходе счетчика 29 формируется ошибки. Таким образом контролируются все последовательности сигналов интерфейса. i Кроме того, блок 14 позволяет контро лировать интервалы между последовательностями сигналов интерфэйса. По специальному сигналу ,б, формируемому блоком управления интерфейсом 8, запускается блок контроля интервала между последовательностями. При этом импульсы счета из формирователя 25 поступают через эле: менты И 26 и ИЛИ 28 на счетный вход счетчика интервала времени контроля 29, Если интервал между последователе i ностями сигналов интерфейса не превыша; ет допустимого времени ( 30 сек), : сигнал запуска б сбрасывается, .и счетчик интврЕшлов времени контроля 29 через элементы НЕ 31 и 32 пр, г- :одлтс i в исходное состояние. В противном на выходе счетчика 29 формируется ся;гнае ошибки. Сигнал ошибки, выработанный блоком времанкого контроля интерфейса 15( йосту-- пает в регЕстр состояния канала 7 к уста навлквает з нем индикатор контроля работы интерфейса. Если в регистре состояния канала установлен индикатор контроля работы интерфейса, вво;} - М вод npeKpama.t( ется, в блоке, управлений какала 4 устанав ; лнвается зазор на микропрограммную йр остановку, который через входные упра.вля-1 ющие шины 38 процессора поступает в 6rtok мик огфограммного управления 17. Теку- ; щая микропрограмма приостанавливается, и выполняется специальная микропрограмма, которая передает процессгру информацию осостоянии канала,и устройства вводе-вы° вода, 3. I Пред метиаобре тения Селекторный канал, Ч:одержа1ций счетчик адреса данных, счетчик байтов, ре;гистр состояния канзла, блок управления интерфейсом, блок контроля последователь ностей сигналов интерфейса, блок контроля ,по четности, блок контроля модиф;жацин, блок сборки регистров каналов к блок уп- равления каналом, информйциокные , которого, а также ннформааЕонныо БЫКОДЫ счетчика адреса )1Х, счетчика байтов, регистра состояния канала и блока управления интерф йсом подколочены к соответствующим информационным входам блока ;сборки регистров канала, блока контроля по четности и блока управления канала, . управляющие выходы которого соединены ; с управляющими входами блока с6орки регистров канала,- блока кон7рО7 я1модйфнм кадии, блока контроля по четности, блока контроля последовательностей сигналов, ив терфейса, блока управления интерфейсом, рЫ гистра состояния канвла, счетчика байтов и счетчика адреса данных, информадионяый выход н второй управляющий вход которогс подключены соответственно к информацирнйол; входу н выходу коррекции блока контроля моднфнкадии, информационный вход сч янн адреса данньис, а также информационные к& ды счетчика байтов, регистра состояния жа нала, блока управления канала и блока пения интерфейсом соедннены с соответствие I юшнми информеционными входами устройст: ва, первые управляющие выходы блока 1 управления интерфейсом подключены ко i вторым управляющим входам блока конт роля последовательностей сигналов интер бб фейса, выход которого, а также выход 51 блока контроля по четности соединены с установочными входами регистра состояния канала, вторые информационные входы выходы блока управления интерфейсом, информационные выходы счетчика адреса дан ных и блока сборки регистров канала, а также управляющие входы и выходы блока управления канала подключены к соответст юшим информационным и управляющим выходам и входам устройства, о т л и ч а и щ и и с я тем, что, с целью повышения быстродействия и надежности канала, он содержит вт.орой блок контроля модификации, элемент ИЛИ и ,блок временного контроля интерфейса, и второй управляюшие входы которого соединены с соответствующими управляющими выходами блока управления канала и блока управления интерфейсом, выход блока временного контроля интерфейса подключён к соответствующему установочному входу регистра состояния канала, другой установочный вход которого соединен с выходом элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам блокй контроля модификации и второго блока контроля модификации, янфорк ационный И; управляющие входы и выходы коррекции KO-I торого соединены соответственно с иМрЬркг - ционным выходом счетчика байтов, управляющим выходом блокп управления канала и вторым управляющим входом счеччика байтов. Фиг. 1

I±:::-rr

.J

Фиг. 2

Г

г г

io з1

К регистру 7

7Л

23

Ш LEJ

Фиг:3

Авторы

Даты

1976-06-05—Публикация

1973-05-03—Подача