первыми BXOjiaMH penicipa, Biopjjic входы которого соединены с выходом обнаружигсля ошибок кратности /, а выход1,1 роглстра подключены к вторы.м входам блока улраплснпя инверсией. При зто.м вторые вход1 1 лерпой и второй грулн элементов И соединены с .прямыми и инверсными входными шинами устройства соответственио.

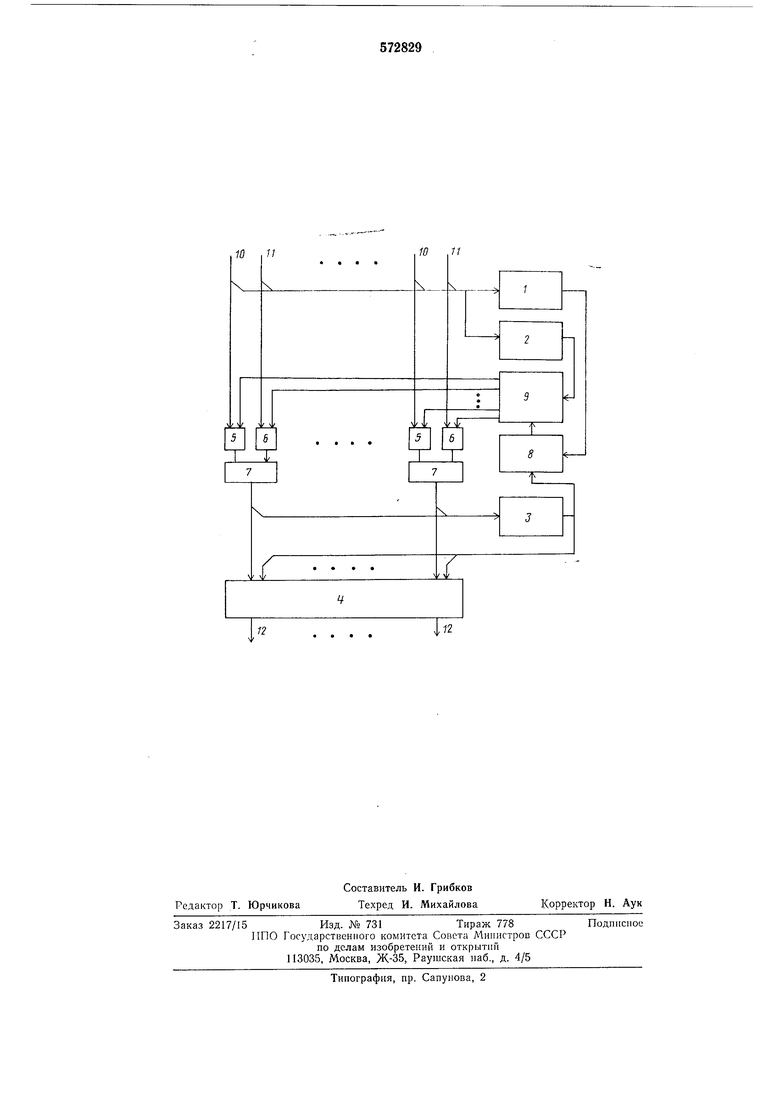

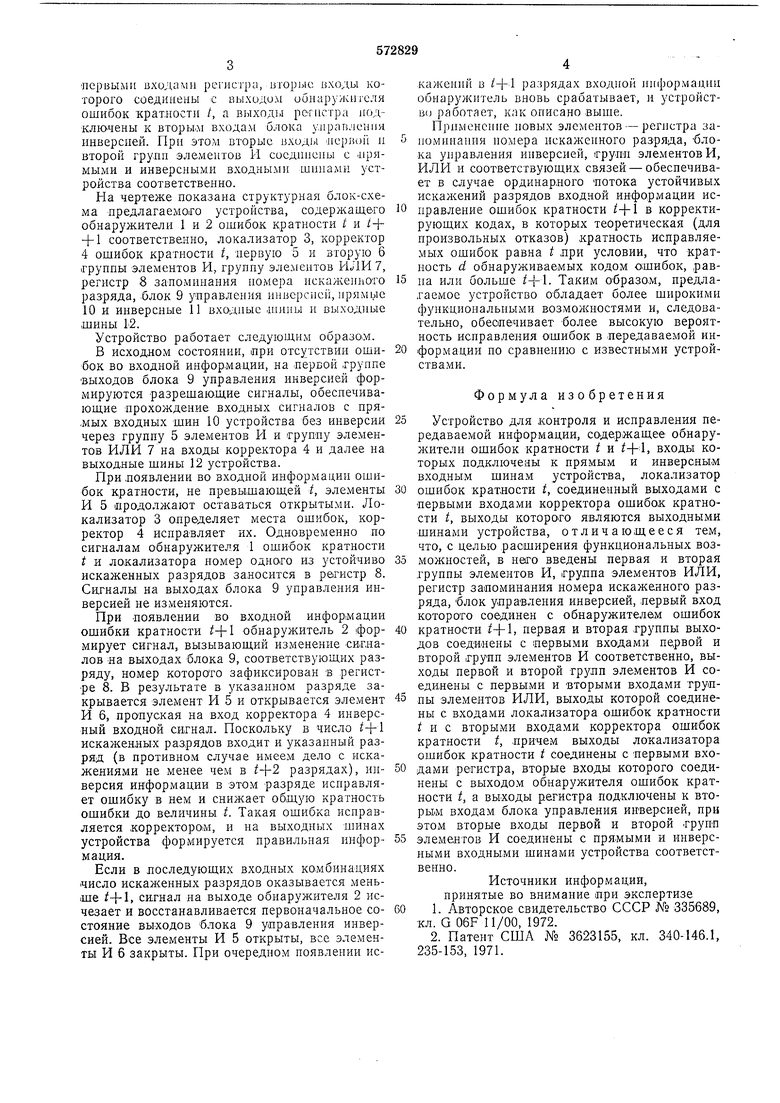

На чертеже иоказаиа структурная блок-схема предлагаемого устройства, содержащего обнаружители 1 и 2 ошибок кратности / и /+ -|-1 соответственно, локализатор 3, корректор 4 ошибок кратиости /, иервую 5 и вторую 6 груииы элементов И, групиу элементов ИЛИ 7, регистр 8 запоминания помера искаженного разряда, блок 9 у правлепия инверсией, нрямыс 10 и инверсные 11 входные шины и выход)1ые шины 12.

Устройство работает следуюш,им образом.

В исходном состоянии, при отсутствии ошнбок во входной информации, на первой группе ВЫХОДОВ блока 9 управления инверсией формируются разрешающие сигналы, обеснечиваюш,ие прохождение входных сигналов с пря,мых входных шин 10 устройства без ииверсии через группу 5 элементов И и группу элементов ИЛИ 7 на входы корректора 4 и далее на выходные шины 12 устройства.

При .появлении во входной информации ошибок кратности, не превышаюш,ей t, элементы И 5 1лродолл ;ают оставаться открытыми. Локализатор 3 определяет места ошибок, корректор 4 исправляет их. Одновременно но сигналам обнаружителя 1 ошибок кратности t и ло,кализатора номер одного из устойчиво искаженных разрядов заносится в регистр 8. Сигналы на выходах блока 9 управления инверсией не изменяются.

При появлении во входной информации ошибки кратности +1 обнаружитель 2 формирует сигнал, вызываюш,ий изменение сигналов на выходах блока 9, соответствуюш,их разряду, номер которого зафиксирован в регистре 8. В результате в указанном разряде закрывается элемент И 5 и открывается элемент И 6, пропуская на вход корректора 4 инверсный входной сигнал. Поскольку в число t искаженных разрядов входит и указанный разряд (в противном случае имеем дело с искажениями не менее чем в t-{-2 разрядах), инверсия информации в этом разряде исправляет ошибку в нем и снижает общую кратность ошибки до величины i. Такая ошибка исправляется корректором, и на выходных шинах устройства формируется правильная инфорнация.

Если в последующих входных комбинациях число искаженных разрядов оказывается меньше +1, сигнал на выходе обнаружителя 2 исчезает и восстанавливается первоначальное состояние выходов блока 9 управления инверсией. Все элементы И 5 открыты, все элементы И 6 закрыты. При очередном ноявлении искажений в Н-1 разрядах входной информации обнаружитель вновь срабатывает, и устройство работает, как описано выше.

Применение новых элементов - регистра заноминапня номера искаженного разряда, блока управления инверсией, групп элементов И, ИЛИ н соответствующих связей - обеспечивает в случае ординарного потока устойчивых искажений разрядов входной информации исправление ошибок кратности /+1 в корректирующих кодах, в которых теоретическая (для произвольных отказов) кратность исправляемых ошибок равна t лри условии, что кратиость d обнаруживаемых кодом ошибок, равна или больше Н-1- Таким образо.м, предлагаемое устройство обладает более широкими функциональными возможностями и, следовательно, обеспечивает -более высокую вероятность исправления ошибок в передаваемой информации по сравнению с известными устройствами.

Формула изобретения

Устройство для контроля и исправления передаваемой информации, содержащее обнаружители ошибок кратности t и , входы которых подключены к прямым и инверсным входным шинам устройства, локализатор ошибок кратности t, соединенный выходами с первыми входами корректора ошибок кратности t, выходы которого являются выходными шинами устройства, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены первая и вторая группы элементов И, группа элементов ИЛИ, регистр запоминания номера искаженного разряда, блок управления инверсией, первый вход которого соединен с обнаружителем ошибок кратности /+1, первая и вторая групиы выходов соединены с первыми входами первой и второй групп элементов И соответственно, выходы первой и второй групп элементов И соединены с первыми н вторыми входами труппы элементов ИЛИ, выходы которой соединены с входами локализатора ошибок кратности и с вторыми входами корректора ошибок кратности t, причем выходы локализатора ошибок кратности t соединены с первыми входами регистра, вторые входы которого соединены с Быходо.м обнаружителя ошибок кратности t, а выходы регистра подключены к вторым входам блока управления инверсией, при этом вторые входы первой и второй групп элементов И соединены с прямыми и инверсными входными шинами устройства соответственно.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 335689, кл. G 06F 11/00, 1972.

2.Патент США № 3623155, кл. 340-146.1, 235-153, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1978 |

|

SU721817A1 |

| Устройство для исправления ошибок в корректирующем коде | 1975 |

|

SU592018A1 |

| Устройство для контроля и исправления информации | 1977 |

|

SU696466A1 |

| Устройство для исправления ошибок в дискретной информации | 1978 |

|

SU860335A1 |

| Устройство для исправления ошибок в дискретной информации | 1980 |

|

SU932645A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297034C2 |

| Пороговый декодер сверточного кода | 1991 |

|

SU1781825A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

12

.12

Авторы

Даты

1977-09-15—Публикация

1975-11-05—Подача