(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ИСПРАВЛЕНИЯ

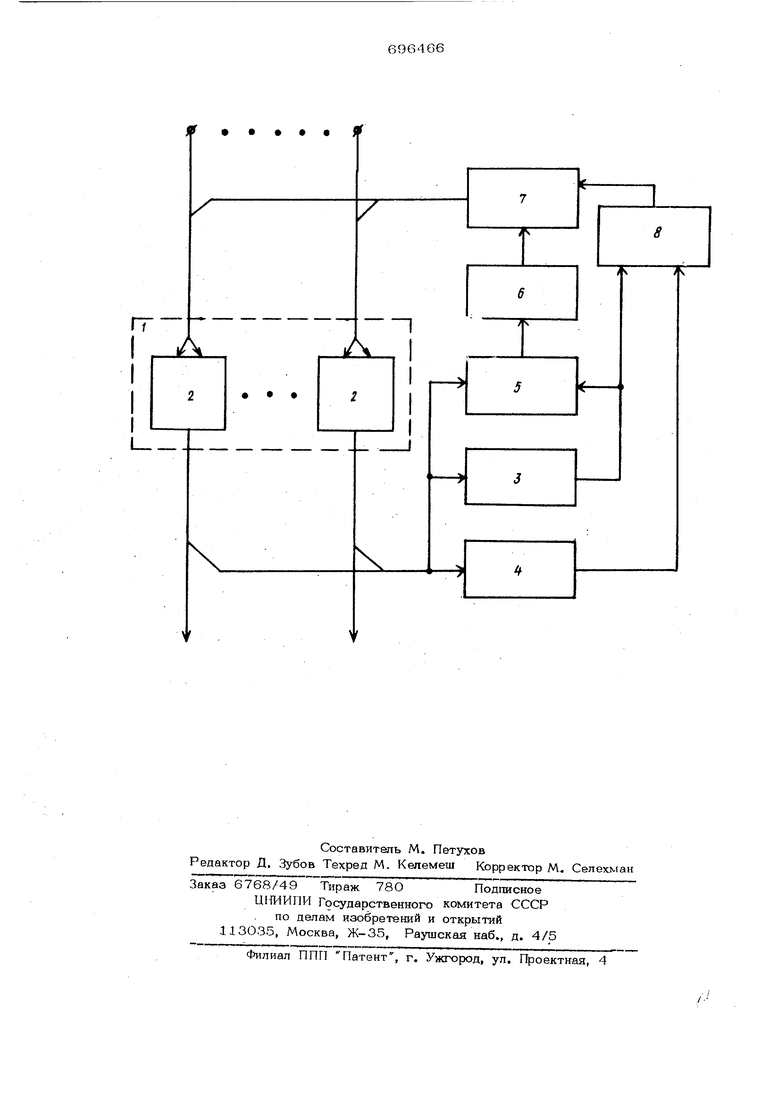

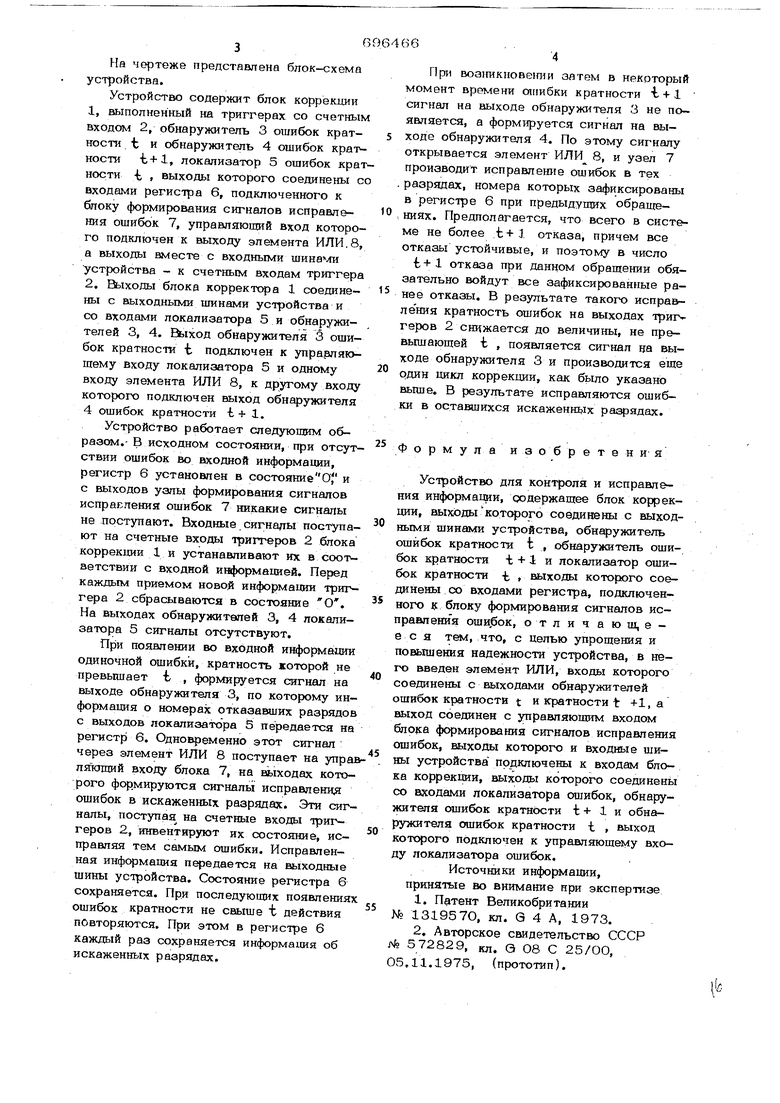

ИНФОРМАЦИИ На чертеже представлена блок-схема устройства. Устройство содержит блок коррекции 1,№1полненный на триггерах со счетным входом 2, обнаружитель 3 ошибок кратности t и обнаружитель 4 ошибок кратности t+l, локализатор 5 ошибок крат ности -t , выходы которого соединены со входами регистра 6, подключенного к блоку формирования сигналов исправления ошибок 7, управляющий вход которого подключен к выходу элемента ИЛИ. 8, а выходы вместе с входными устройства - к счетным входам триггера 2.ВЬ1ходы блока корректора 1 соединены с выходными шинами устройства и со входами локализатора 5 и обнаружителей 3, 4. ЕЬхход обнаружителя 3 ошибок кратности -fc подключен к управляющему входу локализатора 5 и одному входу элемента ИЛИ 8, к другому входу которого подключен выход обнаружителя 4 ошибок кратности -t + 1. Устройство работает следующим образом.- В исходном состоянии, при отсут- ствии ошибок во входной информации, регистр 6 установлен в состояние OJ и с выходов узлы формирования сигналов исправления ошибок 7 никакие сигналы не поступают. Входные поступают на счетные входы триггеров 2 блока коррекции 1 и устанавливают их в соответствии с входной информацией. Перед каждым приемом новой информации триггера 2 сбрасываются в состояние О. На выходах обнаружителей 3, 4 локализатора 5 сигналы отсутствуют. При появлении во входной информации одиночной ошибки, кратность которой не превышает t , формируется сигнал на выходе обнаружителя 3, по которому информация о номерах отказавших разрядов с выходов локализатора 5 передается на регистр 6. Одно еменно этот сигнал : через элемент ИЛИ 8 поступает на упра лякщий входу блока 7, на ш 1ходах которого формируются сигналы исправления ошибок в искаженных разрядах. Эти сигналы, поступая на счетные входы триггеров 2, инвентируют их состоящие, исправляя тем самым ошибки. Исправленная информация передается на ш 1ходные шины устройства. Состояние регистра б сохраняется. При последующих появления ошибок кратности не свыше t действия повторяются. При этом в регистре 6 каждый раз сохраняется информация об искаженных разрядах. При BoairaKHOBeifflH затем в некоторый момент времени оапибки кратности t + 1 сигнал на выходе обнаружителя 3 не появляется, а формируется сигнал на выходе обнаружителя 4. По этому сигналу открывается элемент ИЛИ 8, и узел 7 производит исправление ошибок в тех разрядах, номера которых зафиксированы в регистре 6 при предыдущих обращениях. Предполагается, что всего в сист&ме не более t+J отказа, причем все отказы устойчивые, и поэтому в число t + i отказа при данном обращении обязательно войдут все зафиксированные ранее отказы. В результате такого испра&ления кратность ошибок на выходах триггеров 2 снижается до величины, не превышающей t , появляется сигнал ва выходе обнаружителя 3 и производится еще один цикл коррекции, как было указано выше. В результате исправляются ошибки в оставшихся искаженш 1х разрядах. Ф о р м у л а и 3 о б р е тения Устройство для контроля и исправления информации, содержащее блок коррекции, выходыкоторого соединены с выходными шинами устройства, обнаружитель ошибок кратности t , обнаружитель ошибок кратности -fc + 1 и локализатор ошибок кратности -t , выходы которого соединены со входами регистра, подключенного к блоку формирования сигналов исправления оши,бок, отличаюш,ее с я тем, что, с целью упрощения и повышения надежности устройства, в него введен элемент ИЛИ, входы которого соединены с выходами обнаружителей ошибок кратности t и кратности t +1, а выход соединен с управляющим входом блока формирования сигналов исправления ошибок, выходы которого и входные шины устройства подключены к входам блока коррекции, выходы которого соединены со входами локализатора ошибок, обнаружителя ошибок кратности t + 1 и обнаружителя ошибок кратности t , выход которого подключен к управляющему входу локализатора ошибок. Источники информации, принятые во внимание нри экспертизе 1.Патент Великобритании № 131957О, кл. 6 4 А, 1973. 2.Авторское свидетельство СССР ft} 572829, кл. Q О8 С 25/ОО, 05.11.1975, (прототип).

If

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1978 |

|

SU721817A1 |

| Устройство для контроля и исправления передаваемой информации | 1975 |

|

SU572829A1 |

| Устройство для исправления ошибок в корректирующем коде | 1975 |

|

SU592018A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Устройство для исправления ошибок в дискретной информации | 1978 |

|

SU860335A1 |

| Устройство для исправления @ -кратных ошибок | 1985 |

|

SU1425849A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

S

/ч1

Ч

Авторы

Даты

1979-11-05—Публикация

1977-08-22—Подача