Изобретение касается запоминающих устройств.

Известно устройство для сохранения информации в блоке оперативной памяти, содержащее источник опорного напряжения, датчик рабочего напряжения, ключевые элементы, логические элементы, усилители 1.

Недостатком такого устройства являются большие аппаратурные затраты.

По основному авт. св. 331424 известно устройство, содержащее источник эталонного напряжения, два делителя напряжепия, два усилителя, элемент И, интегратор и преобразователь линейной функции в дискретную, причем входы делителей напряжения соединены с источником питания, а выходы - с первыми входами усилителей, выходы усилителей через последовательно соединенные элемент И, интегратор и преобразователь линейной функции в дискретную соединены с запрещающим входом формирователя тока выборки в блоке оперативной памяти 2.

Недостатком этого устройства является возможность разрушения информации в момент отключения питания. Это объясняется тем, что в момент прихода импульса на запрещающий вход формирователя тока выборки, в случае, если в этот момент происходит запись, из-за ограничения длительности управляющего импульса фронтом импульса запрета, записываемая (считываемая) информация, а также адрес обращения, могут не соответствовать истинному. Кроме того, в связи с тем, что неизвестно, по какому адресу произошел

останов устройства при выключении питания, для возобновления работы после включения питания необходимо вводить целый массив входной информацин. Указанные обстоятельства снижают надегкность устройства.

Целью изобретения является повышение надежности устройства за счет предотвращепия разрушения информации в момент отключения питания и осуществления продолженпя работы при включении питания.

Это достигается тем, что предлагаемое устройство содержит счетчик, триггер, выходпые элементы И, регистр и дополнительные элементы И, входы регистра подключены к выходам выходных элемеитов И, а выходы - ко

входам блока управления, одни входы выходных элементов И соединены с выходами блока управления, другие - с инверсным выходом счетчика, счетный вход которого подключен к выходу первого дополнительного элемента И, а нрямой выход - к одному из входов второго дополнительного элемента И, выход которого соединен со входом формирователя тока выборки, выход преобразователя линейной фз нкции в дискретную соединен с

другим входом второго дополнительного элемента И и одним из входов первого дополнительного элемента И, другие входы которого подключены к одной из управляющих шин, инверсному выходу счетчика и выходу триггера, первый вход которого соединен с выходом основного элемента И, а второй вход - с другой управляющей шиной и управляющим входом счетчика.

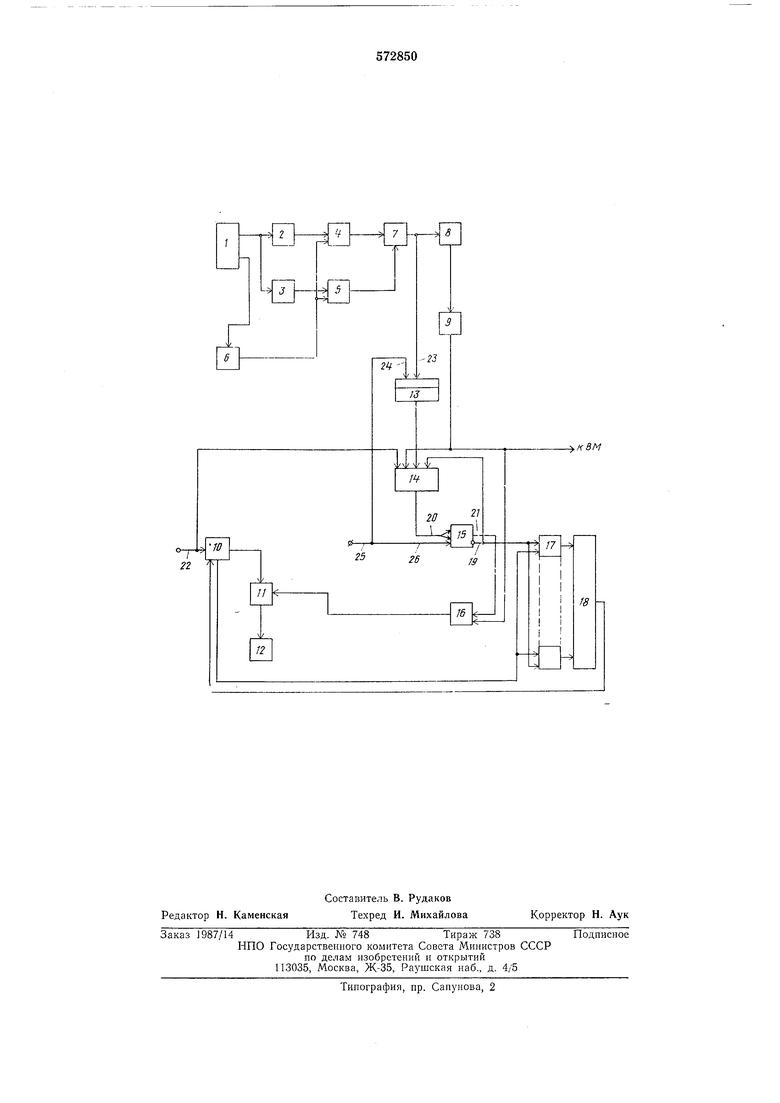

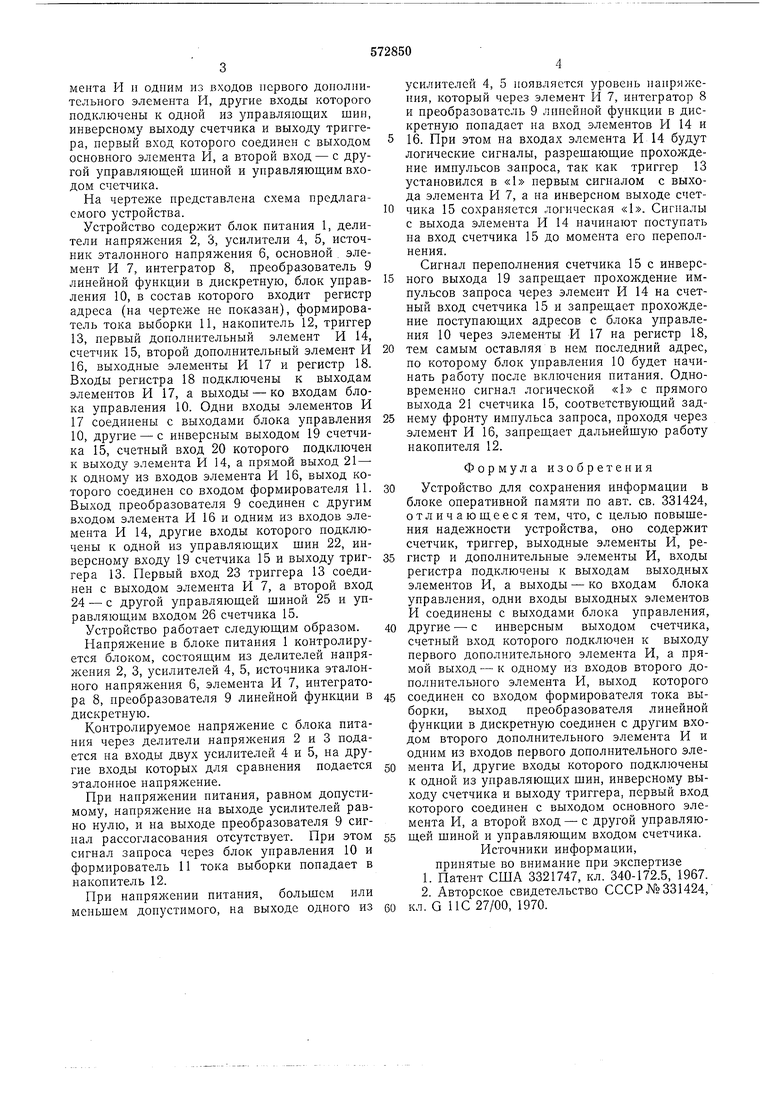

На чертеже представлена схема предлагаемого устройства.

Устройство содержит блок питания 1, делители напряжения 2, 3, усилители 4, 5, источник эталонного напряжения 6, основной . элемент И 7, интегратор 8, преобразователь 9 линейной функции в дискретную, блок управления 10, в состав которого входит регистр адреса (на чертеже не показан), формирователь тока выборки И, накопитель 12, триггер 13, первый дополнительный элемент И 14, счетчик 15, второй дополнительный элемент И 16, выходные элементы И 17 и регистр 18. Входы регистра 18 подключены к выходам элементов И 17, а выходы - ко входам блока управления 10. Одни входы элементов И 17 соединены с выходами блока управления 10, другие - с инверсным выходом 19 счетчика 15, счетный вход 20 которого подключен к выходу элемента И 14, а прямой выход 21 - к одному из входов элемента И 16, выход которого соединен со входом формирователя 11. Выход преобразователя 9 соединен с другим входом элемента И 16 и одним из входов элемента И 14, другие входы которого подключены к одной из управляющих шин 22, инверсному входу 19 счетчика 15 и выходу триггера 13. Первый вход 23 триггера 13 соединен с выходом элемента И 7, а второй вход 24 - с другой управляющей шиной 25 и управляющим входом 26 счетчика 15.

Устройство работает следующим образом.

Напряжение в блоке питания 1 контролируется блоком, состоящим из делителей напряжения 2, 3, усилителей 4, 5, источника эталонного напряжения 6, элемента И 7, интегратора 8, преобразователя 9 линейной функции в дискретную.

Контролируемое напряжение с блока питания через делители напряжения 2 и 3 подается на входы двух усилителей 4 и 5, на другие входы которых для сравнения подается эталонное напряжение.

При напряжении питания, равном допустимому, напряжение на выходе усилителей равно нулю, и на выходе преобразователя 9 сигнал рассогласования отсутствует. При этом сигнал запроса через блок управления 10 и формирователь 11 тока выборки попадает в накопитель 12.

При напряжении питания, больщем или меньщем допустимого, на выходе одного из

усилителей 4, 5 появляется уровень напряжения, который через элемент И 7, интегратор 8 и преобразователь 9 линейной функции в дискретную попадает на вход элементов И 14 и 16. При этом на входах элемента И 14 будут логические сигналы, разрещающие прохождение импульсов запроса, так как триггер 13 установился в «1 первым сигналом с выхода элемента И 7, а на инверсном выходе счетчика 15 сохраняется логическая «1. Сигналы с выхода элемента И 14 начинают поступать па вход счетчика 15 до момента его переполнения.

Сигнал переполнения счетчика 15 с инверсного выхода 19 запрещает прохождение импульсов запроса через элемент И 14 на счетный вход счетчика 15 и запрещает прохождение поступающих адресов с блока управления 10 через элементы И 17 на регистр 18, тем самым оставляя в нем последний адрес, по которому блок управления 10 будет начинать работу после включения питания. Одновременно сигнал логической «1 с прямого выхода 21 счетчика 15, соответствующий заднему фронту импульса запроса, проходя через элемент И 16, запрещает дальнейщую работу накопителя 12.

Формула изобретения

Устройство для сохранения информации в блоке оперативной памяти по авт. св. 331424, отличающееся тем, что, с целью повышения надежности устройства, оно содержит счетчик, триггер, выходные элементы И, регистр и дополнительные элементы И, входы регистра подключены к выходам выходных элементов И, а выходы - ко входам блока управления, одни входы выходных элементов И соединены с выходами блока управления, другие - с инверсным выходом счетчика, счетный вход которого подключен к выходу первого дополнительного элемента И, а прямой выход - к одному из входов второго дополнительного элемента И, выход которого соединен со входом формирователя тока выборки, выход преобразователя линейной функции в дискретную соединен с другим входом второго дополнительного элемента И и одним из входов первого дополнительного элемента И, другие входы которого подключены к одной из управляющих щин, инверсному выходу счетчика и выходу триггера, первый вход которого соединен с выходом основного элемента И, а второй вход - с другой управляющей щиной и управляющим входом счетчика.

Источники информации, принятые во внимание при экспертизе

1.Патент США 3321747, кл. 340-172.5, 1967.

2.Авторское свидетельство СССР №331424, кл. G НС 27/00, 1970.

квм

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство управления | 1986 |

|

SU1409973A1 |

| Аналого-цифровой преобразователь неэлектрических величин | 1985 |

|

SU1403374A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Цифровой измеритель температуры | 1988 |

|

SU1583757A1 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Цифровой кондуктометр | 1986 |

|

SU1374144A1 |

Авторы

Даты

1977-09-15—Публикация

1976-03-24—Подача