1

Изобретение относится к области авто матики и вычисли/ельной техники и может быть использовано в вычислительных средах.

Известны ячейки памяти для матричног коммутатора, позволяющие производить последовательную сборку соединительных путей подачей сигналов по координатным шинам.

Одна из известных ячеек памяти 1 с держит триггер, прямой выход которого соединен с переключающими МОП-транзисторами. Вход установки триггера соединен с трехвходовым элементом И, а вход сбро са - с щииой управления. Переключением МОГ -транзисторов управляет триггер, ко, торый устанавливается в единичное состсь яние при одновременном появлении на входах трехвходового элемента И сигналов горизонтального и вертикального поиска

и сигнала установки соединения. Однако такая ячейка памяти для коммутирующей матрицы не позволяет производить поиск нескольких точек соединения путем пдно« временной пойачи управляющих сигналов

по нескольким координатным шкнам У. и нескольким координатным шинам Y , Крп ме того, в этой ячейке : раздепэны инфор« мационные и управляющие к,рординатные щины, что увеличивает число выводов в ячейке.

Известна ячейка, содержащая кроме григIepa, переключающнх МОП-транзисторов и трехвходового элемента И, дополнительный МОП-транзистор, включенный между переключающими МОП-транзисторами и триггером .2. Эта ячейка позволяет оставлять переключающие МОП-транзисторы в неизмо ном состоянии в момент переключения триг гера. Такая ячейка имеет те же недостатки, что и ячейка .

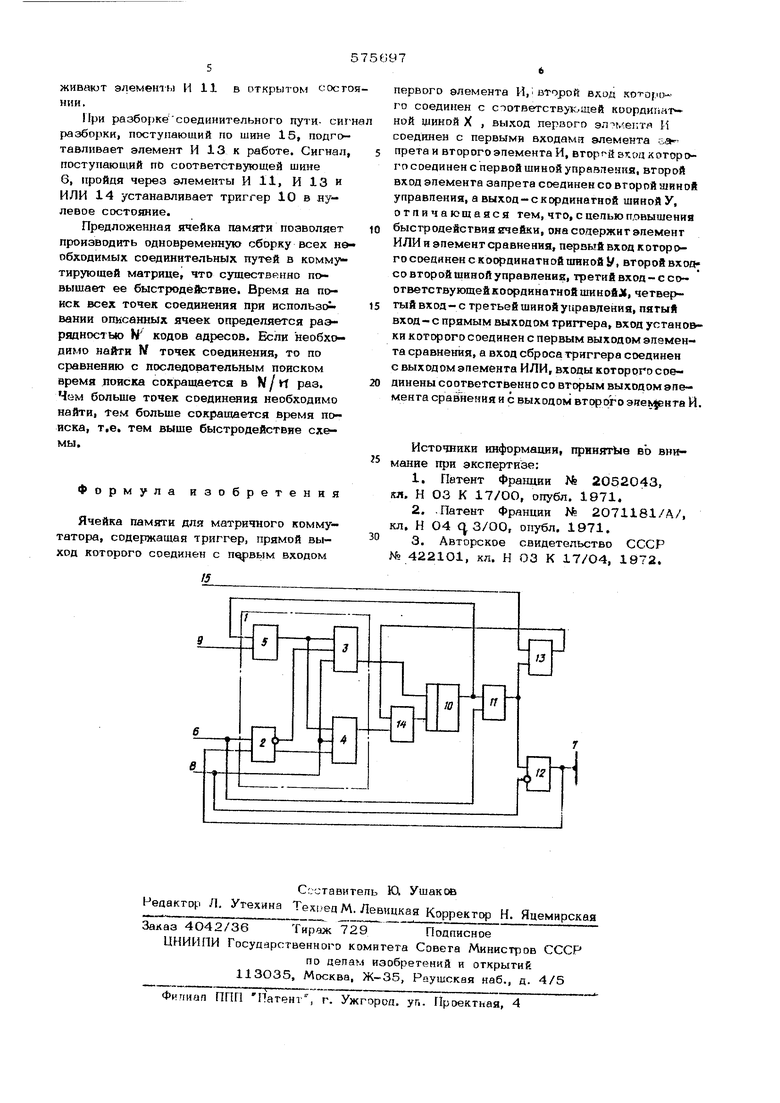

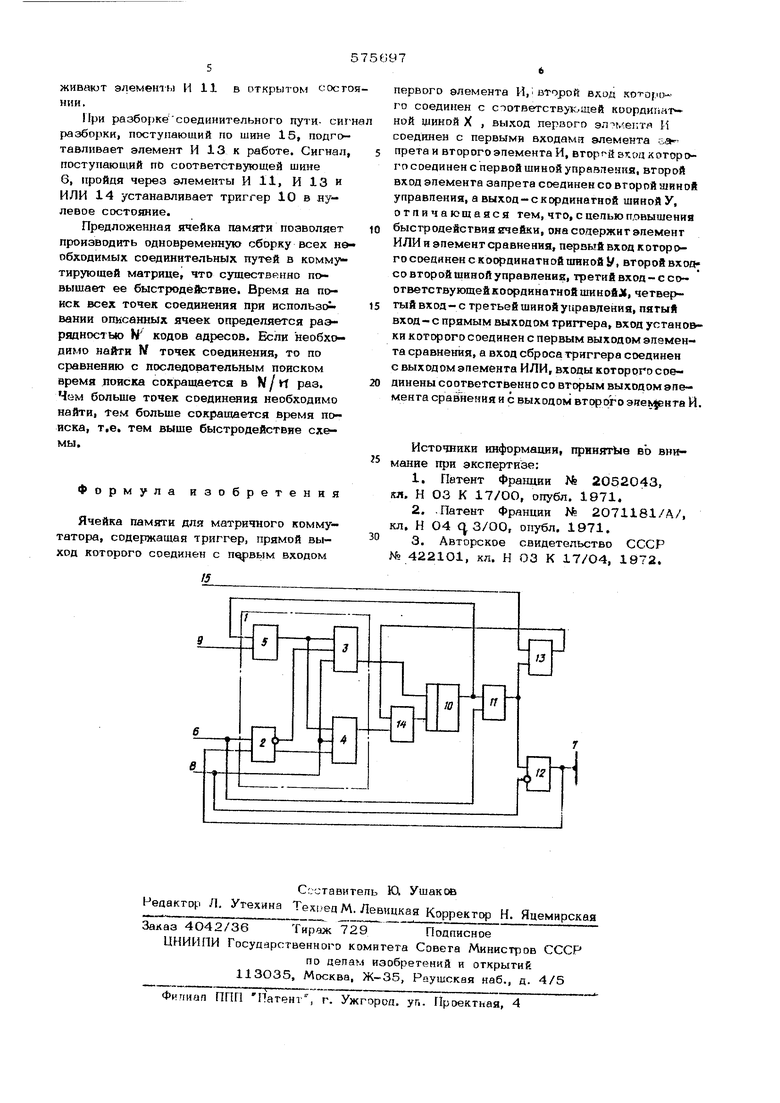

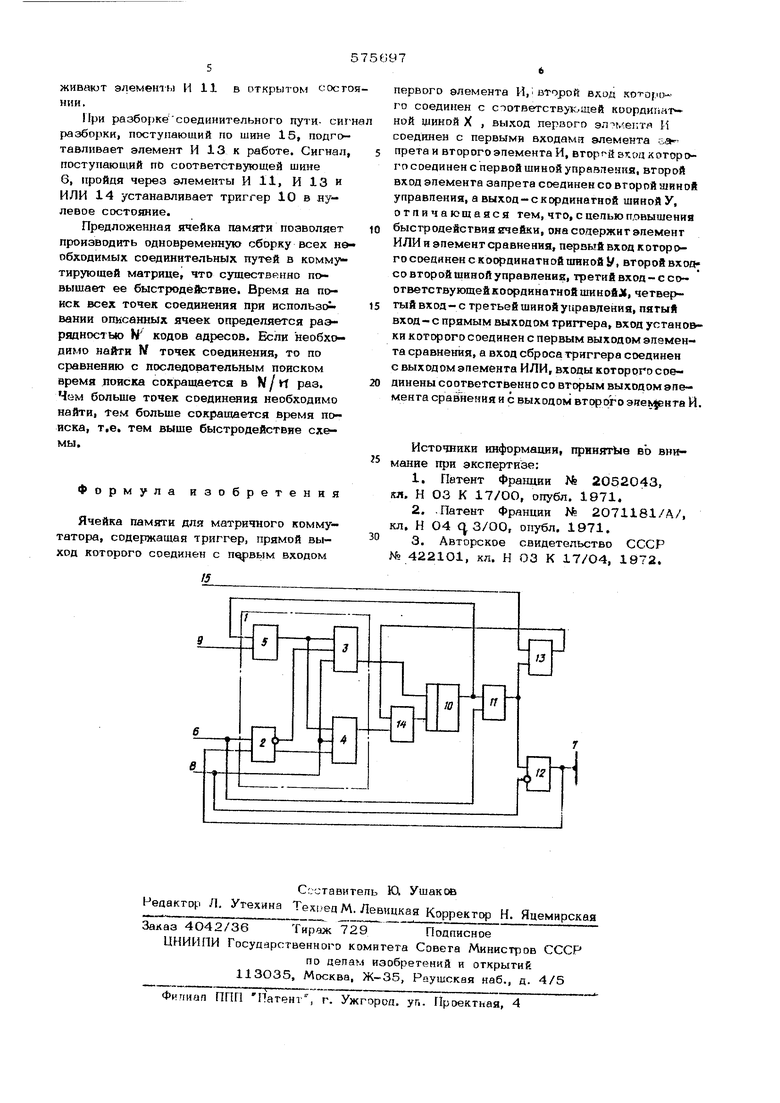

Наиболее близким техническим рещенп.ем к изобретению является ячейка памяти sj, содержащая триггер, прямой выход которого соединен с первым входом первого элемента И, второй в;;од которого соединен с соответствующей координатной ши ной X . Выход первого элеме1 та И соопинен с первыми входами элемента запрета и второго элемента И, второй вход которого соединен с первой шиной управления. Второй вход элемента запрете соединен со вто рой шиной управления, а выход элемента с координатной шиной Y Эта ячейка памяти не позволяет провод поиск нескольких точек соединения подачей управляющих сигналов одновременно по нескольким координатным шинам У и неско КИМ координатным шинам Y , так как в это случае в матричном коммутаторе появляются ложные точки соединения и существе но снижается ее быстродействие. Целью изобретения является повышение быстродей.. ..л ячейки памяти. Поставленная цель достигается тем, что предложенная ячейка памяти содержит элемент ИЛИ и элемент сравнения, первый вход которого соединен с координатной шиной V , второй вход - со второй шиной управления, третий вход - с соотве1ч:тву ющей координатной шиной X , четвертый вход - с третьей шиной управления, пятый вход - с прямым выходом , вход установки которого соединен с первым выходом элемента сравнения. Вход сброса триггера соединен с выходом эл&мгзнта ИЛИ, входы которого соединены со- ответственно со вторым выходом элемента сравнения и с выходом второго элемен та И. На чертеже представлена фун1ациональна схема ячейки памяти матричного коммута™ тора. Элемент 1 сравнения предназначен для сравнения адресных кодов и выработки сиг налов равенства или неравенства кодов и состоит из элемента 2 сложения по модулю два, элементов И 3 и 4 и элемента ИЛИ 5. Входы элемента 2 соединены с со ответотвующей координатной шиной У. 6 координатной шиной У 7. Прямой выход элемента 2 соединен со входом элемента И 4, а инверсный со входом элемента И 3. Вторые входы этих элементов И соединены с ШИНОЙ управления 8, а третьи выходом элемента ИЛИ 5. Выход элемента И 3 является первым выходом а выход элемента И 4 вторым выходом элемен га 1 сравнения. Входы элемента ИЛИ 6 соединены с шиной 9 управления и с прямым выходом триггера Ю. Триггер 10 предназначен для угфавлени работой элемента 1 сравнения и элемента И 11. Элемент И 11 является частью соедини тельного пути. Управляющий вход алеме та И 11 соединен с прямым выходом соот ввтствуюшего триггера 10, а информадио - - ный - с шиной X 6. Выход элемента И 11 соединен со входом элемента 12 запрета для передачи информационного сообшекия и со входом элемента И 13 для передачи сигнала {зазборки, поступаюшего по cooTBeTCTBjToщей шине X 6. Элемент 12 запрета предназначен для блокировки передачи информации с выхода элемента И 11 на шину Y 7 в режиме сборки соединительного пути и для разрешения ее поступления в режиме передачи информациогшого сообщения. Запрещаюший вход этого эл емента соединен с шиной 8. Элемент И 13 предназначен для выработки сигнала, сбрасываюшего триггер 10 в нулевое положение. Его выход через элемент ИЛИ 14 соединен со входом триггера 10, а второй вход - с швной 15 управления. Ячейка работает следующим образом. Для сборки соединительных путей по шине 8 подается сигнал сборки, который запрещает передачу информации через элемент 12 запрета и подготавливает элементы И 3 и 4 к работе. Поиск точек соединения в матричном коммутаторе, cocтo щем из таких ячеек,производитея передачей по шине Y 7 кода ее адреса, а по каждой шине У 6 кода адреса той шины У 7, с которой необходимо ее соединить. Коды, поступающие по шинам Y 7 к X 6, пораэрядно поступают на элементы 2. При равенстве поступивших разрядов единичный сигнал появляется на инверсном выходе элемента 2, при неравенстверазрядов - на прямом выходе элемента 2. Одновременно с поступлением на элемент 1 сравнения первых разрядов сравниваемых кодов на элементы И 3 и 4 через элемент ИЛИ 5 поступает запускающий с шины 9. Если первые разряды кодов одинаковы, то единичный сигнал с инверсного выхода элемента 2 проходит через элемент И 3 на вход установки триггера 1О и переводит его в единичное состояние. Потенциал с прямого выхода триг гера 1О, поступая через элемент ИЛИ 5 на элементы И 3 и 4, разрешает сравненке следующих разрядов. Каждый следующий снгЬс,л равенства подтверхсдает единичное состощше триггера 10. Сигнал неравенства, выработанный элементом 2 на любом шаге сравнения, пройдя через элементы И 4 и ИЛИ 14 устанавливает триггер 10 в нулевое состояние и тем самым прекращает дальянейшее сравнение на этом элементе 1 сравнения. Сборка соединительных путей заканчи.-. вается после прохождения последних разрядов кодов по координатным шинам. Для этого с шины 8 снимается си1-.яал сборки. Триггеры lOjHa которые не 1шдан сигнал перавем ства, остаются в единичном состоянии и уде}

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Трехкаскадная коммутирующая система | 1984 |

|

SU1226481A1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Устройство для программного управления позиционного типа | 1983 |

|

SU1158976A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| ПРОГРАММИРУЕМОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1999 |

|

RU2154852C1 |

| Устройство для отображения символов на экране электронно-лучевой трубки | 1991 |

|

SU1800475A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

Авторы

Даты

1977-10-05—Публикация

1975-08-22—Подача