Устройство относится к средствам управления и может применяться при автоматизации в технологических процессах и в производстве.

Известно устройство, содержащее входной блок, блок коммутации, подключенный своим выходом к вычислительному блоку, выход которого связан с блоком оперативной памяти и выходным блоком, программный блок, связанный выходами через командные и адресные шины с входами всех вышеперечисленных блоков, генератор импульсов /А.С. N 1652964 G 05 B 19/08, 1991 г./.

Недостатком данного устройства является сложность коммутационного и вычислительного блоков.

Наиболее близким по технической сущности является устройство, содержащее входной и выходной блоки, блоки оперативной памяти и синхронизации, адресные шины, генератор импульсов, программный блок, блок коммутации и вычисления, состоящий из трехвходового дешифратора, трех двухвходовых элементов И, элемента ИЛИ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и управляемой ячейки памяти, командных шин, поступающих с соответствующих выходов программного блока /патент N 1801223 от 9.10.92 г./.

К недостаткам этого устройства можно отнести относительно низкое быстродействие, связанное с большим количеством тактов при вычислении логических функций.

Целью предлагаемого изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, коммутационно-вычислительный блок, содержащий трехвходовый дешифратор, элемент 2-2И-2ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и первый элемент И, первые входы элемента 2-2И-2ИЛИ соединены соответственно с первым и вторым выходами дешифратора, вторые входы элемента 2-2И-2ИЛИ подключены соответственно к выходу входного блока, соединенного первой и второй группами входов соответственно к выходу входного блока, соединенного первой и второй группами входов соответственно с группой информационных выходов объекта управления и с соответствующими адресными шинами, поступающими с выходов объекта управления и с соответствующими адресными шинами, поступающими с выходов программного блока, и к выходу блока оперативной памяти, выход элемента 2-2И-2ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с соответствующим командным выходом программного блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом первого элемента И, подключенного вторым входом к первому выходу блока синхронизации, соединенному вторым выходом с первыми управляющими входами блока оперативной памяти и выходного блока, группа входов которых соединена с группой адресных выходов программного блока, а информационные входы объединены, третий выход блока синхронизации соединен со счетным входом программного блока, третий и четвертый выходы дешифратора связаны соответственно с вторыми управляющими входами блока оперативной памяти и выходного блока, в командно-вычислительный блок введены управляемая ячейка памяти с прямым и инверсным выходами, второй, третий и четвертый элементы И, элемент ИЛИ и элемент НЕ, причем управляющий вход ячейки памяти соединен с выходом первого элемента И, ее информационный вход связан с выходом элемента ИЛИ, первый вход которого подключен к выходу второго элемента И, первый вход последнего соединен с первым входом третьего элемента И и с соответствующей командной шиной программного блока, а второй вход с выходом элемента НЕ, вход элемента НЕ связан со вторым входом третьего элемента И и первым входом четвертого элемента И, второй вход которого подключен к инверсному выходу ячейки памяти, его же выход соединен с вторым входом элемента ИЛИ, прямой выход ячейки памяти связан с информационными входами выходного блока и блока оперативной памяти и третьим входом третьего элемента И, его четвертый вход подключен к третьему выходу блока синхронизации, а выход третьего элемента И соединен с введенным также блоком прерывания, содержащим элемент И, первый и второй электронные ключи, ячейки памяти с управляющими входами, причем первый электронный ключ связан информационными входами с четырьмя соответствующими командными шинами программного блока, управляющим входом с соответствующей командной шиной программного блока, а выходы первого электронного ключа подключены соответственно к трем входам дешифратора и входу элемента НЕ коммутационно-вычислительного блока, ячейки памяти соединены информационными входами с соответствующими командными и адресными шинами, идущими с выходов программного блока, а управляющими входами с выходом элемента И, входы которого связаны соответственно с вторым выходом блока синхронизации и с управляющим входом первого электронного ключа, выходы ячеек связаны с информационными входами второго электронного ключа, управляющий вход которого подключен к выходу третьего элемента И коммутационно-вычислительного блока, в выходы второго электронного ключа соединены с установочными входами программного блока.

Предлагаемое устройство поясняется фиг. 1

Устройство состоит из входного блока 1, соответствующие входы которого подключены к первичным датчикам /на чертеже не показаны/, с которых поступают сигналы X1. ..X, и адресным шинам, а выход соединен с блоком коммутационно-вычислительным /далее БКВ/ 2, содержащим дешифратор 3, связанный двумя выходами соответственно с входами элемента 2-2И-2ИЛИ 4, выход которого через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5 и первый элемент И 6 подключен к управляющему входу ячейки памяти с прямым и инверсным выходами 7, информационный вход которой соединен с выходом элемента ИЛИ 8, первый вход которого связан с выходом второго элемента И 9, входы последнего связаны с входом третьего элемента И 10 и выходом элемента НЕ 11, вход которого подключен к входу четвертого элемента И 12, прямой выход ячейки памяти соединен с информационными входами выходного блока 13 и блока оперативной памяти 14, связанных входами с одним из выходов блока синхронизации 15, другой выход которого соединен с входом программного блока 16, выходы последнего связаны с блоком прерывания 17, содержащего первый электронный ключ 18, связанный своим управляющим входом с первым входом элемента И 19, выход которого подключен к управляющим входам ряда ячеек памяти 20, прямые и инверсные выходы которых соединены с входами второго электронного ключа 21.

C1...C6, Cj+1 - командные шины с выходов программного блока 16 C7...Cj - адресные шины с выходов программного блока 16, определяющие адреса операндов X1...Xn входного блока 1 и соответствующих адресов ячеек памяти блока оперативной памяти и выходного блока /14, 13/.

- сигналы, устанавливающие счетные триггеры во внеочередной такт в блоке программ 16, где

- сигналы, устанавливающие счетные триггеры во внеочередной такт в блоке программ 16, где  принимает значение a и a'.

принимает значение a и a'.

В качестве ячейки памяти 7 можно использовать стандартный двухступенчатый Д-триггер.

Работа первого электронного ключа /далее ЭК1/ 18 заключается в том, что при подаче на его вход команды Cj+1=1, на его выходах C'3...C'6 присутствуют логические нули, независимо от значений сигналов на его входах C3...C6. При Cj+1= 0 значения на выходах C'3...C'6 повторяют значения на входах C3...C6 ЭК1, 18.

Работа ряда ячеек памяти /далее ЯП/ 20 состоит в том, что при команде на их управляющем входе Cj+1=1 происходит запись значений сигналов на входах C3. . .Cj в ячейки памяти ЯП 20 в момент поступления сигнала из программного блока 15, что фиксируется сигналом на выходе элемента И 19.

Работа второго электронного ключа /далее ЭК2/ 21 заключается в том, что при единичной команде, поступающей на его командный вход с выхода третьего элемента И 10, прямые и инверсные значения сигналов C3...Cj, ранее записанных в ряд ЯП 20, считываются и в виде сигналов a1...am поступают на установочные входы счетных триггеров 46 /см. далее по тексту/ программного блока 17, устанавливая триггеры 46 в определенное положение, соответствующее внеочередному такту.

Входной блок 1 /фиг. 2/ содержит элементы согласования 22, связанные входами X1. . .Xn с датчиками, а выходами с первыми входами элементов И 23, выходы которых, через элемент ИЛИ 24 соединены с блоком 2, а вторые входы элементов И 23 подключены к выходам дешифратора 25, входы которого соединены адресными шинами с блоком программ 16. В соответствии с сигналами C7...Cj адресных шин переменные X1...Xn поочередно считываются и подаются на вход блока 2.

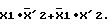

Блок оперативной памяти 14, представленный на фиг. 3, содержит элементы И 26 обращения к ячейкам памяти 27, элементы считывания 28 /например элементы И/, элемент ИЛИ 29, первый и второй дешифраторы 30, при этом через соответствующий элемент 26 или 28 заносится или считывается информация по командам из дешифратора 3 блока 2 и в соответствии с сигналами C7...Cj адресных шин.

Выходной блок 13 /фиг. 4/ состоит из элементов И 31, ячеек памяти 32, куда заносится информация с выхода ячейки памяти 7 блока 2, и соответствующих усилителей 33, передающих логические сигналы из ячеек памяти на электроприводы и т. д. по адресам, определяемым сигналами C7...Cj и соответствующей командой с выхода дешифратора 3 блока 2, которые поступают на соответствующие входы дешифратора 34.

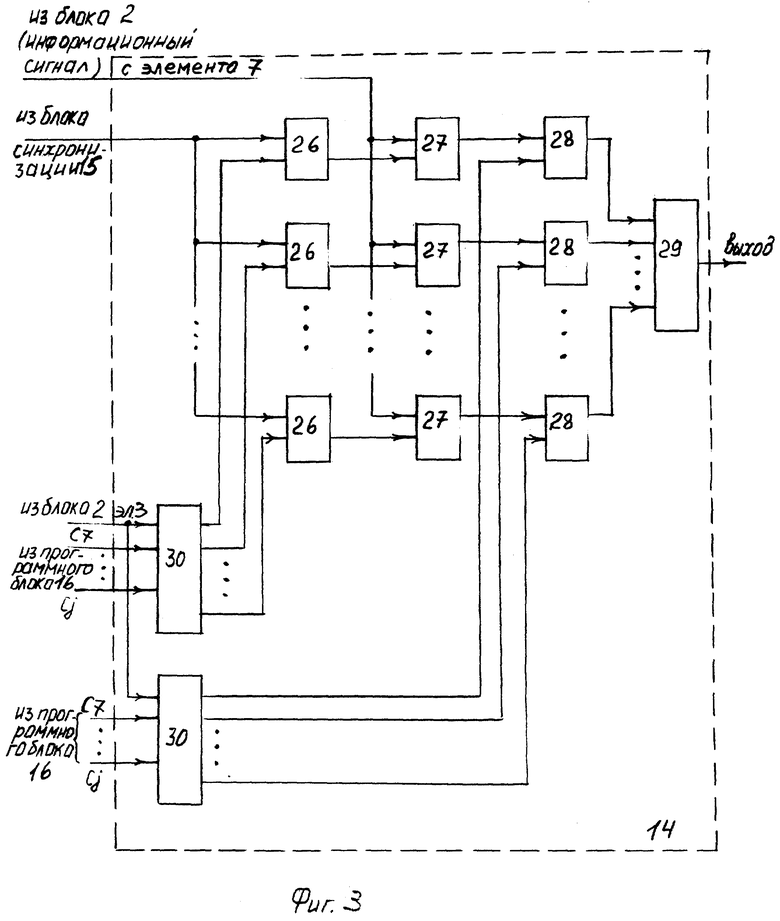

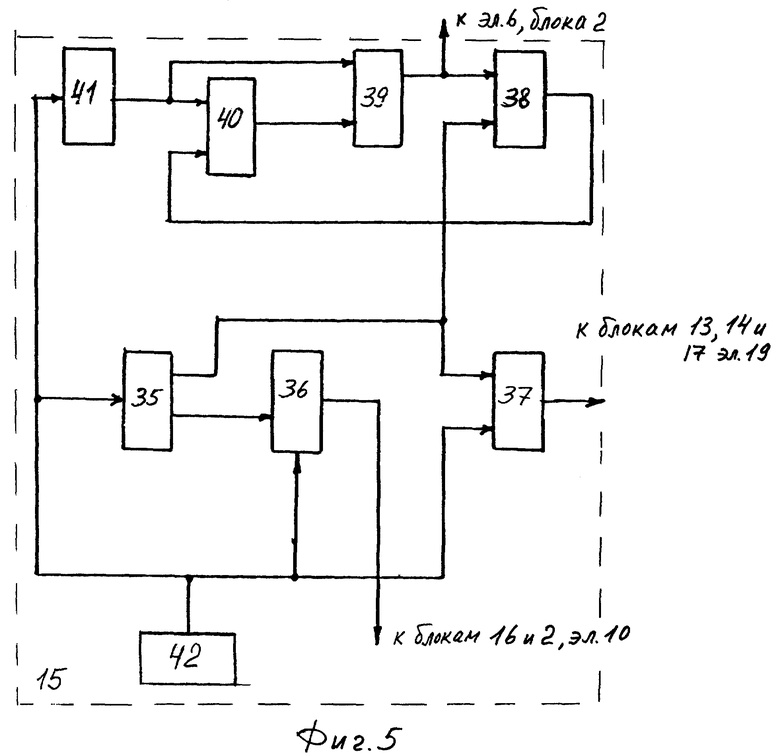

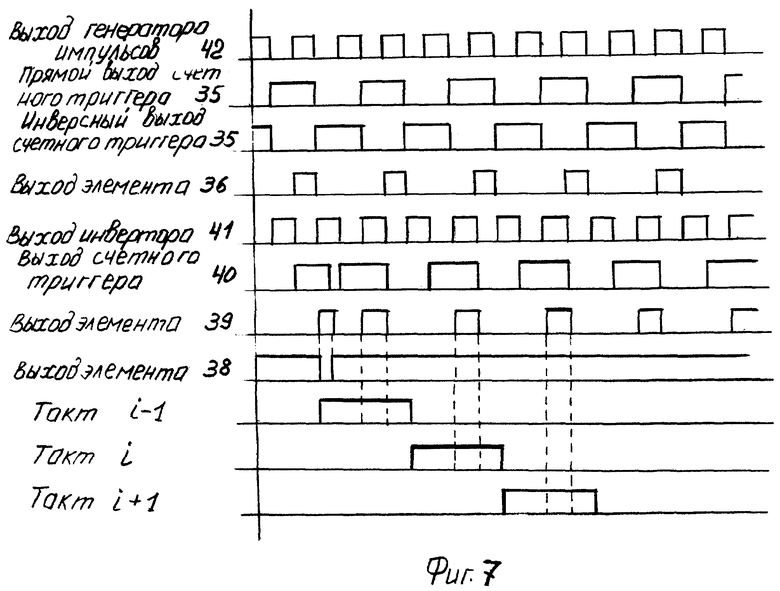

Блок синхронизации 15 известной конструкции /фиг. 5/ содержит первый счетный триггер 35, подключенный прямым выходом к элементу И 36, а инверсным выходом к первым входам элементов И 37 и И 38, второй вход последнего подключен к выходу элемента И 39, входы которого связаны с прямым выходом второго счетного триггера 40 и с выходом инвертора 41, вход которого вместе с входом триггера 35 подключены к генератору прямоугольных импульсов 42. Работа блока 15 поясняется диаграммами на фиг. 6 и фиг. 7.

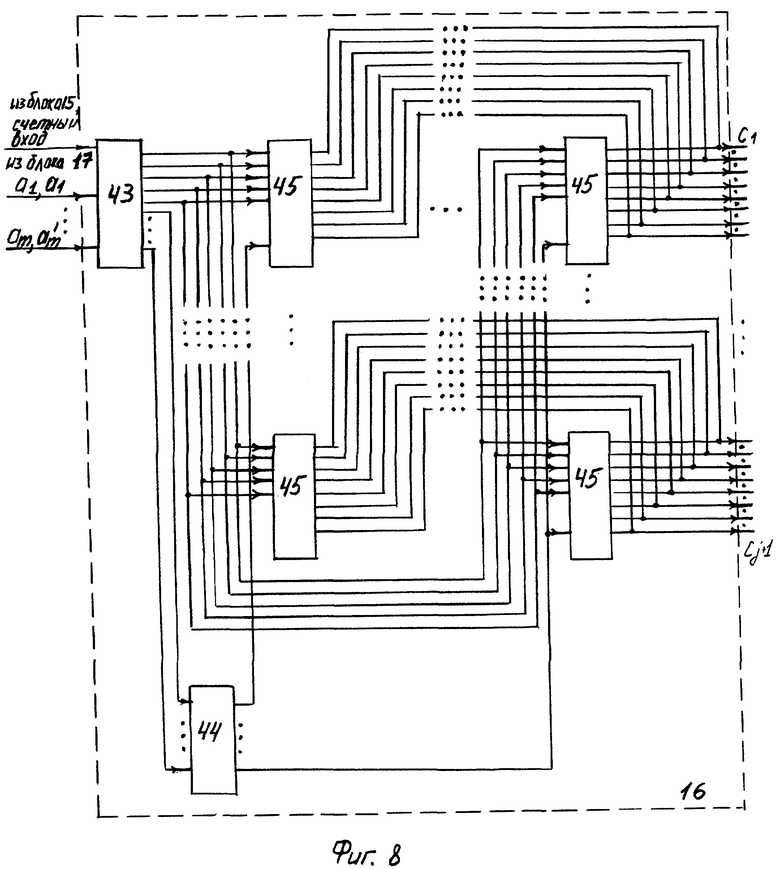

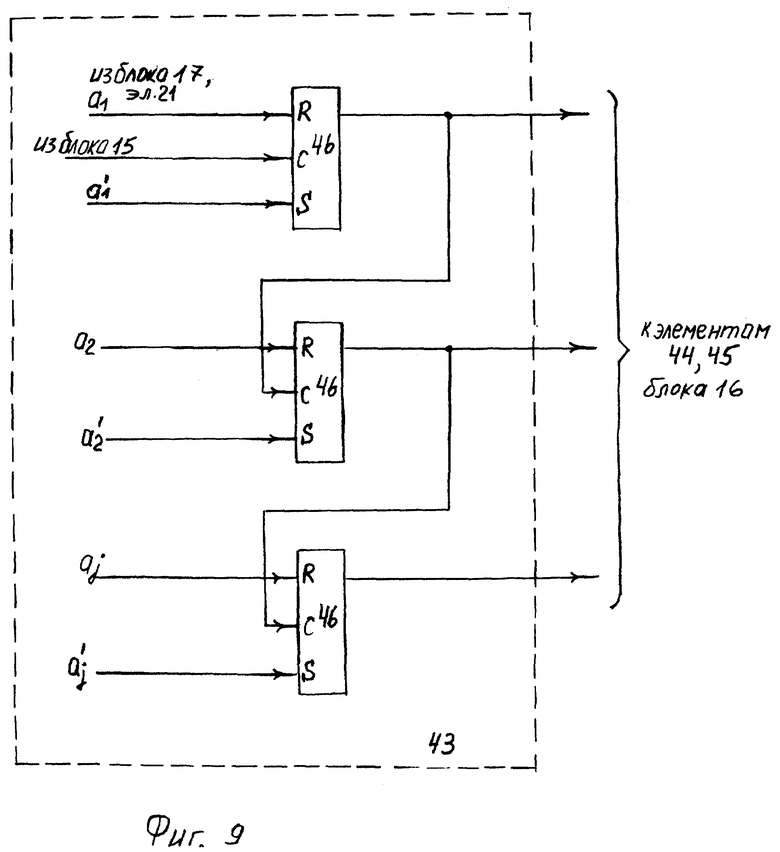

Программный блок 16 известной конструкции /фиг. 8/ состоит из счетчика импульсов с установочными входами R и S 43, на счетный вход которого поступают импульсы из блока 15, а на установочные входы подаются сигналы a1... am и a'1...am', которые при нулевом сигнале на выходе элемента И 10 блока 2 и тем самым на командном входе ЭК2 21 блока 17 все равны "0" или "1" в зависимости от типа счетных триггеров, обеспечивают работу этих триггеров в счетном режиме, если же на командном входе ЭК2 21 присутствует единичный сигнал, то прямые a1...am и инверсные a'1...a'm сигналы ранее записанных в ЯП20 значений C3...Cj поступят с выходов ячеек памяти 20 на установочные R и S входы счетных триггеров, устанавливая их во внеочередное состояние. Дешифратор 44 распределяет импульсы по элементам постоянной памяти 45 /например, серии ПЗУ 155РЕ3/, на которые записываются программы работы всего устройства. Подробнее схема счетчика 43 представлена на фиг. 9, где индексом 46 обозначены счетные триггеры с установочными R и S входами.

Заметим, что запись информации, поступающей на вход ячейки памяти 7 из элемента ИЛИ 8, происходит по заднему фронту импульса, приходящему с выхода элемента И 6 на управляющий вход ячейки памяти 7.

Отметим, что каждая переменная из всех рассматриваемых нами может принимать значение либо логического "0", либо логической "1".

Примем, что при значении C'3=1, C'4=0 и C'5=0 активизируется верхний выход дешифратора 3 блока 2 и в соответствии с текущим адресом C7...Cj произойдет подача одного из сигналов X1...Xn с выхода входного блока 1 на верхний /первый/ вход элемента 4 и далее на вход элемента 5, при C'3=0, C'4= 1 и C'5=0 активизируется второй выход дешифратора 3 и переменная из ячейки памяти с адресом C7...Cj БОП 13 через элемент 4 поступит на вход элемента 5. При C'3=0, C'4=0 и C'5=1 активизируется третий выход дешифратора 3 и на вход выходного блока 13 поступит команда на запись информации по адресу C7...Cj с выхода ячейки памяти 7 блока 2. При C'3=1, C'4=0 и C'5=1 активизируется четвертый /нижний/ выход дешифратора и на вход БОП 13 поступит команда на запись информации с выхода ячейки 7.

Принцип действия предлагаемого устройства рассмотрим на двух примерах. Отметим, что вычисление логических функций в базисе И, ИЛИ, НЕ в предлагаемом устройстве реализуется при C'6=0 аналогично прототипу.

В первом примере рассмотрим вычисление функции ИСКЛЮЧАЮЩЕЕ ИЛИ от двух переменных X1 и X'2:

X1⊕X′2. (1)

При вычислении функции /1/ в устройстве, принятом за прототип, потребуется 9 тактов, что легко проверить, реализуя функцию /1/ в предлагаемом устройстве при C'6=0. Представим функцию /1/ в виде  Допустим, что X'2 была ранее записана в блок БОП 13.

Допустим, что X'2 была ранее записана в блок БОП 13.

На первом такте ячейка памяти 7 устанавливается в единичное состояние при C1= 1, C2=1, C'3...C'6=0, на втором такте при C1=1, C2=0, C'3=1 C'4... C'6= 0 и соответствующих значениях C7...Cj переменная X1 поступает на вход элемента 5 и, если X1=0, то логический нуль записывается в ячейку 7, при X1= 1 значение ячейки 7 не меняется. На третьем такте, если C1=0, C2=0, C'3=0, C'4=1, C'5=0 и C'6=0, значение X'2 в соответствии с C7...Cj из БОП 14 поступает на вход элемента 5 и при X'2=1 произойдет запись "0" в ячейку 7, а при X'2= 0 значение ячейки 7 сохранится. Произойдет вычисление функции  с результатом в ячейке памяти 7. На четвертом такте под действием команд C'3= 1, C'4=0, C'5=1 и C'6=0 во второй четверти такта произойдет запись результата вычисления функции

с результатом в ячейке памяти 7. На четвертом такте под действием команд C'3= 1, C'4=0, C'5=1 и C'6=0 во второй четверти такта произойдет запись результата вычисления функции  в БОП 14, а в третьей четверти такта при C1=1, C2= 1 в ячейку 7 запишется логическая "1". На пятом, шестом и седьмом тактах произойдут вышеописанные процессы по вычислению второй конъюнкции функции /1/, т.е.

в БОП 14, а в третьей четверти такта при C1=1, C2= 1 в ячейку 7 запишется логическая "1". На пятом, шестом и седьмом тактах произойдут вышеописанные процессы по вычислению второй конъюнкции функции /1/, т.е.  и записи результата в БОП 14, на седьмом же такте в третьей четверти логический "0" запишется в ячейку 7. На восьмом и девятом тактах при C1=0, C2=1, C'3=0, C'4=1, C'5=0 и C'6=0 в соответствующих адресах C7... Cj произойдет вычисление всей функции /1/ и результат вычисления будет находиться в ячейке 7. При необходимости этот результат запишется в выходной блок 13 по командам C'3=0, C'4=0, C'5=1 и соответствующем адресе C7..Cj на десятом такте.

и записи результата в БОП 14, на седьмом же такте в третьей четверти логический "0" запишется в ячейку 7. На восьмом и девятом тактах при C1=0, C2=1, C'3=0, C'4=1, C'5=0 и C'6=0 в соответствующих адресах C7... Cj произойдет вычисление всей функции /1/ и результат вычисления будет находиться в ячейке 7. При необходимости этот результат запишется в выходной блок 13 по командам C'3=0, C'4=0, C'5=1 и соответствующем адресе C7..Cj на десятом такте.

Вычислим функцию /1/ с использованием введенных в блок 2 логических элементов и связей. На первом такте описанным выше способом запишем логический "0" в ячейку памяти 7 блока 2. На втором такте при C1=0, C'3=1, C'4=0, C'5= 0, C'6=1 переменная X1 из блока 1 поступит на вход элемента 5 и, если X1=0, то на выходе элементов 5 и 6 будут "0" и состояние ячейки 7 не изменится, т. е. на ее инверсном выходе имеется логическая "1". Если же X1=1, то на выходе 5 также логическая "1", которая вместе с импульсом с выхода блока 15 создаст на выходе элемента 6 единичный импульс, переводящий ячейку памяти 7 в единичное состояние. На третьем такте C1=0, C'3=0, C'4=1, C'5=0, C'6=1 и при соответствующем адресе C7...Cj значение X'2 из блока БОП14 поступит на вход элемента 5 и, если X'2=0, то состояние ячейки памяти 7 не изменится, при X'2= 1 состояние ячейки памяти 7 изменится на противоположное, т.е. ячейка памяти 7 при C'6=1 работает в режиме счетного триггера. Таким образом, вышеописанный процесс позволяет вычислять широко распространенную функцию ИСКЛЮЧАЮЩЕЕ ИЛИ за меньшее количество тактов, чем в прототипе, т.к. уже на третьем такте мы имеем результат вычисления функции /1/ в ячейке памяти 7. Действительно, при любых одинаковых значениях X1 и X'2 в ячейке 7 имеет место логический нуль, а при различных значениях X1 и X'2 в функции /1/ в ячейке 7 находится логическая единица, что является результатом вычисления функции /1/. На четвертом такте результат может быть отправлен в БОП14.

Рассмотрим второй пример. До этого примера принималось, что Cj+=0.

Допустим, как это часто требуется в системах управления, необходимо сравнить два двоичных кода на их равенство и допустим процесс сравнения кодов организован так, что, если в его конце имеем логический "0", то коды равны, а если "1", то не равны. Например, сравниваются первый и второй коды 101. . . и 100..., поступающие на входы X1...Xn блока 1. Принцип сравнения основан на поразрядном вычислении функции /1/ от двух соответствующих разрядов представленных кодов и далее результаты этих вычислений реализуют с помощью функции ИЛИ и, если в результате получается "0", то коды равны.

Из первого примера следует, что на вычисление функции /1/ с учетом записи результата в БОП14 требуется четыре такта. Поэтому, чтобы сравнить три разряда каждого кода, потребуется 12 тактов и для реализации функции ИЛИ потребуется еще 4 такта, всего 16 тактов.

Приведем сравнение первых трех разрядов представленных кодов с учетом введенного блока 17. На первом такте при C1=1, C2=0, C'6=0 и Cj+1=1 в ЯП 20 из блока 16 запишется двоичный номер такта, на котором готовый результат сравнения двух кодов отправится в БОП14 или блок 13 и в ячейку памяти 7 запишется логический "0". На втором такте при C1=0, C2=0, C'3=1, C'5=0, C'6=1, Cj+1= 0 с учетом кода адреса C7...Cj значение первого разряда первого кода с выхода блока 1 поступает через элемент 5 на вход элемента И 6, на другой вход которого приходит импульс с выхода блока 15 и сигнал с выхода элемента И 6 меняет состояние ячейки 7 с "0" в "1". На третьем такте при C1=0, C2=1, C'3= 1, C'4=0, C'5=0, C'6=1, Cj+1=0 и соответствующих значениях C7...Cj первый разряд второго кода через элементы 5 и 6 меняет информацию в ячейке 7 на противоположную. На четвертом такте при C1, C2, C'4, C'5, Cj+1, равных "0", и C'3, C'6, равных "1", и соответствующих C7...Cj второй разряд первого кода через элементы 5 и 6 поступит на вход ячейки 7, не меняя ее состояния. На пятом такте при C1, C'4, C'5, равных "0", и C2, C'3, C'6, равных "1", и соответствующих C7. . .Cj второй разряд второго кода через элементы 5 и 6 поступит на вход ячейки 7, не меняя ее состояния. На шестом такте под действием команд C1, C2, C'4, C'5, Cj+1, равных "0", и C'3, C'6, равных "1", при соответствующих адресах C7...Cj третий разряд первого кода через элементы 5 и 6 поступит на вход ячейки 7 и изменит ее состояние на противоположное /единичное/. На седьмом такте при C1=0, C2=1, C'3=1, C'4=0, C'5=0, C'6=1, Cj+1= 0 из блока 1 по адресу C7...Cj считается третий разряд второго кода, который обеспечит на выходах элементов 5 и 6 логические "0" и состояние ячейки не изменится, т.е. на прямом выходе ячейки 7 присутствует "1". При этом, учитывая, что C2=1 и C'6=1, на выходе элемента И 10 и в четвертой четверти такта ЭК2 появится "1", ЭК2 21 откроется, передав с выхода ЯП20 записанные туда сигналы на первом такте на установочные входы счетных триггеров 46 программного блока 16, установив их в положение, отвечающее процессу передачи результата сравнения в блоки БОП 14 или 13. Итак, при первом же признаке неравенства кодов их сравнение прекращается и результат передается в блоки 13 и 14. При равенстве кодов вышеуказанное положение установилось бы после сравнения последних разрядов двух кодов.

Таким образом, при сравнении трех разрядов двух кодов потребовалось семь тактов вместо шестнадцати при отсутствии блока 17. Более того, без блока 17 сравнение разрядов двух кодов продолжалось бы независимо от неравенства в каких-либо разрядах и закончилось бы после вычисления функции ИЛИ от всех переменных, образованных при реализации функции /1/ по соответствующим разрядам двух кодов.

Вышеприведенные примеры раскрывают принципы работы предлагаемого устройства и методы повышения его быстродействия за счет уменьшения числа тактов при вычислении представленных логических функций, что позволяет сократить время реакции систем управления на изменение входных сигналов, поступающих с объекта управления, и тем самым более точно вести технологические процессы в автоматическом режиме, повышая качество выпускаемого продукта.

Изобретение относится к средствам управления и может применяться при автоматизации в технологических процессах и производстве. Технический результат заключается в повышении быстродействия устройства за счет сокращения числа тактов при реализации логических операций и достигается за счет того, что в устройство в коммутационно-вычислительный блок введены управляемая ячейка памяти с прямым и инверсным выходами, второй, третий и четвертый элементы И, элементы ИЛИ и НЕ с соответствующими связями. Выход третьего элемента И соединен с введенным также блоком прерывания, содержащим элемент И, первый и второй электронные ключи и ячейки памяти с управляющими входами и соответствующими связями. 9 ил.

Программируемое устройство для логического управления электроприводами, электронными ключами и сигнализацией, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, коммутационно-вычислительный блок, содержащий трехвходовой дешифратор, элемент 2-2И-2ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и первый элемент И, первые входы элемента 2-2И-2ИЛИ соединены соответственно с первым и вторым выходами дешифратора, вторые входы элемента 2-2И-2ИЛИ подключены соответственно к выходу входного блока, соединенного первой и второй группами входов соответственно с группой информационных выходов объекта управления и с адресными шинами, соединенными с соответствующими выходами программного блока, и к выходу блока оперативной памяти, выход элемента 2-2И-2ИЛИ подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с соответствующим командным выходом программного блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом первого элемента И, подключенного вторым входом к первому выходу блока синхронизации, соединенного вторым выходом с первыми управляющими входами блока оперативной памяти и выходного блока, группы входов которых соединены с группой адресных выходов программного блока, а информационные входы объединены, третий выход блока синхронизации связан со счетным входом программного блока, третий и четвертый выходы дешифратора подключены к соответственно вторым управляющим входам блока оперативной памяти и выходного блока, отличающееся тем, что командно-вычислительный блок содержит управляемую ячейку памяти с прямым и инверсным выходами, второй, третий и четвертый элементы И, элемент ИЛИ и элемент НЕ, причем управляющий вход ячейки памяти соединен с выходом первого элемента И, ее информационный вход связан с выходом элемента ИЛИ, первый вход которого подключен к выходу второго элемента И, первый вход последнего соединен с первым входом третьего элемента И и с соответствующей командной шиной программного блока, а второй вход - с выходом элемента НЕ, вход которого связан со вторым входом третьего элемента И и первым входом четвертого элемента И, второй вход которого подключен к инверсному выходу ячейки памяти, а выход соединен с вторым входом элемента ИЛИ, прямой выход ячейки памяти связан с информационными входами выходного блока и блока оперативной памяти, а также с третьим входом третьего элемента И, четвертый вход которого подключен к третьему выходу блока синхронизации, а выход соединен с введенным блоком прерывания, содержащим элемент И, первый и второй электронные ключи, ячейки памяти с управляющими входами, причем первый электронный ключ связан информационными входами с четырьмя соответствующими командными шинами программного блока, управляющим входом - с еще одной командной шиной программного блока, а выходы первого электронного ключа подключены соответственно к трем входам дешифратора и входу элемента НЕ коммутационно-вычислительного блока, ячейки памяти соединены информационными входами с соответствующими командными и адресными шинами, идущими с выходов программного блока, а управляющими входами - с выходом элемента И, входы которого связаны соответственно с вторым выходом блока синхронизации и с управляющим входом первого электронного ключа, выходы ячеек памяти связаны с информационными входами второго электронного ключа, управляющий вход которого подключен к выходу третьего элемента И коммутационно-вычислительного блока, а выходы второго электронного ключа соединены с установочными входами программного блока.

| Устройство для дистанционного программного управления сигнализацией и электропроводными механизмами | 1990 |

|

SU1801223A3 |

| Устройство для дистанционного программного управления сигнализацией и электроприводными механизмами | 1989 |

|

SU1652964A1 |

| RU 94012061 A1, 27.02.1996 | |||

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2050576C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2047889C1 |

| Способ диагностики технического состояния трансмиссий горных машин с приводным двигателем | 1985 |

|

SU1271970A1 |

Авторы

Даты

2000-08-20—Публикация

1999-11-24—Подача