Изобретение относится к цифровым вычислительным машинам и может быть использовано для численного решения систем обыкновенных дифференциальных уравнений, для решения задач, которые можно свести к системам обыкновенных дифференциальных уравнений, а также для моделирования систем автоматического управления.

Известен цифровой дифференциальный анализатор 1, используюш ий для вычисления функциональных зав-исимостей преобразование их в систему дифференциальных уравнений.:

Наиболее близким к изобретению но технической сущности является цифровая интегрирующая машина 2, содержащая блок yviравления, первый выход которого соединен с управляющими входами блока ввода информации, блока памяти и блока вывода информации, выход блока ввода информации соединен со входом блока памяти, выход которого подключен ко входу блока управления.

Недостатком известного устройства является низкое быстродействие.

Целью изобретения является повыщенме быстродействия цифровой интегрирующей

машины.

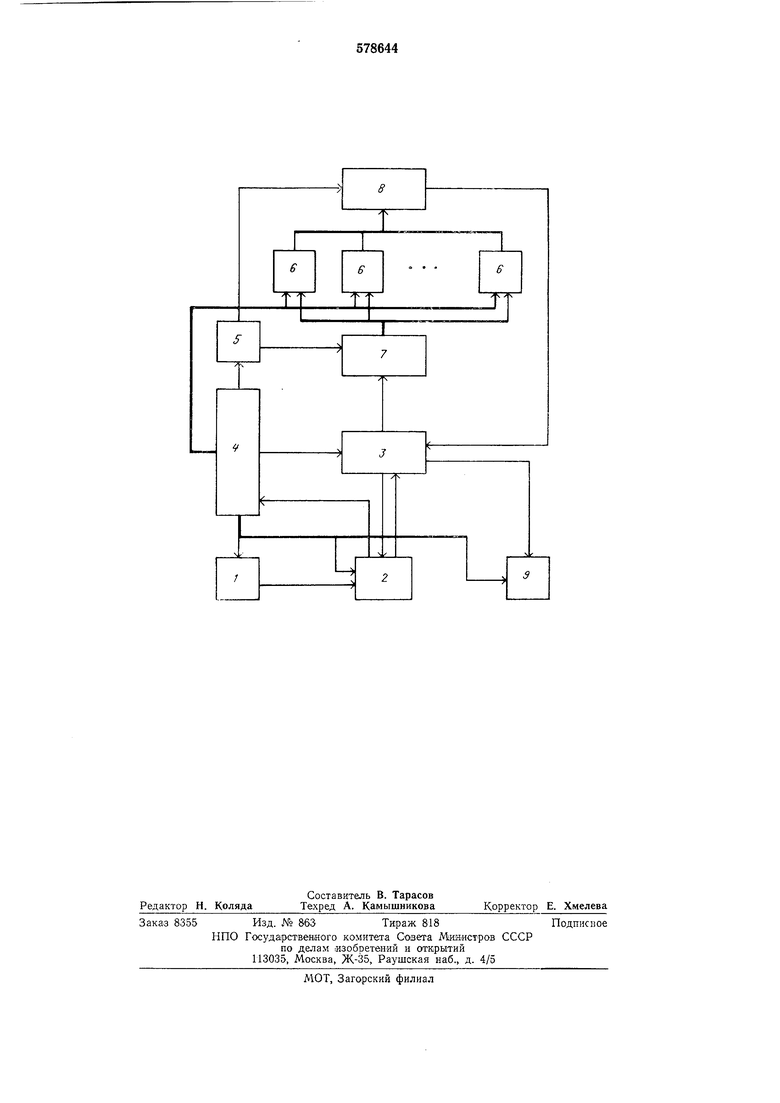

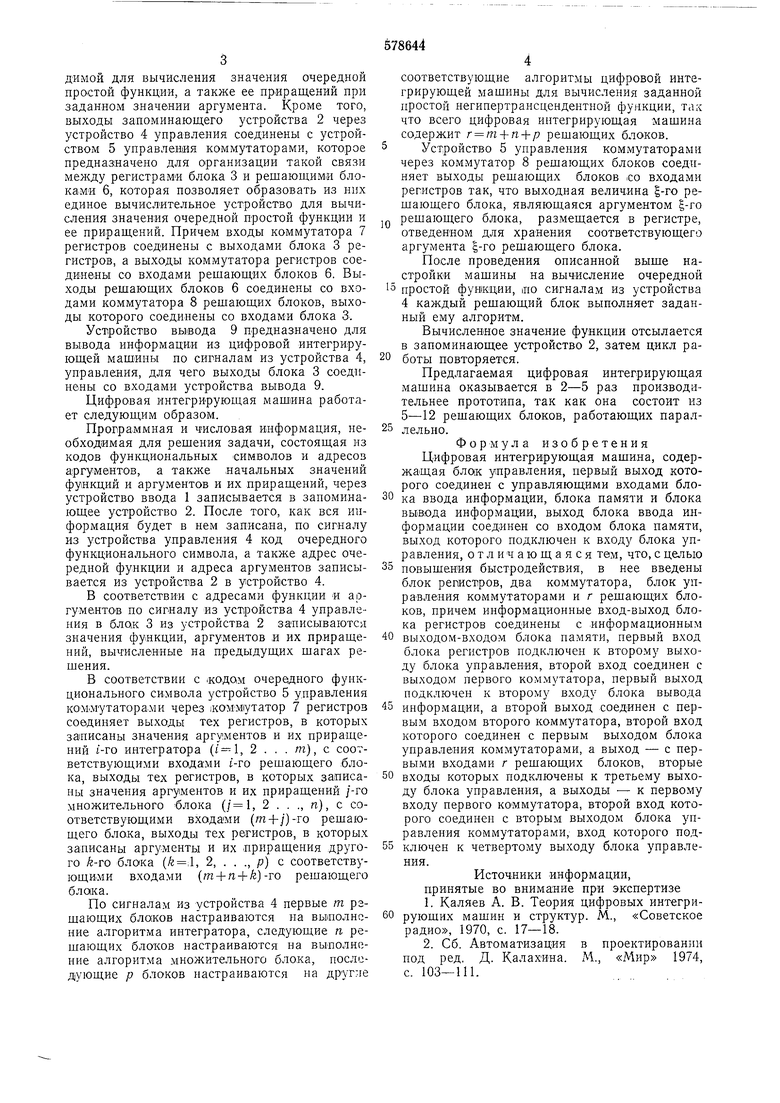

Поставленная цель достигается тем, что в известную мащнну введены блок регистров, два коммутатора, блок управления коммутаторами и г решающих блоков, причем информационные вход-выход блока регистров соединены с информационным входом-выходом блока памяти, первый вход блока регистров подключен ко второму выходу блока управления, второй вход соединен с выходом первого коммутатора, первь й выход подключен ко второму входу блока вывода информации, а второй выход соединен с первым входол второго коммутатора, второй вход которого соединен с первым выходом блока управления коммутаторами, а вы.ход - с первыми входами г решающих блоков, вторые входы которых подключены к третьему выходу блока управлеПИЯ, а выходы - к первому входу первого коммутатора, второй вход которого соединен со вторым выходом блока управления коммутаторами, вход которого подключен к четвертому выходу блока управления. На чертеже представлена структурная схема предлагаемой цифровой интегрирующей машины.

Устройство ввода 1 служит для ввода числовой и програм.мной информации. Выходы устройства ввода соединены со входами зачоминаюишго устройства 2 для передачи числовой и программной информации.

Выходы запоминающего устройства 2 соединены со входами блока 3 регистров для передачи в него числовой информации, необхоДИМОЙ для вычисления значения очередной простой функции, а также ее приращений при заданном значении аргумента. Кроме того, выходы запоминающего устройства 2 через устройство 4 управления соединены с устройством 5 управления коммутаторами, которое предназначено для организации такой связи меладу регистрами блока 3 и рещающими блоками 6, которая позволяет образовать из них единое вычислительное устройство для вычисления значения очередной простой функции и ее приращений. Причем входы коммутатора 7 регистров соединены с выходами блока 3 регистров, а выходы коммутатора регистров соединены со входами рещающих блоков 6. Выходы рещающих блоков 6 соединены со входами коммутатора 8 решающих блоков, выходы которого соединены со входами блока 3.

Устройство вывода 9 предназначено для вывода информации из цифровой интегрирующей машины по сигналам из устройства 4, управления, для чего выходы блока 3 соединеиы со входами устройства вывода 9.

Цифровая интегрирующая машина работает следующим образом.

Программная и числовая информация, необходимая для решения задачи, состоящая из кодов функциональных символов и адресов аргументов, а также начальных значений функций и аргументов и их приращений, через устройство ввода 1 записывается в запоминающее устройство 2. После того, как вся информация будет Б нем записана, по сигналу из устройства управления 4 код очередного функционального символа, а также адрес очередной функции и адреса аргументов записывается из устройства 2 в устройство 4.

В соответствии с адресами функции и аргументов по сигналу из уст1ройства 4 управления в блок 3 из устройства 2 записываются значения функции, аргументов и их приращений, вычисленные на предыдущих шагах решения.

В соответствии с .кодом очере дного функционального символа устройство 5 управления ком.мутаторами через 1КОММ(утатор 7 регистров соединяет выходы тех регистров, в которых записаны значения аргументов и их приращений 1-го интегратора (i-, 2 ... т), с соответствующими входами t-ro решающего блока, выходы тех регистров, в которых записаны значения аргументов и их приращений /-го множительного блока (, 2 . . ., п), с соответствующими входа ми (m+i)-To решающего блока, выходы тех регистров, в которых записаны аргументы и их приращения другого k-ro блока (, 2, . . ., р) с соответствующими входами (m + n + k)-YO решающего блока.

По сигналам из устройства 4 первые т рэшающих блоков настраиваются на выполнение алгоритма интегратора, следующие п решающих блоков настраиваются на выполнение алгоритма множительного блока, последующие р блоков настраиваются на другие

соответствующие алгоритмы цифровой интегрирующей машины для вычисления заданной простой негипертрансцендентной функции, так что всего цифровая интегрирующая машина содержит г т + п + р решающих блоков.

Устройство 5 управления коммутаторами через коммутатор 8 рещающих блоков соединяет выходы решающих блоков со входами регистров так, что выходная величина g-ro решающего блока, являющаяся аргументом |-го

рещающего блока, размещается в регистре, отведенном для хранения соответствующего аргумента 1-го решающего блока.

После проведения описанной выше настройки мащины на вычисление очередной простой фувкции, |по сигналам из устройства 4 каждый решающий блок выполняет заданный ему алгоритм.

Вычисленное значение функции отсылается в запоминающее устройство 2, затем цикл работы повторяется.

Предлагаемая цифровая интегрирующая машина оказывается в 2-5 раз производительнее прототипа, так как она состоит из 5--12 решающих блоков, работающих параллельно.

Формула изобретения Цифровая интегрирующая машина, содержащая блак управления, первый выход которого соединен с управляющими входами блока ввода информации, блока памяти и блока вывода информации, выход блока ввода информации соединен со входом блока памяти, выход которого подключен к входу блока управления, отличающаяся тем, что, с целью

повышения быстродействия, в нее введены блок регистров, два коммутатора, блок управления коммутаторами и г решающих блоков, причем информационные вход-выход блока регистров соединены с информационным

выходом-входом блока памяти, первый вход блока регистров подключен к второму выходу блока управления, второй вход соединен с выходом первого коммутатора, первый выход подключен к второму входу блока вывода

информации, а второй выход соединен с первым входом второго коммутатора, второй вход которого соединен с первым выходом блока управления коммутаторами, а выход - с первыми входами г решающих блоков, вторые

входы которых подключены к третьему выходу блока управления, а выходы - к первому входу первого коммутатора, второй вход которого соединен с вторым выходом блока управления коммутаторами, вход которого подключен к четвертому выходу блока управления.

Источники информации, принятые во внимание при экспертизе

1.Каляев А. В. Теория цифровых интегрирующих машин и структур. М., «Советское

радио, 1970, с. 17-18.

2.Сб. Автоматизация в проектировании под ред. Д. Калахина. М., «Мир 1974, с. 103-111.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выфода данных цифровой интегрирующей структуры | 1974 |

|

SU506849A1 |

| Цифровая интегрирующая структура | 1974 |

|

SU674052A1 |

| Элемент однородной вычислительной среды | 1974 |

|

SU596940A1 |

| Устройство для вычисления полиномов | 1978 |

|

SU792263A1 |

| Цифровое устройство для воспроизве-дЕНия фуНКций | 1979 |

|

SU809126A1 |

| Цифровая интегрирующая структура | 1978 |

|

SU680001A1 |

| Устройство для решения дифференциальных уравнений | 1979 |

|

SU1023340A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ—ЦИФРА | 1973 |

|

SU388361A1 |

| Цифровая интегрирующая структура | 1973 |

|

SU488205A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU942034A1 |

Авторы

Даты

1977-10-30—Публикация

1974-11-21—Подача