(54) ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ

ФУНКЦИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор функции | 1977 |

|

SU711556A1 |

| Функциональный преобразователь | 1983 |

|

SU1126968A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| ЦИФРО-АНАЛОГОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УПРАВЛЯЮЩЕЕ | 1973 |

|

SU386409A1 |

| Устройство для логарифмирования двоичных чисел | 1980 |

|

SU924705A1 |

| Функциональный преобразователь | 1980 |

|

SU962971A1 |

| Устройство для вычисления тригонометрических функций тангенса и котангенса | 1980 |

|

SU907545A1 |

| Цифровой функциональный генератор | 1985 |

|

SU1285452A1 |

| Устройство для логарифмирования двоичных чисел | 1984 |

|

SU1241237A1 |

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

1

Изобретение откосится к вычислительной технике и может быть использовано для аппаратурной реализации функций в специализированных и универсальных быстродействующих цифровых вычислительных машинах.

Известно устройство, содержащее регистры старщих и младщих разрядов аргумента, блоки памяти, блоки умножения и сумматор 1.

Недостаток известного устройства сос тоит в ограниченной точности.

Наиболее близким к предлагаемому является устройство, содержащее регистры старщих и младщих разрядов аргумента, два коммутатора, первый буферный регистр, сумматор, регистр результата, первый, второй и третий блоки памяти, адресные входы которых подключены к выходу регистра старщих разрядов аргумента, а выходы первого, второго блоков памяти и первого буферного регистра соединены соответственно с первым, вторым и третьим входами первого коммутатора, выход которого подключен к.первому входу сумматора, выход которого подключен ко входам регистра результата и первого буферного регистра, выход третьего

блока памяти соединен с первым входом второго коммутатора, а управляющие входы первого и второго коммутаторов подключены соответственно к первому и второму выходам блока управления 2.

Однако такое устройство характеризуется возможностью применения лищь для малоразрядных ЦВМ.

Цель изобретения - расщирение класса рещаемых задач за счет возможности применения с ЦВМ средней и больщой разрядности.

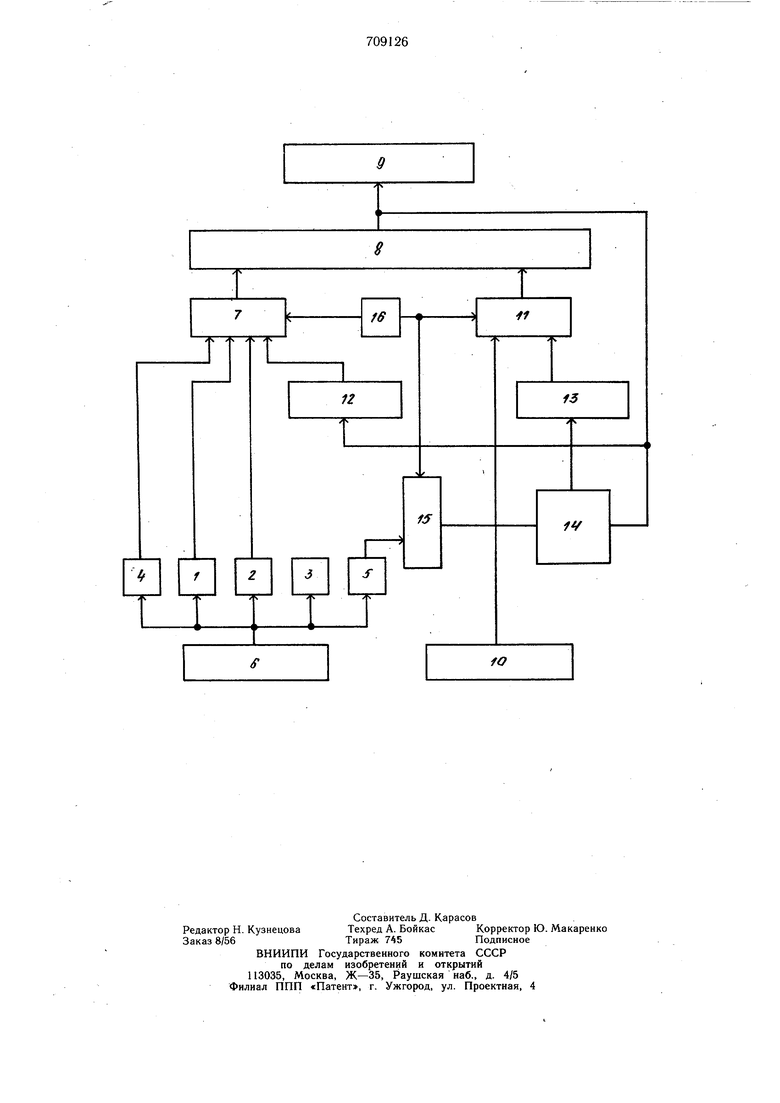

Поставленная цель достигается тем, что в устройство введены четвертый и пятый блоки памяти, второй буферный регистр, третий коммутатор и блок деления, вход делимого которого соединен с выходом второго коммутатора, а выход делителя подключен к выходу сумматора, выход блока деления через второй буферный регистр соединен с первым входом третьего коммутатора, второй вход которого соединен с выходом регистра младщих разрядов аргумента, выход третьего коммутатора подключен ко второму входу сумматора, адресные входы четвертого и пятого блоков памяти соединены с выходом регистра старщих разрядов аргумента, а их выходы соответственно с четвертым входом первого и вторым входом второго коммутаторов, . управляющий вход третьего коммутатора подключен ко второму выходу блока управления. Вычисление значений функции в предлагаемом устройстве производится на основе следующих соотнощений. Пусть задана функция F(x), О 6 1, удовлетворяющая условию /F(x)/ 1, значения аргумента X представляются п разрядным двоичным кодом, а значения функции Y F(X) тре буется находить с п верными двоичными циф рами после запятой. Фиксируем значение параметра К, 1 К п, и разбиваем аргумент X О, Х, X2,...Xrt, в сумму двух слагаемых Хо 0,Xi ..ХкО...О и ДХ 0,0...ОХ ..Хк; Х Хо+ АХ. Расчеты показывают, что значения заданной функции F(X) можно аппроксимировать выражением -«-a., где коэффициенты А(Хо), В(Хо), С(Хо), D(XO) и Е(Хо) зависят только от промежуточного аргумента Хо, но не зависят от ДХ и определяются следующим образом через вспомогательные функции p(Z), y(Z): (p(Z) ф57)-ф,(7) Фз(Z)(Z)- Ф2(2) )«(2:) Ф,(7)ф4(7)-фг(г)ф,(2)/ (Z)-Фг(Z)Ф,(Z)j; А(Хо) Фо(Хо)+ Oi(Xo)/F(Xo) + Фг(Хо)) ((Хо); В(Хо) )(Xo) -Фг(Хо) д)(Хо)У(Хв); Е(Х«) (((Хр) Ф1(Хо){Хо)+ Ф(Хо) р(Хо)/{Ф(Хо) У(Хо)) + + tpi(Xo) (|)(Xo)V(Xj} ; С(Хо) (Хо)-Е(Хо); D(XO) р(Хо)-С(Хо)Е(Хо); ф.(Z) ), где 1 0,5. Значение параметра К для получения верными всех двоичных разрядов результата п необходимо при этом взять из выражения К (п + 1 -f 1одгМ)/5, где М O.Z4 b ОС,2 CP3(Z) + ,(Z) Z) + q%(Z + l| ) (Z) 2}+ (Z) V Значения коэффициентов A(Xo), B(Xo)j C(Xo), D(Xo) и E(Xo) предварительно рассчитываются по указанным формам и запоминаются по соответствующим адресам блоков памяти предлагаемого устройства. На чертеже представлена блок-схема устройства. Цифровое устройство содержит блоки 1, 2, 3, 4 и 5 памяти, регистр 6 старщих разрядов аргумента, первый коммутатор 7, сумматор 8, регистр 9 результата, регистр 10 младших разрядов аргумента, третий коммутатор П, первый буферный регистр 12, второй буферный регистр 13, блок 14 деления, второй коммутатор 15, блок 16 управления. Предлагаемое устройство работает следующим образом. В первом такте по адресу Хо, передаваемому с выхода регистра 2 старщих разрядов а)гумента на входы блоков 1, 2, 3, 4 и 5 памяти, на выходах блоков памяти появляются соответственно значения коэффициентов Е(Хо), С(Хо), D(Xa), А(Хо) и В(Хо). Значение коэффициента D(Xo) через первый вход второго коммутатора 15, подключаемого в этом такте блоком 16 управления, передается на вход делимого блока 14 деления. Одновременно с этим на вход делителя блока 14 деления с выхода многоразрядного комбинационного сумматора 8 поступает Е(ХО) -t- АХ,, образованное в результате подачи на этот сумматор через первый вход первого коммутатора 7 значения коэффициента Е(Хо) с выхода блока 1 памяти и подачи на другой вход сумматора через первый вход третьего коммутатора 11 значения приращения АХ, хранящегося на регистре 10 младщих разрядов аргумента. В результате выполнения первого такта на выходе блока деления образуется значение D(Xo)(Xo) + ДХ, запоминаемое на втором буферном регистре 13. Во втором такте работы значение промежуточного результата D(Xo)(Xo) + ДХ через второй вход третьего коммутатора со второго буферного регистра 13 и значение коэффициента С(Хо) через второй вход первого коммутатора с выхода блока памяти поступают на многоразрядный комбинацион ный сумматор, образуя результат Р С(Хо + D (Хв)(Хо) + ЛХ, запоминаемый на первом буферном регистре 12. В третьем такте работы устройства на вход делимого блока 14 деления через второй вход второго коммутатора 15 с выхода блокаЗ памяти поступает значение В (Хо), а на вход делителя с выхода многоразрядного комбинационного сумматора 8 - значение С(Хо) + + D((Xo) + АХ, образуемое путем сложения на последнем значении приращения ДХ, передаваемого через первый вход третьего коммутатора 11, и поступающего через третий вход первого коммутатора с первого буферного регистра 12 значения Р: Результат деления (Xo)(Xo) + AX + D(Xo)l/ (Хо) -f- запоминается на втором буферном регистре 13. В последнем, четвертом, такте работы устройства на многоразрядном комбинационном сумматоре 8 происходит сложение значения коэффициента А (Хо), поступающего через четвертый вход первого коммутатора с выхода блока 4 памяти, и промежуточного результата, поступающего через второй вход третьего коммутатора 11 с выхода второго буферного регистра 13, что дает согласно формуле (1) искомое значение функции, запоминаемое на регистре 9 результата. Таким образом, предлагаемое устройство расширяет область применения аппаратурной реализации ряда функций, в частности элементарных, на ЦВМ средней и большой разрядности. Формула изобретения Цифровое устройство для воспроизведения функций, содержащее регистры старших и младших разрядов аргумента, два

/, коммутатора, первый буферный регистр, сумматор, регистр результата и три блока памяти, адресные входы которых подключены к выходу регистра старших разр.чдов аргумента, а выходы первого и второго блоков памяти и первого буферного регистра соединены соответственно с первым, вторым, и третьим входами первого коммутатора, выход которого подключен к первому входу сумматора, выход которого подключен ко входам регистра результата и первого буферного регистра, выход третьего блока памяти соединен с первы.м входом второго коммутатора, а управляющие входы первого и второго коммутаторов подключены соответственно к первому и второму выходам блока управления, отличающееся тем, что, с целью расширения класса решаемых задач за счет возможности применения с ЦВМ средней и большой разрядности, в него дополнительно введены четвертый и пятый блоки памяти, второй буферный регистр, третий коммутатор и блок деления, вход делимого которого соединен с выходом второго коммутатора, а выход делителя подключен к выходу сумматора, выход блока деления через второй буферный регистр соединен с первым входом третьего коммутатора, второй вход которого соединен с выходом регистра младших разрядов аргумента, выход третьего коммутатора подключен ко второму входу сумматора, адресные входы четвертого и пятого блоков памяти соединены с выходом регистра старших разрядов аргумента, а их выходы соответственно с четвертым входом первого и вторым входом второго коммутаторов, управляющий вход третьего коммутатора подключен ко второму выходу блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 575647, кл. G 06 F 7/38, 1977. 2.Авторское свидетельство СССР по завке № 2415788/18-24, кл. G 06 F 1/02, 0.04.77 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-03-07—Подача