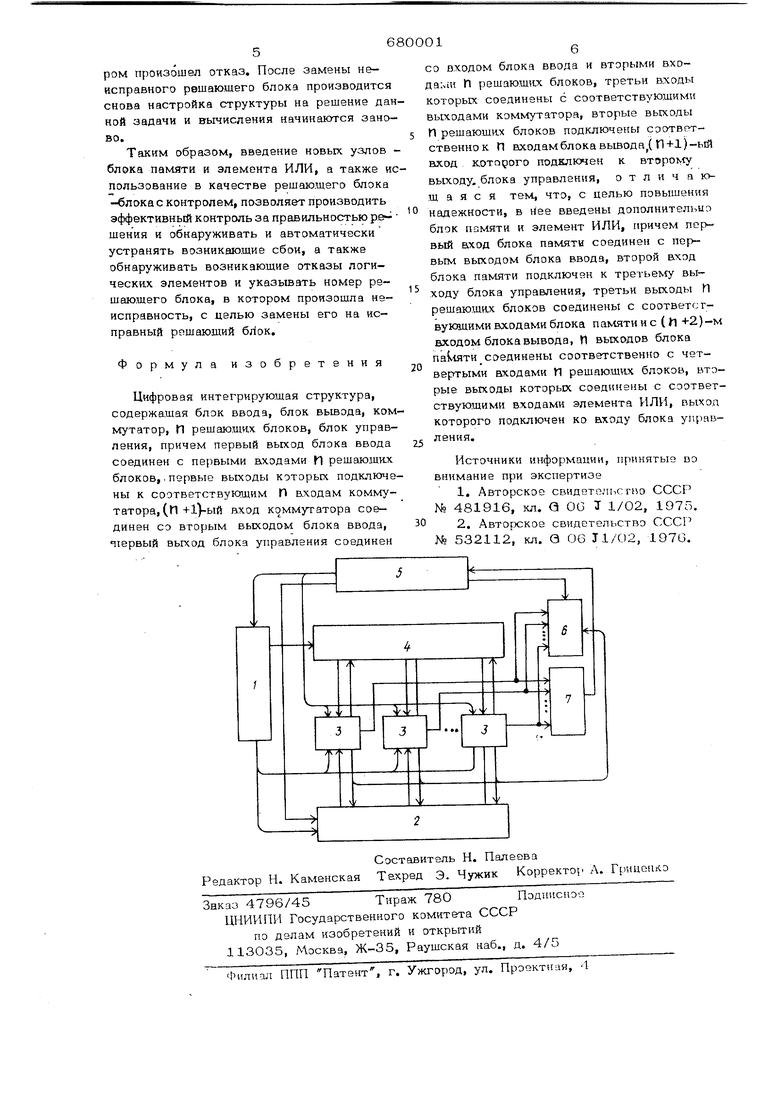

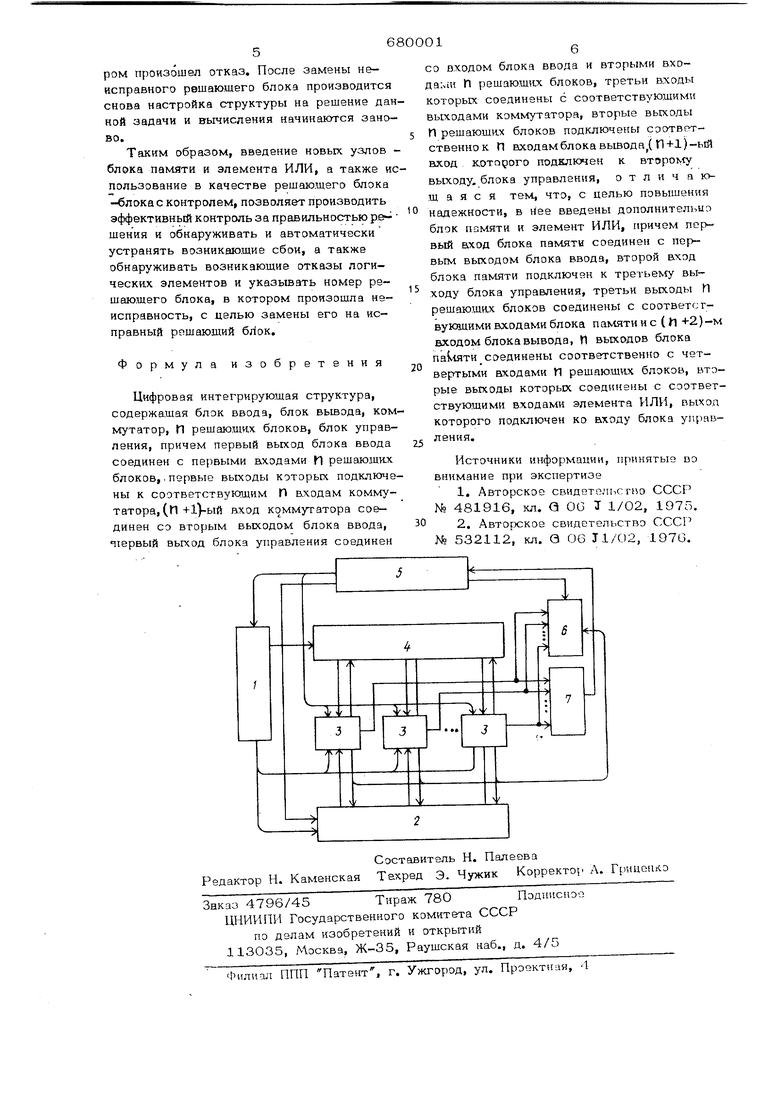

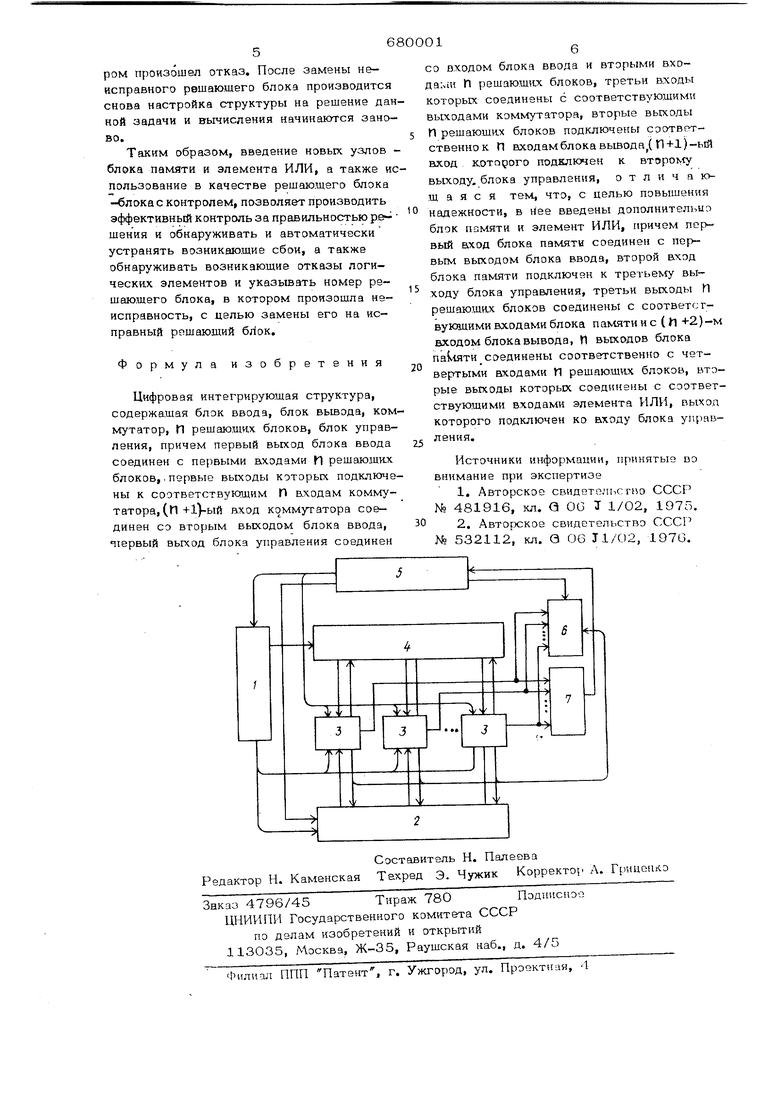

(54) ЦИФРОВАЯ ИНТЕГРИРУЮЩАЯ СТРУКТУРА чены соответственно к -Ц входам блока вы вода, (И+1)-ьй нхо-д которого подключен к второму выходу блока управления, введены дополнительно блок памяти и элемен ИЛИ, причем первь1й аход. блока памяти соединен с первым выходом блока ввода, второй в.ход блока памяти подкл очен к третьему выходу блока управления, треть выходы h решающих блоков сюединены с соответствующими входами блока памяти и с ( И +2 -м входом блока вьюода, Я выходов блока памяти соединены соответственно с четвертыми входами ,tl решаюШИ.Х блоков, вторые выходы которьк соединены с соответствующими входами элемента ИЛИ, выход которого подключен ко входу блока управления. Блок-схема предлагаемой цифровой интегрируюшей структуры представлена на чертеже, В состав интегрирующей структурьгах дят блок 1 ввода, блок 2 памяти, решающие блоки 3, коммутатор 4, блок 5 управления, блок 6 вывода, элемент ИЛИ 7, Рещйниэ задач на структуре осуществляется приближенными методами численного интегрирования. Результаты решения получаются и виде числовых значений искомых величин через равные интервалы времени, определяемые заранее выбранным шагом решения. На входы решающих блоков информации подаётся в виде приращения подинтегральной функции и переменной интегрирования. Решающий блок оперирует с одноразрядными приращениями, выполняет операции численного интегрирования, суммирования приращений, функции знака и ограничения Для обеспечения достоверности функционирования в нем осуществляется контроль выполнения арифметическах операций и передачи информации в регистры, и при обнаружении сбоя решающий блок вьщает сигнал сбоя на выходную управляющую шину. Перед настройкой структуры на решени задачи и выполнением процесса решения производится установка в нулевое положение блоков 1, 2, 3,6 и коммутатора 4 подачей соответствующих сигналов с блока 5. Настройка структуры на решение задачи может производиться как вручную с помохцьЮ блока 5, так и автоматически с помо.щью блока 1. Решение задачи осу.ществляется следующим образом, В блоке 5 задается не- обходимое количество итераций, в течение оторых вычисляется точка решения, т. е. адается шаг решения, а также задается необходимое число точек решения. Затем блок 5 вырабатывает команду пуска, по Которой вырабатывается сигнал, разрешающий решение задачи. В процессе решения задачи обмен информацией между решающими блоками 3 происходит через соответствующие элементы коммутатора 4, На каждой итерации в решающих блоках 3 наряду с вычислениями производится контроль за правильностью выполнения арифметических операций и передачи информации в регистрах, а вычисленные новые значения подынтегральной функции и неквантованного приращения интеграла, наряду с запоминанием ах в регистрах решающих блоков 3, поступают в соответствующие ячейки блока 2, который хранит также значения подынтегральгной функции и неквантованного приращения интеграла, вычисленные в предьщущей итерации (для первой итерации - это будут начальныеданные). В случае, если в каком то решающем блоке 3 происходит сбой вычислений, то этот блок вьщает на свой управляющий выход сигнал сбоя, которьй через элемент ИЛИ 7 поступает в блок 5. Блок 5 вьфабатывает сигнал останова решения и одновременно сигнал считывания информации, который поступает в блок 2. По этому сигналу из ячеек блока 2 в соответствующие решающие блоки 3 записьшаются значения подынтегральной функции и некванто- ванного приращения интеграла предыдущего шага решения. По окончанию сигнала считывания блок 5 вырабатывает сигнал, разрешающий решение, и вычисления возобновляются с той итерации, на которой произошел сбой. После отработки заданного количества итераций блок 5 вырабатывает сигнал останова, который поступает в блок 6 подготавливая его к работе. При наличии приэ нака печати в коде операций информация из решающего блока 3 по второму выходу поступает в блок 6 и происходит печать точки решения, после чего решение продолжается. После отработки необходимого количества точек решения, блок 5 вырабатывает сигнал окончания решения. Если же сбой на какой-либо итерации повторится три раза, то это классифицируется как отказ элемента, и блок 5 вырабатывает сигнал аварийного останова, по которому решение прекращается и в блок 6 поступает сигнал, разрошпющий индикацию номера решаюшйго блока, п котором произошел отказ. После замены неисправного решаюшего блока производится снова настройка структуры на решение да ной задачи и вычисления начинаются зано во. Таким образом, введение новых узлов блока памяти и элемента ИЛИ, а также и пользование в качестве решающего блока -блока с контролем, позволяет производить эффективньШ контроль за правильностью решения и обнаруживать и автоматически устранять возникающие сбои, а также обнаруживать возникающие отказы логических элементов и указывать номер решаюшего блока, в котором произошла неисправность, с целью замены его на исправный решающий блок. Формула изобретения Цифровая интегрирующая структура, содержащая блок ввода, блок вьшода, ком мутатор, И решающих блоков, блок управления, причем первый выход блока ввода соединен с первыми аходами П решающих блоков,. первые выходы которых подключе ны к соответствукщдим П входам коммутатора, (М+1)-ый нход коммутатора соединен со вторым выходом блока ввода, «первый выход блока управления соединен со в.ходом блока ввода и вторыми входа:ч1И П решающих, блоков, третьи входы которых соединены с соответствующими выходами коммутатора, вторые выходы П решающих блоков подключены СООТВЕГГственнок П входам блока вывода( П+1)-ый вход которого подключен к BTOpoKty выходу, блока управления, отличающаяся тем, что, с целью повышения надежности, в viee введены дополнительно блок памяти и элемент ИЛИ, причем перьвый вход блока памяти соединен с первым выходом блока ввода, второй вход блока памяти подключен к третьему выходу блока управления, третьи выходы П решающях блоков соединены с соответсгвукшими входами блока памяти и с (Л +2)м входом блока вывода, П вькодов блока соединены соответственно с четвертыми входами Y решающих блоков, вторые выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого подключен ко входу блока управления. Источники информации, принятые вэ внимание при экспертизе 1.Авторское свндетольсгво СССР № 481916, кл. Q 00 J 1/О2, 1975. 2.Авторское свидетельство СССГ № 532112, кл. Q 06 11/02, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Интегрирующее устройство | 1978 |

|

SU781848A1 |

Авторы

Даты

1979-08-15—Публикация

1978-02-06—Подача