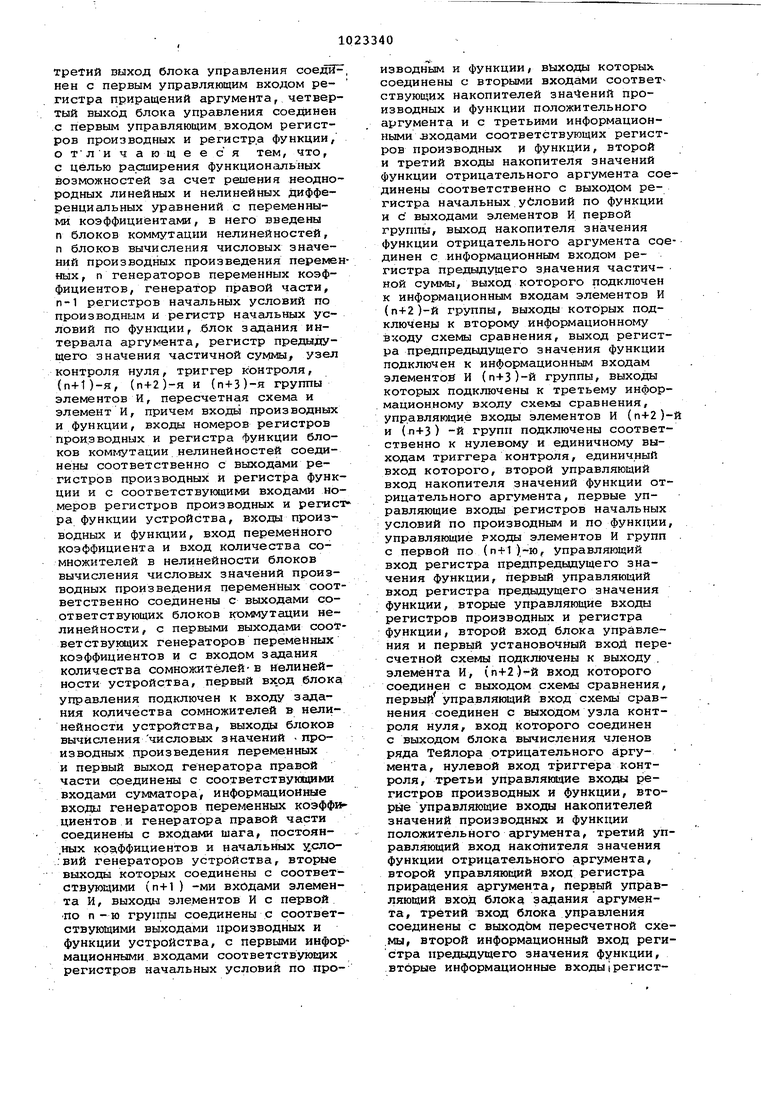

третий выход блока управления соедИ нен с первым управляющим входом ре гистра приращений аргумента, четвертый выход блока управления соединен с первым управляющим входом регистров производных и регистра функции, о тли ч а ющ е е с я тем, что, с целью расширения функцион-альных возможностей за счет решения неоднородных линейных и нелинейных дифференциальных уравнений с переменными коэффициентами, в него введены п блоков коммутации нелинейностей, п блоков вычисления числовых значений производных произведения переменных, п генераторов переменных коэффициентов, генератор правой части, п-1 регистров начальных условий по производным и регистр начальных условий по фунедии, блок задания интервала аргумента, регистр предыдущего значения частичной суммы, узел контроля нуля, триггер контроля, (п+1)-я, (п+2)-я и (п+3)-я группы элементов И, пересчетная схема и элемент И, причем входы производных и функции, входы номеров регистров производных и регистра Функции блоков коммутации нелинейностей соединены соответственно с выходами регистров производных и регистра функции и с соответствующими входами номеров регистров производных и регист ра функции устройства, входы производных и функции, вход переменного коэффициента и вход количества сомножителей в нелинейности блоков вычисления числовых значений производных произведения переменных соответственно соединены с выходами соответствующих блоков коммутации нелинейности, с первыми выходами соответствуияцих генераторов переменных коэффициентов и с входом задания количества сомножителей-в нелинейности устройства, первый блока управления подключен к входу задания количества сомножителей в нелинейности устройства, выходы блоков вычисления числовых значений производных произведения переменных и первый выход генератора правой части соединены с соответствующими входами сумматора, информационные входы генераторов переменных коэффициентов и генератора правой части соединены с входами шага, постоян,ных коэ,ффициентов и начальных у сло:вий генераторов устройства, вторые выходы которых соединены с соответствующими (п+1 ) -ми входами элемента И, выходы элементов И с первой по п-ю группы соединены с соответствующими выходами производных и функции устройства, с первыми информационными входами соответствующих регистров начальных условий по производным и функции, выходы которых соединены с вторыми входами соответ ствующих накопителей зна1ений производных и функции положительного аргумента и с третьими информационными а ходами соответствующих регистров производных и Функции, второй и третий входы накопителя значений функции отрицательного аргумента соединены соответственно с выходом регистра начальных условий по функции и с выходами элементов И первой группы, выход накопителя значения функции отрицательного аргумента соединен с информационным входом регистра предыдущего злачения частичной суммы, выход которого подключен к информационным входам элементов И {п+2)-й группы, выходы которых подключены к второму информационноглу входу схемы сравнения, выход регистра предпредыдущего значения функции подключен к информационным входам элементой И (п+3)-й группы, выходы которых подключены к третьему информационному входу схекИ сравнения, управляющие входы элементов И (п4-2)и (п+З) -и групп подключены соответственно к нулевому и единичному выходам триггера контроля, единичный вход которого, второй управляющий вход накопителя значений функции отрицательного аргумента, первые управляющие входы регистров начальных условий по производным и по функции управляющие рходы элементов И групп с первой по (п-(-Г)-ю, управляющий вход регистра предпредыдущего значения функции, первый управляющий вход регистра предыдущего значения функции, вторые управляющие входы регистров производных и регистра функции, второй вход блока управления и первый установочный вхоД пересчетной схемы подключены к выходу , элемента И, (п+2)й вход которого соединен с выходом схемы сравнения, первый управляющий вход схемы сравнения соединен с выходом узла контроля нуля, вход которого соединен с выходом блока вычисления членов ряда Тейлора отрицательного аргумента, нулевой вход триггера контроля, третьи управлянядие входы регистров производных и функции, вторые управляющие входы накопителей значений производных и функции положительного аргумента, третий управляющий вход накопителя значения функции отрицательного аргумента, второй управляющий вход регистра приращения аргумента, первый управляющий вход блока задания аргумента, третий вход блока управления соединены с выходЬм пересчетной схемы, второй информационный вход регистра предыдущего значения функции, вторые информационные входы регистров начальных условий- по производным и по функции, третьи входы накопителей значений производных и функции положительного аргумента, четвертый вход накопителя значения функции отрицательного аргумента, четвертые информационные входы регистров производных и функции, а также информационный вход блока задания интервала аргумента и информационный вход регистра приращения аргумента соединей с входом задания начальных условий ,. границ интервала и шага устройства, четвертый вход блока управления соединен с первым выходом блоч ка задания интервала аргумента, второй выход которого подключен к инфор мационным входам элементов И {п+1)-й группы, выходы KOTOpbix соединены с выходом аргумента устройства, первый выход блока управления соединен со . вторым управляющим входом схемы сравнения/ с управляющим входом регистра предьщущего значения частичной суммы, четвертый выход блока управле-ния соединен со вторым установочньв-i входом пересчетной схемы, пятый вы;:од блока управления соединен со вторыми управляющими входами регистров начальных условий по производным и по функции, со вторым управляющим входом регистра предыдущего значения функции, со вторым нулевыг входом триггера контроля, шестой.выход блока управления соединен со вторыгу управляющим входом блока задания интервала аргумента. Кроме того, первый, второй, третий, четвертый, пятый и седьмой выходы блока управления, а также выход элемента И и выход пересчетной схемы соединены соответственно с управляющими входами генераторов переменных коэффициентов и генератора правой части, седьмой выход блока управления сое.динен с управляющими входами блоков коммутации нелинейностей, с управляющими входами блоков вычисления числовых значений производных произведений переменных, с входом пересчет.ной схемы.

2, Устройство по П.1, отличающееся тем, что каждый генератор переменных коэффициентов и генератор правой части содержат сумматор, регистр приращения аргумента, р блоков вычисления членов рядов Тейлора положительного аргу- ; мента и блок вычисления членов ряда Тейлора отрицательного аргумента, накопитель значения функции и р-1 накопителей значений производных положительного аргумента, накопитель значения функции отрицательного аргумента, схему сравнения, регистр пред предыдущего значения функции и регистр предыдущего значения функциИь

:р+2 групп элементов И, р- регнст,ров производных и регистр функции, р-1 регистров начальных условий по производным и регистр начальных условий по функции, р регистров постоян;ных коэффициентов, р узлов умножения, регистр пред лдущего значения частичной су1-1мы, узел, контроля нуля, триггер контроля, регистры производных и функции соединены последовательно, выход i-ro (те ,3,..., р) регистра подключен к первому информационному входу (i-l)-ro регистра, выход каждогорегистра производных и регистра функции соединен с первым входом соответствующего блока вычисления членов рядов Тейлора положительного аргумента и с первым входом соответствующего узла умножения, второй вход которого соединен с выходом соответствующего регистра постоянных коэффициентов, выходы узлов умножения соединены с соответствующими входами сумматора, выход котоiporo соединен с первым информационным входом регистра (р-1)-й произ.водной, выходы блоков вычисления членов рядов Тейлора положительното аргумента со второго по р-й соединены с первыми входами соответст:вующих накопителей значений произ:водных положительного аргумента, а выход первого блока вычисления членов .ряда Тейлора соединен с первым входом накопителя значения функции положительного аргумента,выход регистjpa функции соединен с первым входом блока, вычисления членов ряда тейло-.. ра отрицательного аргумента, выход которого соединен с первым входом накопи.теля значения функции отрицательного аргумента, выходы нак9пи-телей.значений производных и функции положительного аргумента подключены соответственно к информационному входу элементов И групп с первой по р-ю, выходы которых соединены со вторыми информационными входами соответствующих регистров производных и функции и с первыми информацион|ными входами, соответствующих регистров начальных условий по производным и по функции, выходы которых соединены со вторыми входами соответствующих накопителей значений производных и функции Г1ОЛОЖИтельного аргумента и с третьими информационными входами соответствующих регистров производных и функции, второй и третий входы накопителя значения функции отрицательного аргумента соответственно соединены с выходом регистра начашьных условий по функции и с выходом элементов И первой . группы, выход накопителя значения функции отрицательного аргумён.та соединён с первым информационным входом схемы сравнения и с информационным

входом регистра предыдущего значения частичной суммы, выход которого подключен к информационным входам элементов И (р+1)-й группы, выходы которых подключены ко второму информационному входу схеглы сравнения, выходы элементов И первой группы подключены к первому информационному входу разрядов регистра предьщущего значения функции, выход которого соединен с информационным входом регистра предпредыдущего значения функции, выход регистра предпредыдущего значения функции подключен к информационным входам элементов И {р+2)-й группы, выходы кото.рых подключены к третьему информационному входу схемы сравнения, управляющие входы элементов И (р+1)и (р+2)-й групп соответственно подключены к нулевому и единичному выходам триггера контроля, первый управляющий вход схемы сравнения соединен с выходом узла контроля нуля, вход которого соединен с выходом блбка вычисления членов ряда Тейлора отрицательного аргумента, вторые входы блоков вычисления членов рядов Тейлора положительного аргумента и блока вычисления членов ряда Тейлора отрицательного аргумента соединены с выходом регистра приращений аргумента, информационный ёход регистра приращений-аргумента, информационные входы регистров постоянных коэффициентов, второй информационный входрегистра предьщущего значения функции, вторые информационные входы регистров начальных условий по производным и по функции, третьи входы накопителей значений производных и функции положительного аргумента, четвертый вход накопителя значений функции отрицательного аргумента, четвертые информационные входы регистров производных и функции подключены к информационному входу генератора, первые управляющи.е входы накопителей значений производных положительногоаргумента, значения функции положительного аргумента, значения функции отрицательного аргумента, второй управляющий вход схемы сравнения, управляющий вход .регистра предыдущего значения частичной суммы, управляющие входы блоков вычисления членов рядов Тейлора положительного аргумента и блока вычисления членов ряда Тейлора отрицательного аргумента, первый управляющий вход регистра приращения аргумента, первые управляющие входы регистров производных и регистра функции, пер вьте управляющие входы регистров начальных условий по производным и по функции, первый нулевой вход тригге ра контроля, первый управляющий вход регистра предьщущего значения функции, управляющие входы узлов умножения, управляющие входы регистров постоянных коэффициентов, а также единичный вход триггера контроля, второй управляющий вход регистра предыдущего значения функции, управляющий вход регистра предпредыдущего значения функции, второй управляющий вход накопителя значения функции отрицательного аргумента, управляющие входы элементов И групп с первой по р-ю, вторые управляющие входы регистров производных и регистра функции, вторые управляющие входы регистров начальных условий по производным и по функции, второй нулевой вход триггера контроля, третьи управляющие входы регистров производных и функции, вторые управляющие входы накопителей значений производных и функции положительного аргумента, третий управляющий вход накопителя значения функции отрицательного аргумента, второй управляющий вход регистра приращения аргумента соединены с управляющим входом генератора, выход регистра функции подключен к первому выходу генератора, выход схемы сравнения подключен

ко второму выходу генератора.

1

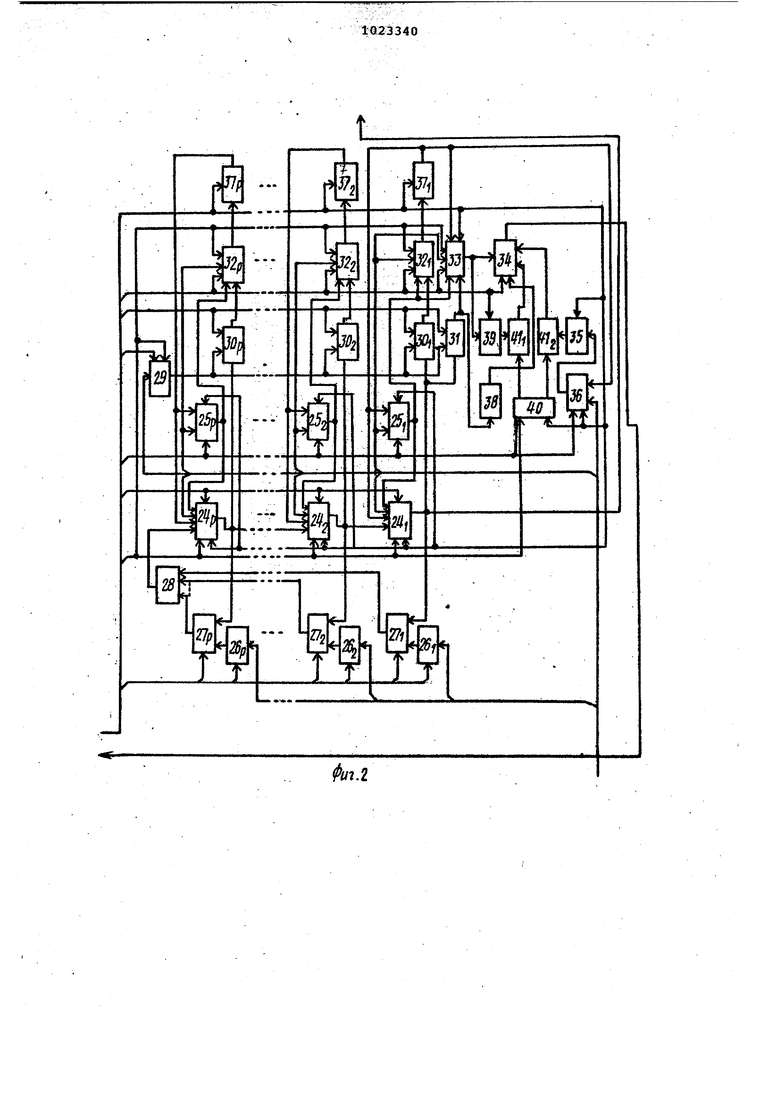

3. Устройство ПО-П.1, о т л и чающееся тем, что блок вычисления ЧИСЛОВЫХ значений производных произведения переменшлх, количество которых равно 1+1 (где1 1, 2,...,q), а порядок производных равен I (где ,1,2,-i.. ., k-1 ) ,. содержит k-cj регистров -первых сомножителей и их производных г-и (где - 1-fk) строки Д)-го (гдер lf(|) столбца, (k-l)q регистров вторых сомножителей и их производных i-и (где .k) строки -О-го (где Ti)l-rq) столбца и регистр вторых сомножителей и их производных первой строки первого столбца, k-1 регистров коэффициентов, k-2 двухвходовых сумматбров коэффициентов, k-2 первых узлов умножения, k вторых узлов умножения, k-входовый сумматор, группу элементов И, регистр количества сомножителей в нелинейности, причем выходы каждых предыдущего и последующего регистров коэффициентов подключены к входам соответствующего двухвходового сумматора коэффициентов, выход которого подключен к информационному входу того же последующего регистра, выходы регистров коэффициентов, за исключением выхода первого регистра коэффициентов, соединены с первыми входами соответствующих первых узлов умножения, вторые входы которых соединены с выходами регистров первых сомножителей и .их производных первого столбца соответствующей 1-й.(где i 2Tk-l) строки, при этом выходы регистров первых сомножителей и их производных первого столбца i-й (где ) строки соединены с первыми информационнымивходами регистров первых сомножителей и их производных всех q столбцов соответственно той же i-й cTjpoки, выходы регистров первых сомножителей и их производных-г -го (где . ,3,.., стрлбца каждой i-й (где lfk) строки соединены со вторыми информационными входайи регистров первых сомножителей и их производных (у-1)-го столбца той же каждой i-й строки, третьи информационные входы регистров первых сомножителей и их производных 1-го, 2-го, ..,, qrrq столбцов всех (где tTk) строк подсоединены к соответствующим входам производных и функции блока, выходы первых узлов умножения и выходы регистров первых сомножителей и их производных первойи k-й строк первого столбца соединены с первыми входами соответствую тих вторых узлов умножения, вторые входы которых соединены с выходами соответствующих регистров вторых ; сомножителей и их производных первого столбца i-й (где ) строки и регистра вторых сомножителей и их производных первого столбца первой строки, выходы вторых узлов ; умножения соединены с входами k-Bxo дового сумматора, выход регистра ; вторых сомножителей и их производных первого столбца первой строки и выходы регистров вторых сомножителей и их производных первого столбца i-й (где i 2rk-l) строки соединены с первыми информационными входами регистров вторых сомножителей и их производных всех q столбцов последующей i+1 строки, выходы регистров вторых сомножителей и их производных f-го (где ,3,. .. ,11} : столбца каждой i-и (где i 2 k) стро ки соединены со вторыми информационными входами регистров вторых сомножителей и их производных (V-1)-го столбца той же каждой i-ой строки, первый и второй информационные регистра вторых сомножителей и их ; производных первой строки первого столбца соответственно соединены с i входом переменного коэффициента бло-ii ка и с выходом k-Бходового суммато ; ра, при этом выход k-входового сум- ; матора подключен к входу группы элементов И, выход которой соединен с выходом блока, первые управляющие входы регистров первых сомножителей и их производных 1-го, 2-го,,..., q-ro столбцов i-x (где i lTk) стЬок и ре гистров вторых сомножителей и их производных 1-го, 2-го, ..., q-ro столб ;,ов i-x (где ) строк соединены с соответствующими выходами

регистра количества сомножителей в нелинейности, вход которого соединен с входом количества сомножителей в нелинейности блока, первый управ.ляющий вход регистра вторых сомножи телей и их производных первой строки iпервого столбца, вторые управляющие входы регистров первых сомножителей и их производных и регистров вторых сомножителей и их производных, синхронизирующие входы регистров первых : сомножителей и их производных, регистров вторых сомножителей и их про из(водных и регистров коэффициентов, за исключением первого регистра коэффициентов, третьи управляющие ВХОДЫ регистров первых сомножителей и их производных, управляющий вход группы элементов И, управляющие :входы первых и вторых узлов умноже; ния соединены с управляющим входом iблока.

: 4. Устройство по п.1, о т л и ;ч а ю щ е е с я тем, что блок зада1ния интервала аргумента содержит регистр приращения аргумента, сум.матор, регистр значения аргумента в начале интервала, регистр значения аргумента в койце интервала, схему сравнения, причем первый вход сумматора соединен .с выходом регистра приращений аргумента, информационный вход которого соединен с информационным входом блока, второй вход ; сумматора и его выход соединены, соответственно с выходом и первым информационным входом регистра значения аргумента в начале интервала, при этом выход регистра значения аргумента в начале интервала соединен с первым выходом схемы сравнения, второй вход которой соединен с входом регистра значения аргумента в конце интервала, второй информационный вход регистра значения аргумента в начале интервала и информационный вход регист|)а значения аргумента в конце интервала соединены с информационным входом блока, первый управляющий вход регистра значения аргумента в начале интервала соединен с первым управляющим входом бло;Ка, второй управляющий вход регист:ра Приращения аргумента, второй управляклций .вход регистра значения аргумента в начале интервала и управ:ляющий вход регистра значения аргумента в конце интервёша, третий : управляющий вход регистра приращения аргумента и третий управляющий вход, регистра значения аргумента в нача1ле интервала соединены с вторым управляющим вхсдаом блока, первый выход блока соединен с выходом схемы сравнения, второй выход блока соединен с выходом регистра значения аргумента в начале -интервала.

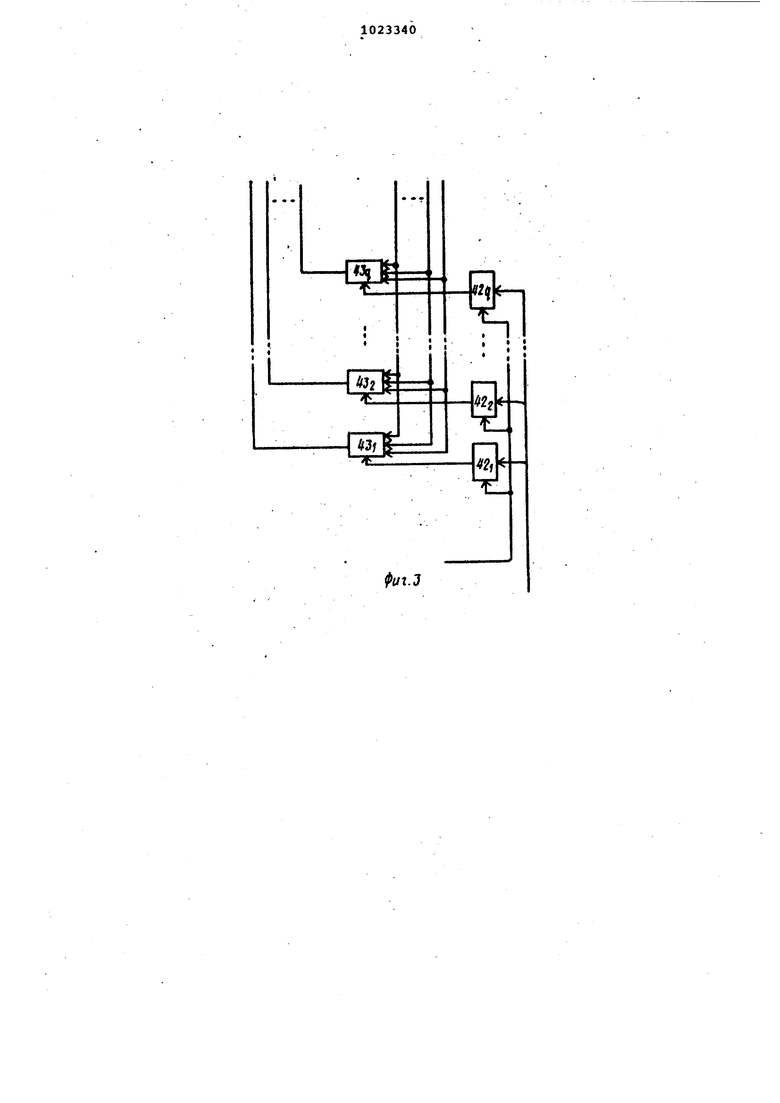

5.Устройство по п.1, о т л и чающееся тем, что блок вычио ления членов ряда Тейлора содержит регистр, узел деления, первый узел умножения, второй узел умножения, причем выходы первого узла умножения и регистра соответственно соединены с первым информационным входо регистра и с входом делимого узла деления, выход которого соединен с первым входом первого узла умножения и с первым входом второго узла умножения, второй вход и выход которого соответственно соединены с первым входом и выходом блока, второй вход первого узла умножения и второй информационный вход регистра соединены со вторым входом блока, вход делителя узла деления, управляющий вход

(регистра, управляющий вход узла деле ния, управляющие входы первого и второго узлов умножения соединены с управляющим входом блока.

6.Устройство по п.1,о т л и ч д ю щ е-е с я тем, что блок управления содержит генератор тактовых импульсов, пять синхронных. RS-триггеров, два асинхронных RS-триггера, девятнадцать элементов И, группу элементов И, элементов ИЛИ, два дешифратора, регистр с единичным кодированием, три пересчетные схемы, кольцевой счетчику кнопку Исходное состояние, кнопку причем единичный выход первого синхронного RS-триггера соединен с первыми входами первого, второго, третьего, пятого, шестого, восьмого элементов И, а нулевой выход соединен

с его единичным синхронным входом и с первым входом седьмого элемента И, единичный выход второго синхронного RS-триггера соединен со вторыми вхоч дами первого, шестого, восьмого элеп ментов И, а нулевой выход соединен с первым входом четвертого элемента И и вторыми входами третьего, пятого и седьмого элементов И, единичный выход третьего синхронного RS-триггёра соединен со вторыми входами второго элемента И, четвертого элемента И и с третьим входом шестого элемента И, а нулевой выход - с третьими входами первого и восьмого элементов И, выходы первого, второго, третьего элементов И подключены к соответствующим входам первого элемента ИЛИ, выход которого соединен с нулевым синхронным входом первого синхронного RS-триггера выходы четвертого и пятого элементов И подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с единичным син хронным входом второго синхронного RS-триггера, выходы iaecToro и седь-,

мого.элементов И подключены к соответствующим входам третьего элемента ИЛИ, выход которого соединен с нулевым синхронным входом третьего синхронного RS-триггера, выход восьмого элемента И соединен с нулевым и единичным синхронными входами соответственно второго и третьего синхронных RS-триггеров, единичный выход четвертого синхронного RS-триггера соединен с первыми BXOдами девятого, двенадцатого и тринадцатого элементов И, а нулевой выход соединен с первыми входами девятого и одиннадцатого элементов И, единичный выход пятого синхронного RS-триггера соединен со вторыми входами девятого, десятого и двенадцатого элементов И, а нулевой выход соединен со вторыми входами одиннадцатого и тринадцатого элементов И, выходы девятого и тринадцатого, десятого и одиннадцатого элементов И соответственно подключены к соответствующим входам четвертого и пятого элементов ИЛИ, выходы которых соответственно соединены с нулевым и единичным синхронными входами четвертого синхронного RS-триггера, выходы двенадцатого и тринадцатого элементов и соответственно соединены с нулевым и единичным синхронными входами пятого синхронного RSтриггера, первы.е нулевые асинхронные входы первого, второго, третьего четвертого и пятого синхронных RSтриггеров соединены с выходом кнопки Исходное состояние, вход которой соединен с выходом генератора тактовых импульсов, единичньай асинхронный вход первого синхронного RS-триггера и вторые нулевые асинхронные входы второго, третьего, четвертого и пятого синхронных RSтрйггеров соединены с выходом шестого элемента ИЛИ, синхронизирующие входы первого, второго, третьего, четвертого и пятого синхронных RSтриггеров соединены с выходом четырнадцатого элемента И, первый и второй входы которого соответственно соединены с выходом генератора так-, товых импульсов и с единичным-выходом первого асинхронного RS-триггера, единичный вход которого подключе к выходу кнопки Пуск, вход которой соединён с выходом генератора тактовых импульсов, выходы первого, второго и третьего синхронных RS-триггеров подключены к входс1М первого дешифратора, а выходы четвертого и пятого синхронных RS-триггеров подключены к входам второго дешифратора, нулевой выход первого дешифратора соединен с управляющим входом регистра с единичным кодированием, первый выход первЪго дешифратора сое|динен с установочным входом кольце ; вого счетчика и с нулевым входом второго асинхронного RS-триггера, второй выход первого дешифратора соединен с первыми входами К элементов группы элементов И, с первыми входами седьмого элемента ИЛИ, девятнадцатого элемента И и с входом кольцевого счетчика, третий выход первого дешифратора соединен с первыми входами, пятнадцатого и шестнадцатого элементов и, вторые входы которых соединены с выходом четырнадцатого элемента И, четвертый выход перво- . го дешифратора соединен со вторым входом седьмого элемента ИЛИ, пятый выход первогодеедфратора соединен с единичным входом: второго асинхронного RS-триггера, единичный выход которого соединен со втррым входом девятнадцатого элемента И, седьмой выход первого дешифратора соединен с третьим входом од инйадцатого эле мента И, выход.регистра с единичным кодированием сойдйнен с входом установки коэффициентов пересчета первой йересчетной схемы, вход которой соединен с выходом второй переочетной схемы, вход второй пересчетной схемы соединён с выходом пятнадцатого элемента И, кроме того, выход второй пересчетной схемы соединен , с четвертыми входами первого и восьмбго элементов И, а выход первой пересчотной схемы соединен с пятым :входом первого элемента И, установочные входы первой, второй и третьей пересчетной схем соответственно сое;динены с выходом кнопки .Исходное состояние и с выходом шестого эле- ИЛИ, перцый выход второго де-

шифратора роединен с первыми входами ;семнадцатого и восемнадцатого элементов И, вторые входы которых соединены с выходом четырнадцатого элемента И, выход семнсодцатого элемента И соединен с входом третьей пересчетной схемы выход которой соединен с третьим входом трин.адцатого элемента И, к первому входу блока {тодключен информационный вход регистjpa с единичным кодированием, ко второму входу блока подключен первый вход шестого элементаИЛИ, к третьему входу блока подключен второй вход Шестого элемента ИЛИ и второй выход блока, к четвертому входу блока подIключен нулевой вход первого асинхрон ного RS-триггера, к первому выходу яблока подключены нулевой выход первого дешифратора, второй и третий выходы второго дешифратора, ко вто. рому выходу блока подключены третий .вход блока, седьмой выход первого :дешифратора и выход восемнадцатого I элемента И, к третьему выходу блоi ка подключен нулевой выход первого дешифратора, к четвертому выходу блока подключены нулевой и шестой, выходы первого дешифратора, к пято:му выходу блока подключен нулевой выход первого дешифратора, к шестому выходу блока подключены нулевой И первый выходы первого дешифратора, к седьмому выходу блока подключены :первый, второй .и пятый выходы дешифратора, выходы k элементов И группы, выходы седьмого эле мента ИЛИ, шестнадцатого и девятГнадцатого. элементов и и выходов первой пересчетной схеIJMH. . . . t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1977 |

|

SU732880A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Функциональный аналого-цифровой преобразователь | 1975 |

|

SU1270776A1 |

| Устройство для нахождения экстремума аддитивной функции многих переменных | 1990 |

|

SU1765830A1 |

| Функциональный преобразователь | 1988 |

|

SU1619258A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Ассоциативное запоминающее устройство | 1985 |

|

SU1277211A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

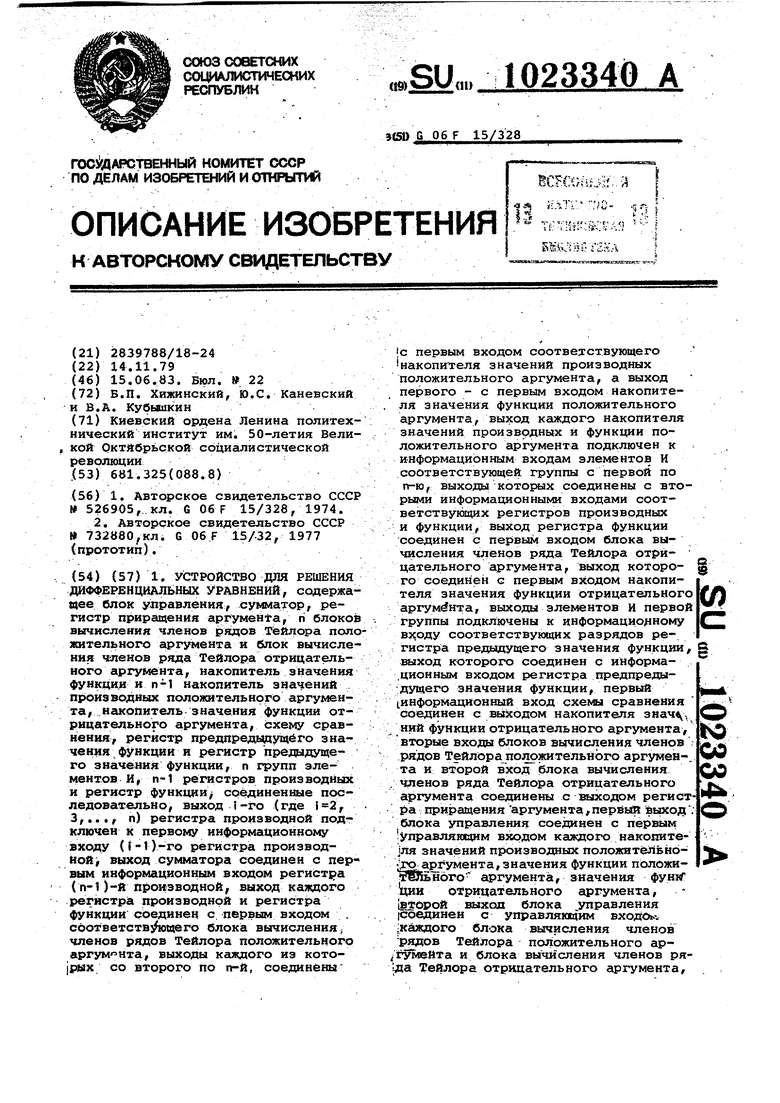

1. УСТРОЙСТВО ДЛЯ РЕШЕНИЯ даФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ, содержащее блок управления, сумматор, регистр приращения аргумента, п блоков вычисления членов рядов Тейлора положительного аргумента и блок вычисления ч-ленов ряда Тейлора Отрицательного аргумента, накопитель значения функции и п-1 накопитель значений производных полоисительнрго аргумента, накопитель значения функции отрицательного аргумента, схему сравнения, регистр предпредыдущёго значения функции и регистр предыдущего значения функции, п групп элементов И, п-1 регистров производных и регистр функции/ срёдиненшае последовательно, выход i-гчэ (где , . 3,..., п) регистра производной подключен к первому информационному входу (}-1)-го регистра производной выход сумматора соединен с первым информационным входом регистра (п-Т)-й производной, выход каждого регистра производной и регистра функции соединен с первым входом , соответств Лощего блока вычисления, членов рядов Тейлора положительного аргумента, выходы каикдого из котоjpHX со второго по п-й, соединены (с первым входом соответствующего накопителя значений производтлх положительного аргумента, а клход первого - с первым входом накопите. ля значения функции положительного аргумента, выход каждого накопителя значений производных и функции положительного аргумента подключен к информационным входам элементов И .соответствующей группы с первой по п-ю, выходы которых соединены с вторыми информационными входами соответствующих регистров производных и функции, выход регистра функции соединен с первым входом блока вычисления членов ряда Тейлора отрицательного аргумента, выход которого соединен с первым входом накопителя значения функции отрицательного аргумента, выходы элементов и первой группы подключены к информационному входу соответствующих разрядов регистра предыдущего значения функции, выход которого соединен с информа.ционным входом регистра предпредыдущего значения функции, первый (.информационный вход схемы сравнения соединен с выходом накопителя НИИ функции отрицательного аргумента, 10 вторые входы блоков вычисления членов О9 рЭ 4ii рядов ТейлОра положительного аргумен-. та и второй вход блока вычисления .членов ряда Тейлора отрицательного аргумента соединены с выходом регистра приращения аргумента , первьа выход; .блока управления соединен с первым .управляющим входом каждого накопите ля з начений производных положитёЛвноigo. аргумента, значения функции положительного аргумента, значения фун ции отрицательного аргумента, второй выход блока управления (Соединен с управляющим входоь-. :каждого блока вычисления членов Р5До Тейлора положительного ар(ГумеНТа и блока вычисления членов Тейлора отрицательного аргумента.

Изобретение относится к вычислительной технике и может быть использов.анс для решения с заданной точностью неоднородных линейных и нелинейных дифференциальных уравнений с переменными коэффициентами

Известно устройство для решения дифференциальных уравнений, содержащее регистр функции, регистры производных, регистры приращений функции, приращений производных и приращений аргумента, регистр старшей производной, регистры постоянных и переменных коэффициентов блоки анализа, триггеры знака, :блок правления, коммутатор, блок .сдвига и блок элементов ИЛИ til.

В этом устройстве решение одно- , родного линейного дифференциального уравнения с постоянными коэффициентами

;vi} . (ни) Y «V, Y

(1)

н интервале

)

при начальных условиях

Г -о,. V (3

происходит путем вычисления числовых значений частичных сумм

(м) W h

.rV- TfTTTir П ()

It-i

j

оответственно рядовТейлора

Л(х - х,)

Y(x)y;

i I

.1

f (x-xj )

:х)1У

(5)

)

1

1-:0

vTx ) Y iil2iiZ.

для калсдой точки интервала j+1, где -f I-1, с шагом

h ux °

(6)

причем количество точек г такое, что выполняется условие .

Числовые значения частичных сумм () соответственно представляют числовые значения функции У , являющейся решением уравнения {1), и

производных Y; , . . . .В ТОЧКв

j+1 интервала.

При решении уравнения (1) устройство работает в трех последовательных во времени режимах.

В первом режиме формируются и вычисляются числовые значения переменных йоэффициентов

h

Ь.

для ,2,...,п., л

Всего за время решения уравнения (1 ) вычисления в этом режиме выполняются один раз.

Во втором режиме формируется и вычисляется числовое значение старшей пр.оивводной

vf

. -.-a.Y. 3у,- Yj +,

в точке j аргумента. Всего за время решения уравнения {1)| вычисления в этом режиме выполняются г раз.

В третьем режиме формируются и вычисляются числовые значения функции и производных

Y- +bYJM , - Y; H- &Yj+.( ,

j- v«-

B точке J+1 интервала. Для этрго j первоначально формируются и заычисляются числовые значения приращений функции и производных

+ ь„.„ у --+ь у.

AYjH V. +.

« J

j

в точке j+1 интервала. Всего за время решения уравнения (1 вычисления в этом режиме выполняются г раз.

. Известно, что точность вычислений с использованием ряда Тейлора при заданной величине шага зависит от количества членов в частичной сумме, посредством которой этот ряд Тейлора представляется. Чем болше количество членов будет содержатся в частичной сумме, тем с большей точностью будет получен результат.

Поскольку количество членов в частичных суммах (4) соответственно равно п+1, п, ..., 1, где п - порядок решаемого уравнения (1), то при заданной величине шага h точность вычисления числовых значений производных Y/ . в данной точке интервала понижается с каждым повышением их порядка, что понижает точность вычисления числового значения функции YJ4.1 в последующей точке интервала. Кроме того, чем ниже порядок п, тем с меньшей точность1о будет вычислено числовое значение функции Y,jj.. Следовательно, неодинаковое количество членов в частичных суммах {) обуславливает в устройстве понижение точности решения уравнения (1) в каждой последующей точке интервала, а зависимость количества членов в частичной сумме, представляющей функцию YA , от порядка решаемого уравнения (1) обуславливает в устройстве зависимость точности решения уравнения (1 от его порядка.

В связи с тем, что количество членов в частичной сумме, представляющей функцию Yj , ограничено порядком |t решаемого уравнения (1), то достичь заданной точности решения этого уравнения можно путем подбора соответствующей величины шага h. Для этого требуется получить контрольные решения уравнения (1) с различными величинами шага h путем решений этого уравнения-на устройстве, а затем сопоставить и сравнить эти решения между собой. Однако необходимость подбора требуемой величлны шага значительно увеличивает время получения решения, а последовательный во времени характер вычислительного процесса в устрюйстве также значительно увеличивает время получения решения.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее блок управления, сумматор, регистр приращений аргумента, блоки вычисления чле нов рядов Тейлора положительного аргумента и блок вычисления членов ряда Тейлора отрицательного аргумента, накопители значений-функции и производных положительного аргумента, накопитель значения функции отрицательного аргумента, схему сра нения, регистр предпредьщуадего значения функции и регистр предыдущего значения функции/ группы элементов И, регистры постоянных коэфф циентов, блоки умножения, регистры производных и регистр функции, которые соединены последовательно в по рядке убывания порядка производной, выходы каокдого регистра производных и регистра функции соединены с первыми входами соответствующих блоков умножения, второй вход каждого блок умножения соединен с выходом соответствующего регистра постоянных ко эффициентов, выходы блоков умножени соединены с входами сумматора, выт хрд которого соединен с входом регистра (п-1)-ой производной, выходы регистров производных и регистра функции соединены с первыми вводами соответствующих блоков вычисления f членов рядов Тейлора положительного аргумента, выходы которых соединены соответственно с входами накопителе значений производных и накопителя значения функции положительного ар. гумента., выходы которых через группы элементов И соединены соответственно с входами регистров производных и регистра функции, выход регис ра функции соединен с первым входом блока звычисления членов ряда Тейлор отрицательного аргумента, выход к6торого соединен с входом накопителя . значений функции отрицательного аргумента, вход регистра предыдущего зИачения функции через группу элементов И соединен .с выходом накопителя значений функции положительного аргумента, выход регистра предыдущего значения функции соединен с входом регистра предпредыдущего значения функции, входы схемы сравнения соединены соответственно с выходами накопителя значений функции отрицательного аргумента и реги стра предпредыдущего значения функции, выход схемы сравнения соединен с управляющими входами групп элементов И, регистров предпредыдуадего значения функции, предыдущего значения функции, с первыми управляющими входами регистра функции и регистров производных и с входом блока управления, вторые входы блоков вычисления членов рядов Тейлора положительного аргумента и вычис ления членов ряда Тейлора отрицательного аргумента соединены с выхо дом регистра приращений аргумента. управляющий вход которого, управляю щие входы регистров постоянных коэффициентов , управляющие входы накопителей значений производных положительно.го аргумента, значения функции положительного аргумента, значения функции отрицательного аргумента, блоков вь1числения членов рядов Тейлора положительного аргумента и вычисления членов ряда Тейлора отрицательного аргумента, вторые управляющие входы регистра функции и регистров производных соединены с соответствующими выходами блока управления, В этом устройстве решение однородного линейного дифференциального уравнения с постоянными коэффициентами (1) на интервале (2), при начальных условиях (3), с шагом (6) происходит в результате протекания параллельно во времени двух вычислительных процессов. Первый вычислительный процесс обуславливает формирование и вычисление по уравнению (t) r-v. ч Y -f-a Y.. +...+а -3 : -j представляющему уравнение (1), от которого взята 2-я, где t i , ,l,2, ..., .производная, числового значения производной в точке j, где ,2,..,,г-1, интервала. Этим подготавливаются числовые значения производных ,Yj(i+«, .... Yi .которые, если учесть, что очередное значение i увеличивается на единицу, являются исходными числовм и эначениями производных YJ- , У/ ..., необходимыми для обеспечения вычислений во втором вычислительном процессе при очередном значении i . Второй вычислительный процесс л обуславливает формирование и вычисление числовых значений членов J« (-hf 1Г ТГ ,(ш+е) h -W(71 f |Г j|г В точках J-1 и j-fl интервала соответственно рядов Тейлора (5), суммиррванйё числовых значений членов (7) с числовыми значениями соответственно частичных сумм Ц ii, . и n(-h) (5-i), i -гг tf. tj+i:ie-i 0 Y.f- (H,E% o j -ТГ (и-11t-A ( h У . -г Y -n,e-i 3 в точках j-1 и j-fl интервала тех рядов Тейлора (5)(при 1 0числовые значения частичных сумм (8) равны нулю) с целью получения и накопления более точных, по сравнению с.ч ловыми значениями частичных сумм (8 У, числовых значений частичных сумм W (-hf j-i),e ТГ tji-i),E (j-t.-iie-i М V м Y +у( (Q) (j+l),f Чй« Et (nHtW I/ 4iH),f «( IT в тех же точках j-1 и j+1 где ,2,...,г-1, интервала соответст венно рядов Тейлора (5) для t i, ,1,2,.... I Числовые значения частичных сум (9) соответственно представляют чис ловые значения решений .Y и Y,j-j. в точках j-1 и j+l интервала, число вые значения производных , . . . У, решения в точке j+l интервала точность вычисления которых определ ется одинаковым количеством однотип ных членов соответственно рядов Тейлора (5), равным t+1 и не завися щим от порядка п уравнения (1). Поскольку при заданной величине шага h точность вычисления числовых значений частичных суг/jM {9 ) повышается каждый раз при каждом очередно увеличении значения i, то числовые значения решений Y; и У в точ ках j-1 и J+1 интервала, числовые значения производных решения il, , , . . , в точке j+l интервала могут быть вычислены с любой точнос тью посредством соответствующего увеличения значения i. Точность вычисления числовых зна чений искомых решений Y и Y.,v в точках j-1 и j+l интервала, искомых производных Y,, ,-.., YjTr реш ния в точке j+l ийтервала задается точностью представления известного .числового значения решения Y ; в точке j-1 интервала. Заданная точность вычисления чис ловых значений искомых решения А и производных Yi , ..., YJI}; решения в точке j+l интервала достигается одновременно с достижением заданной точности вычисления числового значения искомого решения Yy.;, в точке j-1 интервала, которое наступает при достижений равенства числового 3 начения искомого решения Yj. в точке j-1 интервала, полученного путем вычисления числового значения частичной суглмы Yu--t),p , например, при и,.и числового значения известного решения Y; в точке j-1 интервала. Точность вычисления числового значения частичной сугфол . ,),е контролируется при каждом значении i. В заивисимости от результата контроля устройство автоматически выбирает нужное направление дальнейшего протекания вычислительного процесса. Если, например при для числового значения искомой частичной суммы (i),e числового значения известного решения Y,).i в точке j-1 интер-. вала имеет место соотношение. . . (}-1),к f 1 то устройство продолжает описанный вычислительный процесс при с целью получения более точных числовых значений частичных сумм (9). Если, наприг1ер, при для указанных числовых значений имеет место соотношение Y, Y. (J-1),K }-1 то, поскольку числовые значения частичных сумм (9) достигли заданной точности, устройство выдает результат )4.t l+f l. (w-0 ..M ЧУ-Н К . при данном значении | и начинает описанный вычислительный процесс с целью получения числовых значений решения и производных решения, т.е. результата, при последующем значении j, Для эта го, чтобы устройство могло начать описанный вычислительный процесс требуется в подготовительном режиме получить числовые значения решения и производных , ..., решения в точке 1 интервала . Устройство обладает высоким быстродействием за счет распараллеливания протекающего в нем вычислительного процесса 2. . Однако данное устройство, обладая высоким быстродействием, позволяет решать, обеспечивая -автоматически заданную точность решения, лишь однородные линейные дифференциальные уравнения с постоянными коэффициентами типа (1) на интервале (2) при начальных условиях (3) с шагом (6) и не позволяет решать неоднородные линейные и нелинейные дифференциальные уравнения с переменными коэффициентами типа . (x). . . + b (x)Y +b(x)Y f(x), ),(....V-.Y) + b (X ) 4 ( ,. . . .Y ,Y)Y + +.Ьд (x)vfp( ... .Y ,Y)Y f(x) (1 на TOM же интервале (2 ), при -тех же начальных условиях (3) с тем же ша гом (6). Целью изобретения является расши рение функциональных возможностей, устройства за счет решения неодно™ родных линейных и нелинейных дифференциальных уравнений с переменными коэффициентами. ПостсШленная цель достигается тё что в устройство,. содержа15|ее блок управления, сумматор, регистр прира щения аргумента, п блоков вычислени членов рядов Тейлора положительного аргумента и блок вьтисления членов ряда Тейлора отрицательного аргумен та, накопитель значения функции и n-i накопитель значений производных положительного аргумента, накопител значения функций отрицательного аргумента, схему сравнения, регистр предпредьодущего значения функции и регистр предыдущего значения фукнци п групп элементов И, п-1 регистров производных и регистр функции, соед ненные последов ательно, выход i-го (где ,3,..., п) регистра производной подключен к первому информационному входу (i-1)-го регистра производной, выход сумматора соединен с первым информационным входом регистра (п-1)-й производной, выход каждого регистра производной и регистра функции соединен с первым входом соответствующего блока вычисления членов рядов Тейлора полбжительного аргумента, выходы kasCCoго из которых со второго по п-й, сое1динены с первым входом соответствующего накопителя значений производных положительного аргумента, а выход первого - с первым входом накопителя значения функции положительного аргумента, выход каждого накопителя значений производных и функции положительного аргумента подключен к информационным входам элементов И соответствующей группы с первой по п-ю, выходы КОТОРЫХ сое динены с вторыми информационными входами соответствующих регистров производных и функции, выход регист ра функции соединен с первым входом блока вычисления членов ряда Тейлора отрицательного аргумента, выход которого соединен с первым входом накопителя значения функции отрицательного аргумента, выходаа элементов И первой группы подключены к информационному входу соответствующих разрядов регистра предыдущего значения функции, выход которого соединен с информационным входом регистра предпредыдущего значения функции, первый информационный вход схемы сравнения соединен с выходом накопителя значений функции отрицательного аргумента, вторые входы блоков вычисления членов рядов Тейлора положительного аргумента и второй вход блока вычисления членов ряда Тейлора отрицательного аргумента соединены с выходом регистра приращения аргумента, первый выход блока управления соединен с первым управляющим входом каяодого накопителя значений производных положительного аргумента, значения функции положительного аргумента, значения функции отрицательного аргумента, второй выход блока управления соединен с управляющим входом каждого блока вычисления членов рядов Тейлора положительного аргумента и блока вычисления членов ряда Тейлора отрицательного аргумента, третий выход блока управления соединен с первым управляющим входом регистра приращений аргумента, а четвертый выход блока управления соединен с первым управляющим входом регистров производных и регистра функции, введены п блоков коммутации нелинейностей,-п блоков вычисления числовых значений производных произведения переменных, п генераторов переменных коэффициентов, генератор правой части, п-1 регистров начальных условий по про- . изводным и регистр начальных условий по функции, блок задания интервала аргумента, регистр предыдущего значения частичной суммы, узел контроля нуля, триггер контроля, (n-fl )-я, ()-я и (п+3)-я группы элементов И, пересчетная схема и элемент И, причем входы производных и функции, входы номеров регистров производных и регистра функции блоков коммутации нелинейносТёй соединены соответственно с выходами регистров производных a регистра функции и с соотвётствующими входами номеров регистров производньк и регистра функции устройства, входы производных и функции, вход переменного коэффициента и ход количества сомножителей в нелинейности блоков вычисления число- .вых значений производных произведения переменных соответственно соединены с выходами соответствующих блоков коммутации нелинейностей, с первыми выходами соответствующих генераторов переменных коэффициентов и с входом задания количества сомножителей в нелинейности устройства, первый вход блока управления подключен к входу задания количества сомножителей в нелинейности устройства, выходы блоков вычисления числовых значений производных произведения переменных и первый выход генератора правой ,части соединены с соответствующими входами сумматора, информационные входы -генераторов переменных коэффициентов и генератора правой части соединены с входами шагаг постоянных коэффициентов и начальных условий генераторов устройства, вторые выходы которых соединены с соответствующими(п+1)-ми входами элемента И, выходы элементов И с первой по п-ю группы соединены с соответствующими выходами производных и функции устройства, с первыми информационными входами соответствующих регистров начальных условий по производным и функции, выходы которых соединены с вторыми входами соответствующих накопителей значений производных и функции положительного аргумента и с третьими информационными входами соответствующих регистров производных и функции, второй и третий входаа накопителя значений функции от-. рицательного аргумента соединены соответственно с выходом регистра начальных условий по функции и с выходами элементов I-C первой группы, выход накопителя значения функции отрицательного аргумента соединен с информационным входом регистра предыдущего значения частичной суммы, выход которого подключен к информационным входам элементов И (п+2)-й группыj выходы которых подключены ко второму информационному входу схемы сравнения, выход регистра шреднщущёго значения функ- . ции подключен к информационным вхо- дам элементов И (п+3)-й группы, выходы которых подключены к третьему г информационному входу схемы сравнения, управляющие входы элементов И (п+2)-й и(п+3)-й групп подключены соответственно к нулевому и единичному выходамтриггера контроля, единичный вход которого, второй- управляющий вход накопителя значений функции отрицательного аргумента, первые управляющие входы регистров начальных условий по производным и по фу-нкции, управляющие входы элементов И групп с первой по {п+1)-ю, утгравляющий вход регистра предпредыдущего значения функции, первый управляющий вход регистра предыдущего значения функции, вторые управляющие входы регистров производных и регистра функции, второй вход бло ка управления и первый установочный вход пересчетной схемы подключены к выходу элемента И, (Ы-2)-й вход которого соединен с выходом схемы сравнения, первый управляющий

вход схема сравнения соединен с выходом уЗла контроля нуля, вход которого /соединен с выходом блока вычисления членов ряда Тейлора отрицательного аргумента, нулевой вход триггера контроля, третьИ-управляющие вход регистров производных и функции, вторые управляющие входы накопителей значений производных и функции положительного аргумента, третий.управляющий вход накопителя значения функции отрицательного аргумента, второй управляющий вход регистра приращения аргумента, первый управляющий вход блока задания аргумента, третий вход блока управления соединены с выходом пересчетной схемы, второй информационный вход регистра предыдущего значения функции, вторые информационные входы регистров началных условий по производным и по функции, третьи входы накопителей значений производных и функции положительного аргумента, четвертый вход накопителя значения функции отрицательного аргумента, четвертые информационные входы регистров производных и функции, а также информационный вход блока задания интервала аргумента и информационный вход регистра приращения аргумента соединены с входом заданий начальных условий, границ ийтервала и шага устройства, четвертый вход блока управления соединен с первым выходом блока задания интервала арх умента, второй выход которого подключен к ,информационным входам элементов И (п+1)-й группы, В1ЛХОДЫ которых соединены с выходом аргумента устройства, первый выход блока управления соединен со вторым управляющим входом схемы сравнения, с управляющим входом регистра предыдущего значения частичной суммы, .четвертый выход блока управления, сое динен со вторым установочным входом пересчетной схемы, пятый выход блока управления соединен со вторыми управляющими входами регистров начальных условий по проиэводнь1м и по функдии, со вторым управляющим входом региЪтра предыдущего значения функции, со вторым нулевым- входом триггера контроля, шестой выход блрка управления соединен со вторым управляющим входом блока задания интервала аргумента.. Кроме того, первый, второй третий, четверти, пятый и седьмой выходы блрка управления, а также выход элемента И и выход пересчетной схелфл соединены соответственно с управляющими входами генераторов. Переменных коэффициентов и генератора правой части, седьмой выход блока управления соединен с управляющими входами блоков коммутации нелинейностей, с управляющими входами блоков вычисления числовых

значений производных произведений переменных, с входом пересчетной схемы..

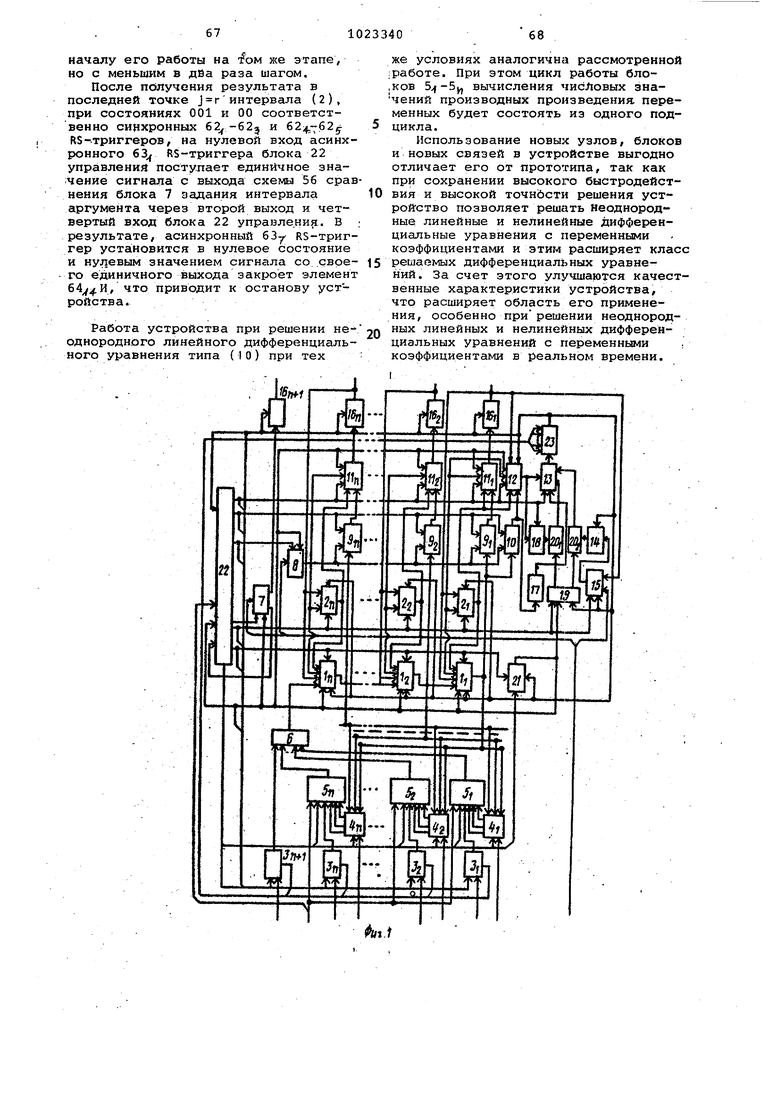

При этом каждый генератор переменных коэффициентов и генератор правой части содержат су1иматор, регистр приращения аргумента, р блоков вычисления членов рядов Тейлора положительного аргумента и блок вычисления членов ряда Тейлора отрицательного аргумента, накопитель значения 1ФУНКЦИИ и р-1. накопителей значений производных положительного аргумент та, накопитель значения функции отрицательного аргумента, схему сравнения, регистр предпрёдыдущего значения функции и регистр предыдущего значения функции, р+2 групп элементов И, p-l регистров производных и регистр функций, р-1 регистров начальных условий по производным и регистр начальных условий по функции, р регистров постоянных коэффициентов, р узлов умножения, регистр предьщу-, щегозначения частичной суммы, узел,

контроля, нуля, триггер контроля,

причем регистры производных и функций соединены последовательно, выход i-ro (где ,3,...,p) регистра подключен к первому информационному входу (i-1)-го регистра, выход каждого регистра производных и регистра функции соединен с первым входом соответствующего блока вычисления членов рядов Тейлора положительного .аргумента и с первым входом соответствующего узла умножения, второй вход которого соедивен с выходом соответствующего регистра постоянных коэффициентов, вых:од5л узлов умножения соединены с соответствующими входами сумматора, ---выход которого соединен с первым ивформационным входом регистра (р-1)-й производной, выходы блоков вычисления членов рядов:Тейлора положительного аргумента со второго по р-й, . соединены с первыми входами соответствующих накопителей значений производных положительного аргумента, а выход первого блока вычисления членов ряда Тейлора соединен с первым входом накопителя значения функНИИ положительного аргумента, выход регистра функции соединён с первым входом блока вьиисления членов ряда Тейлора отрицательного аргумента, выход которого соединен с первым входом накопителя значения функций отрицательного аргумента, выходы накопителей значений производных и функции положительного аргуменфа подключены соответственно к информационному входу элементов Игрупп , J с первой по р-ю,выходы, которых сое-; динены со вторыми информационными входами соответствующих регистров .производных и функции и с первыми нн ;-фррмационными входами соответствую,щих регистров начальных условий .по производным и по функции, выходы которых соединены со вторыгда входами соответствующих Накопителей значений производных и функции положительного аргумента и с третьими информационными входами соответствующих регистро.в производных и функции, второй и третий входы накопител значения функции отрицательного -аргумента соответственно соединены с выходом регистра начальных условий по функции и с выходом элементов И первой группы, выход накопителя значения функции отрицательного аргумента соединен с .первым информационным входом схемы сравнения и с информационным входом регистра предыдущего значения частичной суммы, выход которого подключен к информационным входам элементов И (р+1)-й группы, выходы которых подключены ко второму -информационному вх.оду схе|мы сравнения, выходы элементов И группы подключены к первому информационному входу разрядов регистр ;предыдущего значения функции, выход которого соединен с информационным входом регистра предпредыдущего значения функции, выход регистра предпредыдущего значения функции подключен к информационным входам элементов И (р+2)-и группы, выходы которых подключены к третьему информационном входу схемы сравнения, управлякадие входы элементов И (р+Т)-й и (р+2)-й групп ссютветственно подключены к нулевому и единичному выходам триггера контроля, первый управляющий вход схемы сравнения соединен с выходом узла контроля нуля, вход которого соединен с выходом блока рычисления членов ряда Тейлора отрицательного аругмента, вторые входы блоков вычисления членов рядов Тейлора положительного аргумента и блока вычисления членов ряда Тейлора отрицательного аргумента соединены с выходом регистра приращений аргумента, информационный вход регистра приращения аргумента, информационные входы регистров постоянных коэффициентов, второй информационный вход регистра предащущего значения функции, вторые инфОЕшациьнные входа регистров начальных условий по производным и по функции, третьи входы накопителей значений производных и функции положительного аргумента, четвертый вход накопителя значений функции отгрицательного аргумента, четвертые информационные входы регистров про-изводных и функции подключены к информационному входу генератора, первые управляющие эходы накопителей ;значений,производных положительного :аргумента, значений функции положи- I тельного, аргумента, значения функции отрицательного аргумента, второ управляющий вход схемы сравнения, управляющий вход ре.гистра предыдуще го значения частичной суммы, управл ющие входы блоков вычисления членов рядов Тейлора положительного аргумента и блока вычисления членов ряда Тейлора отрицательного аргумента первый управляющий вход регистра приращения аргумента, первые управляющие входы регистров производных и регистра функции, первые управляющие входы регистров начальшапс условий по- производным и по функции, первый нулевой вход триггера контроля, первый управляющий вход регис ра предыдущего значения функции, уп равляющие входы узлов умножения, управляющие входы регистров постоян ных коэффициентов, а также единичны вход триггера контроля, второй упра ляющий вход регистра предыдущего значения функции, управляющий вход регистра предпредыдущего значения .функции, второй управляющий вход накопителя значения функции отрицательного аргумента, управляющие входы элементов И групп с цервой по р-ю, вторые управляющие входы регистров производных и регистра функ ции, вторые управляющие входы регистров начальных условий по проИзводным и по функции, второй нулевой вход триггера контроля/ третьи управляющие входы регистров производных и функции, вторые управляющие входы накопителей значений производных и функции положительного аргумента, третий управляющий вход накопителя значения функции отрицательного аргумента, второй управляю щий вход регистра приращения аргуме та соединены с управляющим входом генератора, выход регистра функции подключен к первому выходу генерато ра, выход схеМы сравнения подключен ко второму выходу генератора. Кроме того, блок вычисления числовых значений производных произведения переменных, количество которы равно 1+- (гдеО 1,2,.. . ,q), а порядок Производных равен i (где , 1,2, ,. . , k- 1 ), содержит k-q регистро первых сомножителей и их производны -й (где i l7-k) строки л)-го (где ) столбца, (k-l)-q регистров вторых сомножителей и их произволных i-й (где ) строки (где ) l4q} столбца и регистр вторы сомножителей и их производных первой строки первого столбца, k-1 регистров коэффициентов, k-2 двухвход вых сумматоров коэффициентов, k-2 первых узлов умножения, k вторых узлов умножения, k-входовый сумма-, тор, группу элементов И, регистр количества сомножителей в нелинейности, причем выходы каждых предыдущего и последующего регистров коэффициентов подключены к входам соот- ветствующего двухвходового думматора коэффициентов, выход которого подключен к информационному входу того же последуюйдего регистра, выходы регистров коэффициентов, за исключением выхода первого регистра коэффициентов, соединены с первыми входами соответствующих первых узлов умножения, вторые входы которых соединены с выходами регистров первых сомножителей и их производных первого столбца соответст вующей 1 -и (где ) строки, при этом выходы регистров первых сомножителей и их производных первого столбца i-й (где ) строки соединены с первыми информационными входаг м регистров первых сомножителей и их производных всех q столбцов соответственно той же i-й строки, выхода регистров первых сог/шожителей и их производных -го (где л) 2,3, ...,q ) столбца каждой i-и (где i 14-k) строки . соединены со вторыми информационными входами регистров первых сомножителей и их производных (i) -1 )-го столбца той же каждой i-й строки,- третьи информационные входы регистров первых сомножителей и их производных 1-го, 2-го, ..., q-ro столбцов всех i (где i 1-;-k) строк подсоединены к соответствующим входам производных и функции блока, выходы первых узлов умножения и выходы регистров первых сомножителей и их производных первой и k-й строк первого столбца соединены, с первыми входами соответствующих |узлов умножения, вторые входы которых соединены с выходами соответствующих регистров вторых сомножителей и их производных первого столбца t-и (где ) строки и регистра вторых сомножителей и их производных первого столбца первой строки, выходы узлов умножения соединены с входами k-входового сумматора, выход регистра вторых сомножителей и их производных первого столбца первой строки и выходы регистров вторых сомножителей и их производных первого столбца i-й (где J 2-f-k-1 ) ;строки соединены с первыми информационными входами регистров вторых сомножителей и их производных всех q столбцов последующей i+1 строки, выходы регистров вторых сомножителей и их производных )-го (где 2,3,,..,q) столбца каждой i-й (где )cTpoKH соединены со вторыми информационными входами регист-: ров шторых сомножителей и их производных (л -1 )-го столбца той же каждой i-й строки, первый и второй инфор Мационные входы регистра вторых сгомножителей и их производных первой

строки первого столбца соответственно соединены с входом переменного коэфг фициента блока и с выходом k-входового сумматора, при этом выход k-sxc дового сумматора подключен к входу группы элементов И, выход которой соединен с выходом блока, первые управляющие входы регистров первых сомножителей и их производных 1-го 2-го, ..., q-ro столбцов t-X, где i 1-r-k) строк и регистров вторых со- 0 множителей и их производных 1-го, 2-го,..., q-ro столбцов -х (где строк соединены с соответствующими выходами регистра количества сомножителей в нелинейности, вход - tS которого соединен с входом количества сомножителей в. нелинейности бло-г ка, первый управляющий вход регистра вторых сомножителей и их производных первой строки первого столбца, 20 вторые управляющие входы регистров первых .сомножителей и их производных и регистров вторых сомножителей и их производных; синхронизирующие входы регистров первых сомножителей 25 и их производных, регистров вторнхУ сомножителей и их производных и -регистров коэффициентов, за исключе- ; нием-первого регистра коэффициентов, третьи управляющие входы регистров ,« первых сбмножителей и их производ- ных, управляющий вход группы элементов И, .управ лякидие входы первых и вторых узлов умножения соединены с управляющим входом блока. чс Причем блок задания интервала . .аргумента содержит регистр приращения аргумента, сумматор, регистр значения аргумента: в начале интервала, регистр значения аргумента в конце интервала, схему сравнения, . 40 п)ричем первый вход сумматора соединен с выходом регистра приращений аргумента,; информационный вход которого соединен с информационным вхо-дом блока, второй вход сумчатора 45 и его выход соединены соответствен-. : но с выходом и первьш информационным входом .регистра значения аргумента в начале интервала, при этом ВЫХОДрегистра значения аргумента JO в начале интервала соединен с первым выходом схемы сравнения, второйвход КОТОРОЙ соединен с входом ре- Ч гистра значения аргумента в конце интервала, соот ветственно подключё- ны к первому и второму входам схе- KOI сравнения, второй информационньай вход регистра значения аргумента в . начале интервала и информа:ционный вход регистра значения аргумента в конце интервала соединены с инфор- й мационным входом блока, первый ynpaiaляиадий вход регистра приращения ар гумента и первый управляющий вход регистра значения аргумента в начале интервёша соединены с первым управ 65

ляющим входом блока, второй управляющий вход регистра приращения аргумента, второй управляющий вход регистра значения аргумента в начале интервала и управляющий вход регистра значения аргумента в конце интервала, третий управляющий вход регистра приращения аргумента и третий ;управляющий вход регистра значения аргумента в начале интервала соеди|нены со вторым управляющим входом |блока, первый выход блока соединен с выходом схемы сравнения, второй выход блока соединён с выходом регистра значения аргумента в начале интервала.

Кроме того, блок вычисления членов ряда ТейЛора содержит регистр узел деления, первый узел умножения, второй узел умножения, причем выходы первого ysjla умножения и регистра соответственно соединены с первым информационным входом регистра и с входом делимого узла деления, выход которого соединен с первым входом первого узла умножения и с первым входом.второго узла умножения, второй вход и выход которого .соответственно соединены с первым входом и выходом блока, второй вход первого узла умножения и второй .информационный вход регистра соединены со BTOpfcJM входом блока-, вход делителя узла деления, управляющий вход регистра, управляющий вход узла деления, управл5аощие входы первого и второго узлов умножения соединены с управляющим входом блока.

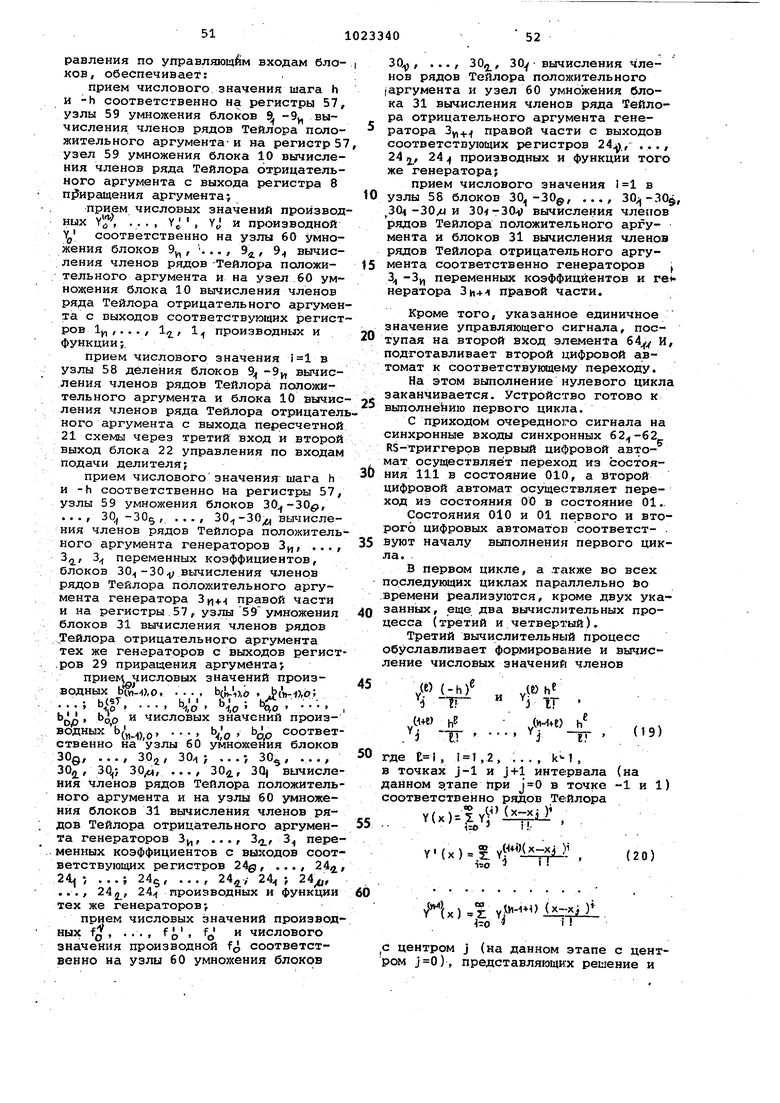

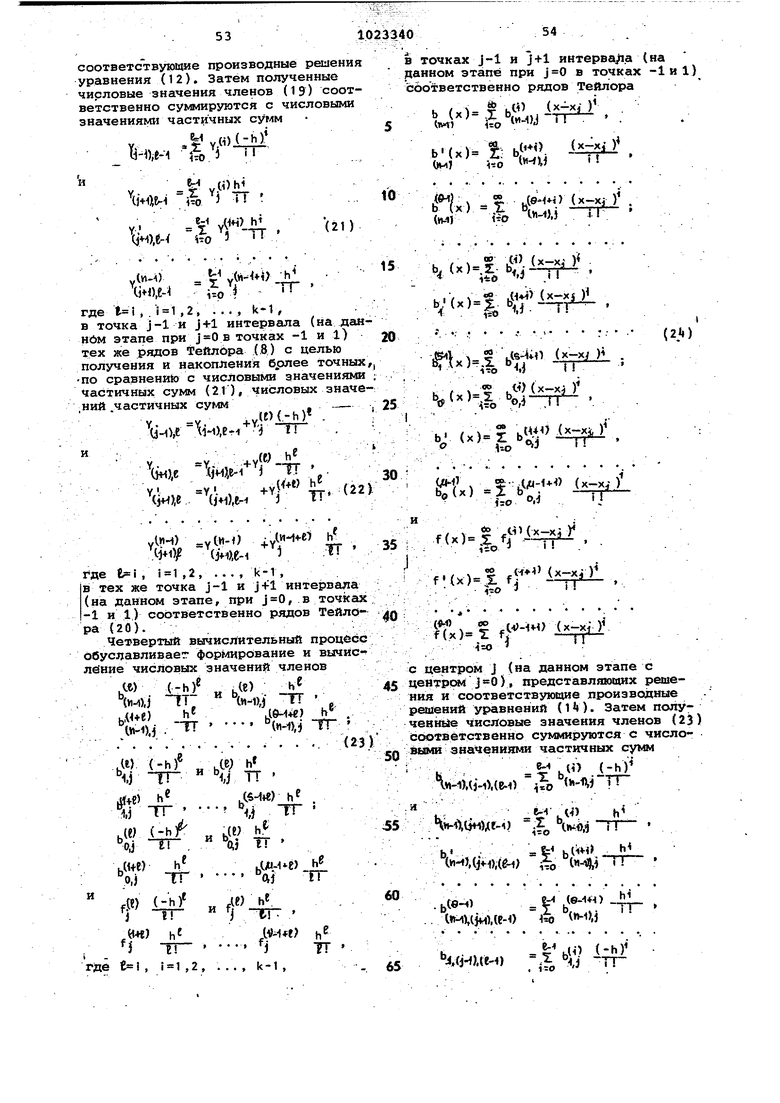

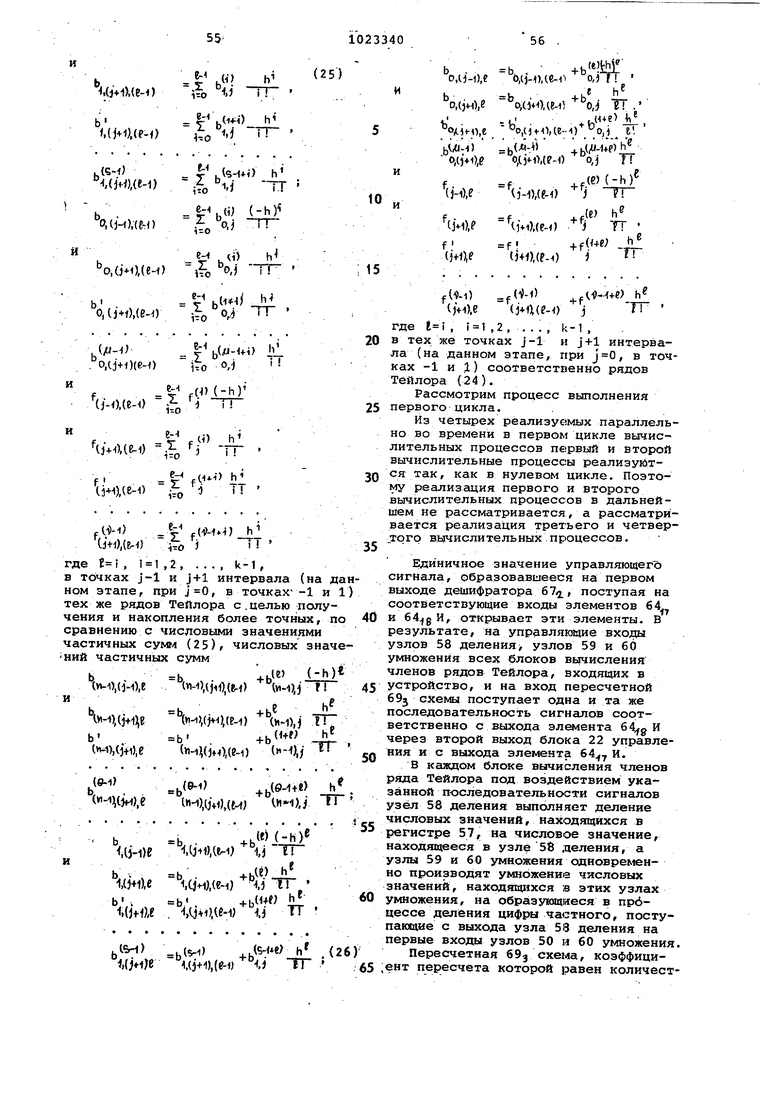

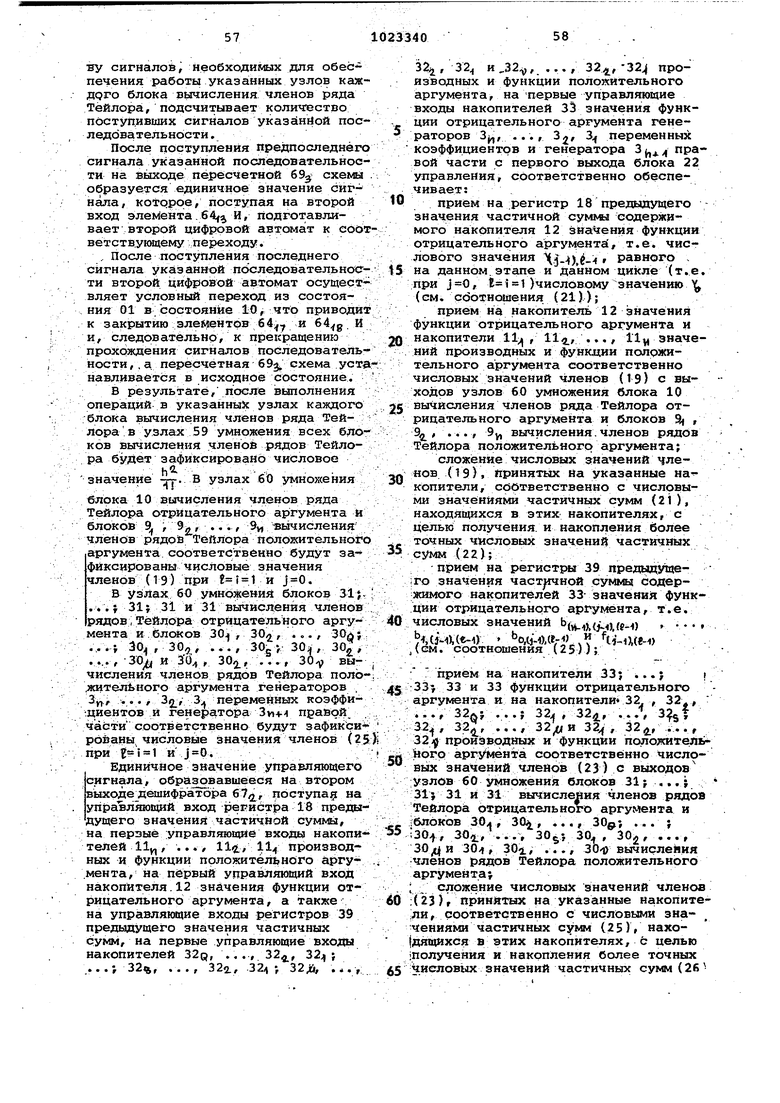

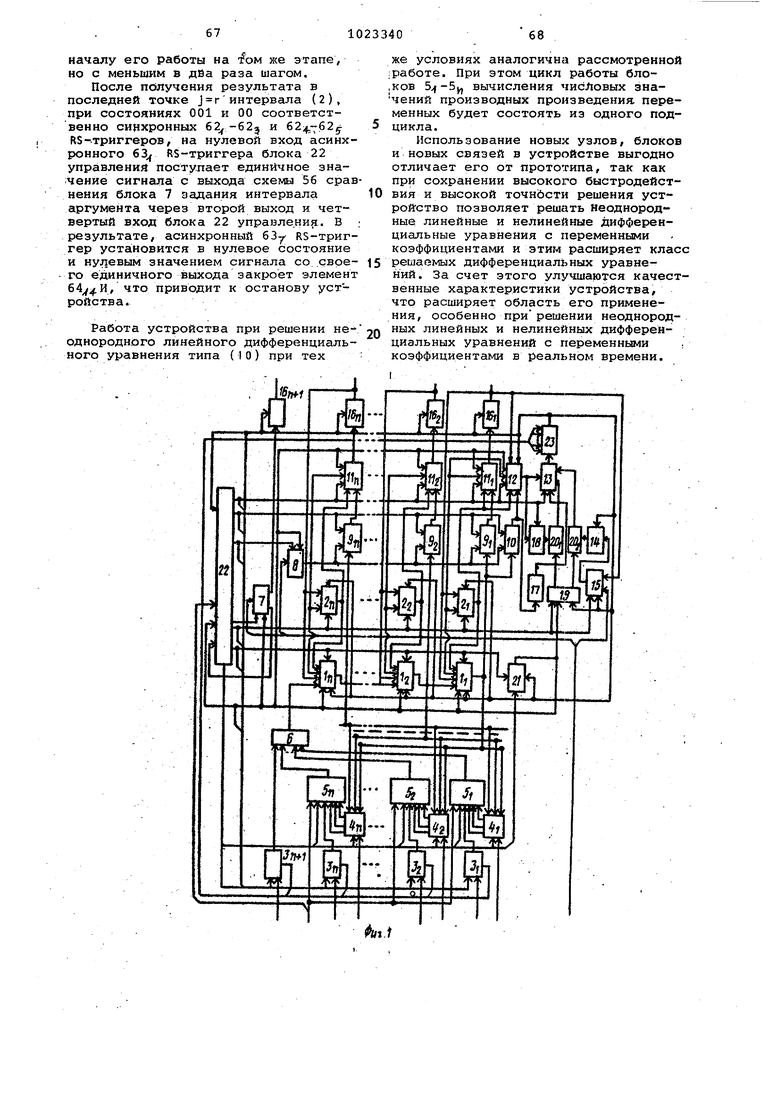

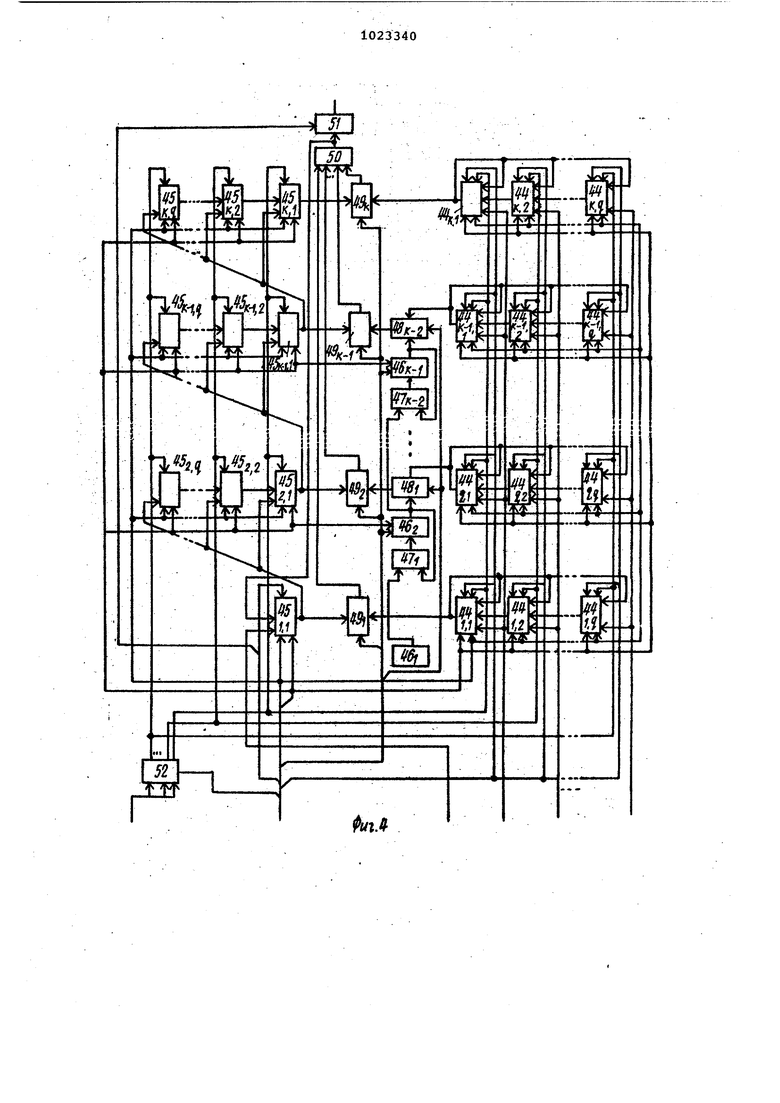

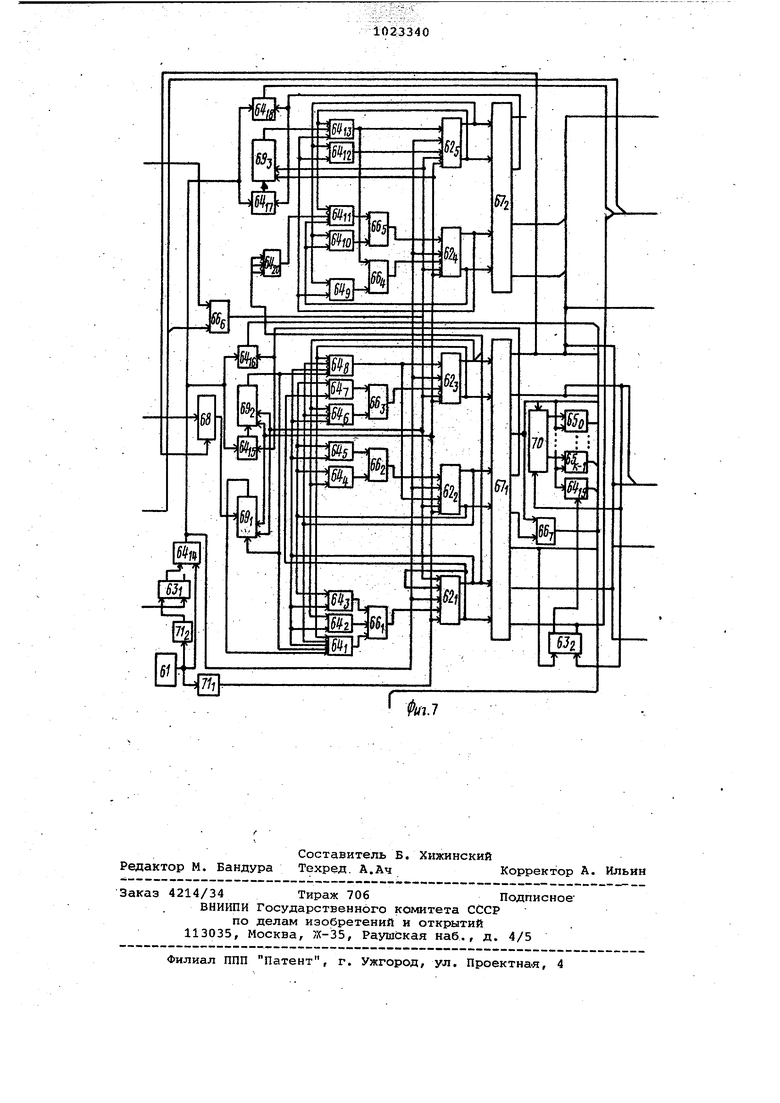

Блок управления содержит генератор тактовых импульсов, пять синхронных RS-триггеров, два асинхронных RS-триггера, девятнадцать элементов И, группу элементов И, семь элементов ИЛИ, два дешифратора, регистр с единйчньм кодированием, три цересчетные схемы, кольцевой счетчик кнопку Исходное состояние, кнопку Пуск, причем единичный выход первого синхронного RS-триггера соединен с первыми входами первого, втоюого, третьего, пятого, шестого, росьмого элементов И, а нулевой вы|ХОД.соединен с его единичным синхрон:ным входе КС первым входом седьмо1ГО элемента И, единичный выход вторюго синхронного RS-триггера соединен ;Со вторыми входами первого, шестого, восьмого элементов И, а нулевой выход соединен с первым входом четвертого элемента И и вторыми входами третьего, пятого и седьмого элементов И, единт1ный выхсдц третьего синхронногб К§-триггера соединен со гвторыми входами второго элемента И, .четвертого элемента И и с третьим 1входом шестого элемента И, а нулевой выход - с третьими входами первого восьмого элементов И, выходы первог второго, третьего элементов И подкл чены к соответствующим входам перво го элемента ИЛИ, выход которого сое динен с нулевым синхронным входом первого синхронного ftS-триггера, выходы четвертого и пятого элементов И подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с единичным синхронным входом второго синхронного RS-триггера, выходы шестого и седьмого элементов И подключены к соответствующим входам третьего элемента ИЛИ, выход которого соединен с нулевым синхронным входом третьего синхронного. RS-триггера, выход вось мого элемента И соединен с нулевым и единичным синхронными входами соответственно второго и третьего синхронных RS-триггеров, единичный выход четвертого синхронного RS-три гера соединен с первыми входами девятого, двенадцатого и тринадцатого элементов И, а нулевой выход соеди- нен с первыми входами девятого и одиннадцатого элементов И, единичный выход пятого синхронного RS-три гера соединен со вторыми входами девятого, десятого и двенадцатого элементов И, а нулевой выход соединен со вторыми входами одиннадцатого и тринадцатого элементов И, вы ходы девятого и тринадцатого, десятого и одиннадцатого элементов И соответственно подключены к соответ ствующим входам четвертого и пятог элементов ИЛИ, выходы которых соответственно соединены с нулевым и ед ничным синхронными входами четверто синхронного RS-триггера, выходы две надцатого и тринадцатого элементов соответственно соединены с нулевым и единичным синхронными входами пятого синхронного RS-триггера, первы нулевые асинхронные входы первого, второго, третьего, четвертого и пятого синхронных RS-триггеров соединены с выходом кнопки Исходное сос тояние , вход которой соединен с выходом генератора тактовых импульсов, единичный асинхронный вход пер вого синхронного RS-триггера-и втор нулевые асинхронные входы второго, третьего, четвертого и пятого синхронных RS-триггеров соединены с вы ходом шестого элемента ИЛИ, синхронизирующие входы первого, второго, третьего, четвертого и пятого синхронных RS-триггеров соединены с выходом четырнадцатого элемента И, первый и второй входы которого соот ветственно соединены с выходом гене ратора тактовых импульсов и с единичным выходом первого асинхронного RS-триггера, единичный вход которог подключен к выходу кнопки Пуск, вход которой соединен с выходом генератора тактовых импульсов, выходы первого, второго и третьего синхронных RS-триггеров подключены к входам первого дешифратора, а В1лходы четвертого и пятого синхронных RS-триггеров подключены к входам второго дешифратора, нулевой выход первого дешифратора соединен с управляющим входом регистра с единичным кодиро ванием, первый выход первого дешифратора соединен с установочным входом кольцевого счетчика и с нулевым входом второго асинхронного RS-триггера, второй выход- первого дешифратора соединен с первыми входами К элементов И группы элементов И, с первыми входами седьмого элемента ИЛИ, девятнадцатого элемента И и с входом кольцевого счетчика, третий выход первого дешифратора соединен с первыми входагли пятнадцатого и шестнадцатого элементов И, вторые входы которых соединены с выходом четырнадцатого элемента И, четвертый выход первого дешифратора соединен со вторым входом седьмого элемента ИЛИ, пятый выход первого дешифратора соединен с единичным входом второго асинхронного RS-триггера, единичный выход которого соединен со вторым входом девятнадцатого элемента И, седьмой выход первого дешифратора соединен с третьим входом, одиннадцатого элемента.И, выход регистра с единичным кодированием соединён с входом установки коэффициентов пересчета первой пересчетной схемы, вход которой соединен с выходом второй пересчетной схемы,вход второй пересчетной схемы соединен с выходом пятнадцатого элемента И, кроме того, выход второй пересчетной схемы соединен с четвертыми входами первого и восьмого элементов И, а зыход первой пересчетной схемы соединен с пятым входом первого элемента И, установочные входы первой, второй и третьей пересчетных схем соответственно соединены с выходом кнопки Исходное состояние и с выходом шестого элемента ИЛИ, первый выход второго дешифратора соединен с первыми входами семнадцатого и восемнадцатого элементов И, вторые входы которых соединены с выходом четырнадцатого элемента И, выход семнадцатого элемента И соединен с входом третьей пересчетной схемы, выход которой соединен с третьим входом тринадцатого элемента И, к первому входу блока подключен информационный вход регистра с единичным кодированием, ко второму входу блока подключен первый вход шестого элемента ИЛИ, к третьему вхрду блока подключен второй вход шестого элемента ИЛИ и -второй выход блока,-к четвертому входу блока подключен нулевой вход первого асинхронного RS-триггера, кпервому выходу блока подключены jiyлевой йыход первого дешифратора, второй, и т ретий выходаа второго децш ратора, ко второму выходу блока под ключены третий вход блока, седьмой выход первого дешифратора и выход восемнадцатого элемента И, к третьему выходу блока подключен нулевой выход; первого дешифратора, к четвер тому выходу блока подключены нулево и шестой выходы первого дешифратора к пятому выходу блока подключен нулевой выход первого дешифратора, к шестому выходу блока подключены нулевой и первый выходы первого дешифратора, к седьмому, выходу блокаподключены нулевой, первый, второй и пятый выходы первого дешифратора, выходы k элементов И группы, выходы седьмого элемента ИЛИ, шестнадцатогои девятнадца,того элементов И и выход первой пересчетной схемы. | i .,-.-. На фиг. 1 представлена структурнал схема устройства для. решейия ди ференциальных уравнений; на фиг. 2 структурная схема примера реализаци генераторов 3 -Зу, переменных коэффициентов и генератора Зц. правой части; на фиг. 3 - то же, блоков Д,-4у, коммутации нелинейностей-, на фиг. 4 - то )ке, блоков 5у,-5J, вычисления числовых значений производных произведения переменных) на фиг. 5 то же, блока задания и контроля интервала изменения аргумента) на фиг. б - то же, блоков 9;, -9 вычисления членов рядов Тейлора положите ного аргумента и блока Ю вычислени членой ряда Тейлора отрицательного аргумента; на фиг. 7 - то же, блока 22 управления. Устройство для регаения дифференциальных уравнений (фиг. 1) содерЖит регистр. функции и регистры . , производных, регистр 2 начая ных условий по функции и регистры начальных условий по производ НЕдм, генераторы 3, -Зу1 переменных ко фициентов, генератор Зун-у правой части, блоки 4j, -4 коммутации нелинейностей, блоки 5ц -5у, вычисления числовых значений производных произведения переменных, сумматор б, ёлок 7 задания интервала аргумента/ регистр 8 приращения аргумента, блоки 9 -9 вычисления членов рядов Тейлора положительного аргумента, блок 10 вычисления членов ряда ТейЛора отрицательного аргумента, накопитель lij значения функции и на.копители llj-11 у, значений производных положительного аргумента, накопитель 12 значения функции отрицательного аргумента, схему 13 cpag неНия, регистр 14 предпредыдущего значения функций, регистр 15 предыдущего значения функции, группы ,, элементов И, группу 16, элемен тов И, узел 17 контроля нуля, регистр 18 предыдущего значения частичной суммы, триггер 19 контроля, группы 20 -и 202. элементов И, пересчетную 21 схему, блок 22 управления, ялемент 23 И. Регистры lyj;- производных и регистр 1; функции соединены последовательно: .выход i-ro (где ,3,..., ft) регистра подключен к первому информационному входу (i-1)-го регистра. К выходам регистров , производных и регистра 1 функции подключены входы производных и функции блоков 4 -4у коммутации нелинейностей, входы номеров регистров произвсданых и регистра функции которых соединены с соответствующими входами номеров регистров производных и регистра функций устройства. Входы производных и функции, вход переменного коэффициента и вход количества сог«Ю5хителей в нелинейности блоков вычисления числовых значений производных произведения переменных соответственно соединены с выходагли соответствующих блоков 4 -4 кoм JIyтaции нелинейностей, с первыми выхоДаг-ш соответствукидих генераторов , переменных коэффициентов и с входс л задания коли|чества сомножителей в нелинейности устройства. Первый вход блока 22 :управления подключен к входу задания количества сомножителей в нелинейности устройства. Выходы блоков 5 -5у, вычисления числовых зн.ачений производных произведения переменных и первый выход генератора Зу правой части соединены с соответствующими входами сумматора 6, выход которого соединён с первыЛ информационным входом регистра 1,,(п-1)-й про- изводной. Информационные входы генераторов Зд-Зу, переменных коэффициентов и генератора 3yi. ц правой части соединены с входами шага, постоянных коэффициентов и начальных услорий генераторов устройства, вторые выходы -которых соединены с соответствующими (п+)-ми входами элемен|та 23 И. Выход каждого регистра ), производных и регистра 1 функции соединен с первым входом соответртвующего блока 9 -9у, вычисления чле-тнов ряда Тейлора положительного аргу--мента, выходы каждого из которых со второго по п-й соединены с первым входом соответствующего накопителя , значений производных положительного аргумента, а выход первогос первым входом накопителя 11) зна- , .ения функции положительного аргу-

мента. Выход каждого накопителя 114 -Ни значений производных и зна- чения функции положительного аргумента подключен к информационным входам элементов И соответствувадей группы 16j -16j,,. выходы которых соединены со -вторыми информационными входами соответствующих регистров производных и функции. Выход регистра 1 функции соединен с первым входом блока 10 вычисления членов ряда Тейлора отрицательного аргумента, . выход которого соединен с первым входом накопителя 12.значения функции отрицательного аргумента. Выходы элементов И группы 16 подключены к информационному входу соответствующих разрядов регистра 15 предыдущего значения функции, выход которого соединен с информационным входом регистра 14 предпредыдущего значения функции. Первый информационный вход схемы 13 сравнения соединен с выходом накопителя 12 значения функции отрицательного аргумента. Вторые входы блоков 9 -9 вычисления членов рядов Тейлора положительного аргумента и второй вход 10 вычисления членов ряда Тейлора отрицательного аргумента соединены с выходом регистра 8 приращения аргумента. Выходы элементов И групп 16 -1б( элементов И соединены с соотвeтcтвyющи ttl выходами производных и функции устройства, с первыми информационными входами соответству1ощи регистров начальных условий по производным и по функции, выходы которых соединены со вторьзми входами соответствующих накопителей 11 -Ни значений производных и функции положительного аргумента и с третьими ин формационными входами соответствующих регистров 1у,-1 производных функции. Второй и третий входы накопителя 12 значения функции отрицательного аргумента соединены соответствен но с выходом регистра 2 начальных условий по функции и с выходом элементов. И группы 16 элементов И. Выход накопителя 12 значения функции отрицательного аргумента соединен с информационным входом регистра 18 предыдущего значения частичной суммы, выход которого подключен к информационный входам элементов И .группы 20 элементов И, выходы которых подключены ко в;торому информациейному входу схемы 13 сравнения. Вмход регистра 14 предпредьщущего значения функции подключен к информационным входам элементов И группы 20 элементов И, выходы которых подключены к. третьему информационному входу схемы 13 сравнения. Управ;Ляющие входы элементов И групп 20 и 2От. элементов И подключены соответственно -к нулёвому и единичному