,1

Изобретение относится к технике связи, в частности к устройствам обеспечения синхронного запуска приемной и передающей аппаратуры.

Известно устройство, обеспечивающее определение фазирующей посылки с помощью сравнения информации из канала связи с вставленными в нее через определенный цикл посылками фазирования, сформированными на рекуррентной линии задержки, поступающей на рекуррентный анализатор и блок сравнения с проверочными символами с выхода рекуррентного анализатора 1.

Наиболее близким техническим решением к предлагаемому является устройство цикловой синхронизации в системах передачи цифровой информации, содержащее приемник бинарного сигнала, -выход которого соединен с первым входом блока сравнения непосредственно, а с входом узла блокировки через рекуррентный анализатор, второй выход которого подключен к второму входу блока сравнения 2.

Однако известные устройства цикловой синхронизации обладают низкой помехоустойчивостью и больщой вероятностью ложного выделения синхросигнала.

Целью изобретения является повыщение помехоустойчивости и уменьщение вероятности 1ожного выделения синхросигнала.

Для этого в предлагаемое устройство цикловой синхронизации в системах передачи цифровой информации введены первый ц втопои счетчики единиц, формирователь меток времени, инвертор, блок совпадения и формирователь одиночных сигналов, при этом один 1:з выходов формирователя меток времени сое.динен с выходом узла блокировки и с входом «Сброс первого счетчика единиц, а другой выход - с регистрирующим входом первого счетчика единиц и через второй счетчик единиц с одним из входов блока совпадения, к другому входу которого подключен выход первого счетчика единиц, а выход блока совпадения через формирователь одиночных сигналов подк.тючен к дополнительному входу рекуррентного анализатора, кроме того, счетньн выход формирователя меток времени подключен к соответствующему входу формирователя одиночных сигналов, а выход блока сравнения подключен через инвертор к счетным входам первого и второго счетчиков единиц.

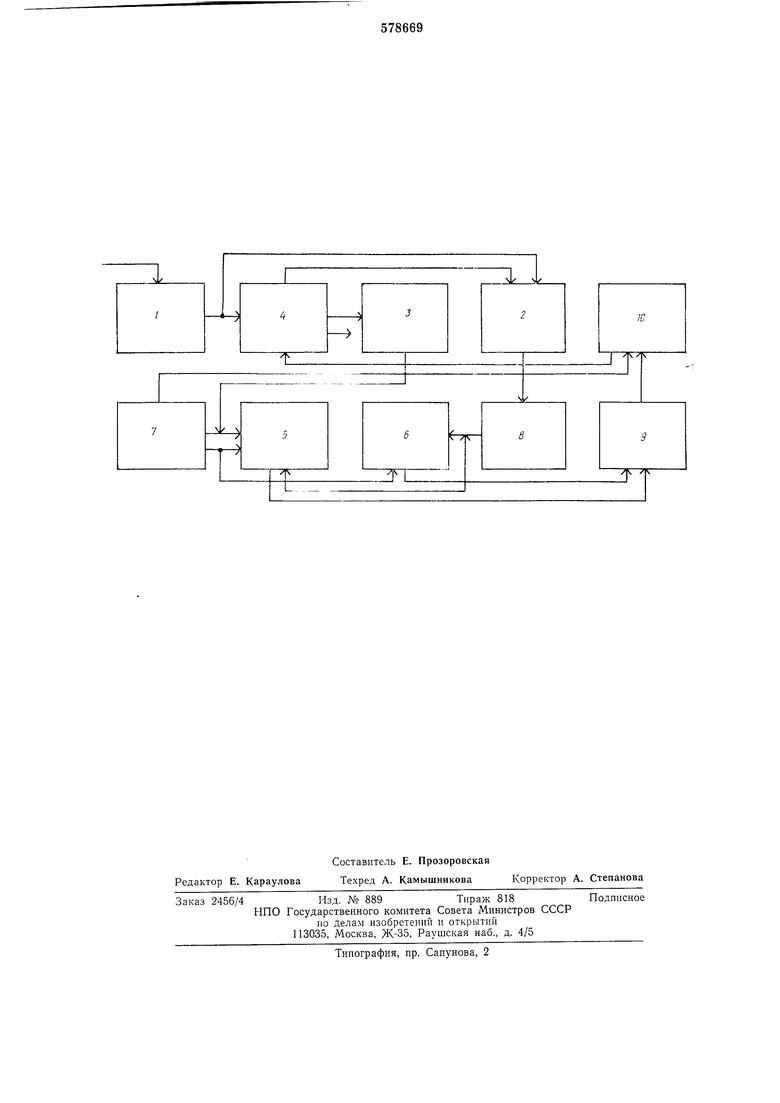

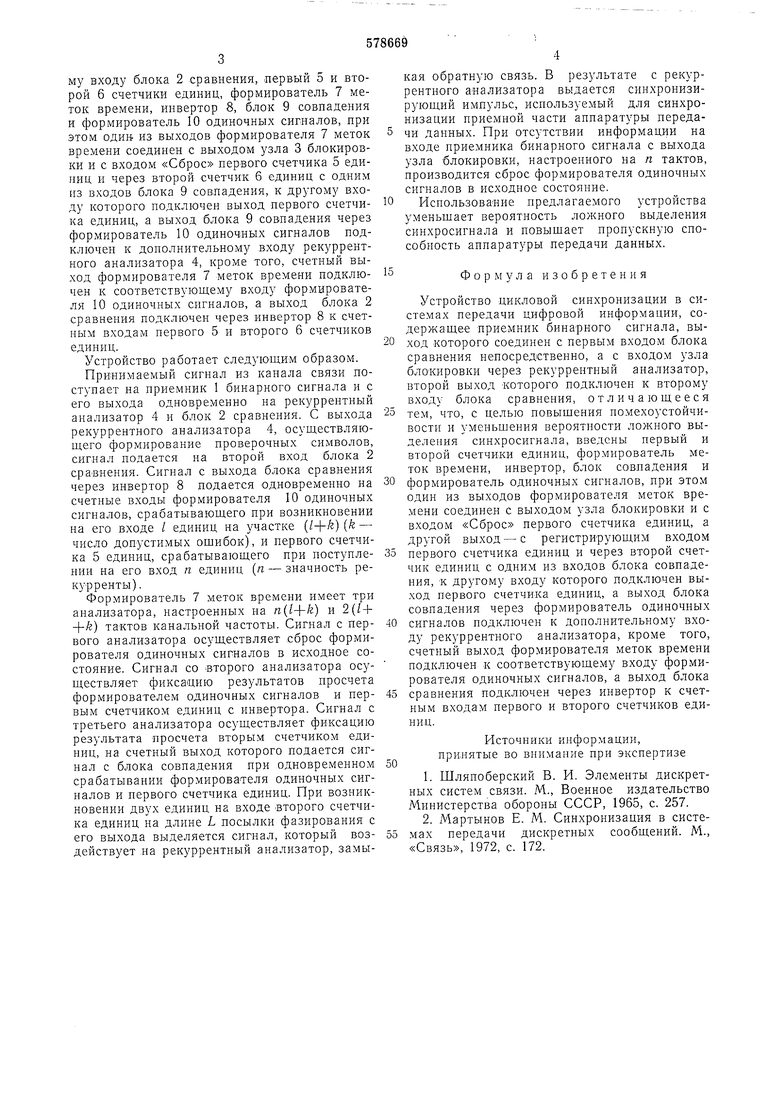

На чертеже приведена структурная электрическая схема иредлагаемого устройства.

Устройство цикловой синхронизации в системах передачи цифровой информашпт содержит приемник 1 бинарного сигнала, выход которого соединен с первым входом блока 2 сравнения непосредственно, а с входом узла 3 блокировки через рекуррентный анализатор 4, второй выход которого подключен к второму входу блока 2 сравнения, первый 5 и второй 6 счетчики единиц, формирователь 7 меток времени, инвертор 8, блок 9 совпадения и формирователь 10 одиночных сигналов, при этом один из выходов формирователя 7 меток времени соединен с выходом узла 3 блокировки и с входом «Сброс первого счетчика 5 единиц и через второй счетчик 6 единиц с одним из входов блока 9 совпадения, к другому входу которого нодключен выход первого счетчика единиц, а выход блока 9 совпадения через формирователь 10 одиночиых сигналов подключен к дополнительному входу рекуррентного анализатора 4, кроме того, счетный выход формирователя 7 меток времени подключен к соответствующему входу формирователя 10 одиночных сигналов, а выход блока 2 сравнения подключен через инвертор 8 к счетным входам первого 5 и второго 6 счетчиков единиц.

Устройство работает следующим образом.

Принимаемый сигнал из канала связи поступает на приемник 1 бинарного сигнала и с его выхода одновременно на рекуррентный анализатор 4 и блок 2 сравнения. С выхода рекуррентного анализатора 4, осуществляющего формирование проверочных символов, сигнал подается на второй вход блока 2 сравнения. Сигнал с выхода блока сравнения через инвертор 8 подается одновременно на счетные входы формирователя 10 одиночных сигналов, срабатывающего при возникновении на его входе / единиц на участке () (k - число допустимых ощибок), и первого счетчика 5 единиц, срабатывающего при иоступлении на его вход п единиц (п - значность рекурренты).

Формирователь 7 меток времени имеет три анализатора, настроенных на n() и 1(1 + ) тактов канальной частоты. Сигнал с первого анализатора осуществляет сброс формирователя одиночных сигналов в исходное состояние. Сигнал со второго анализатора осуществляет фиксацию результатов просчета формирователем одиночных сигналов и первым счетчиком единиц с инвертора. Сигнал с третьего анализатора осуществляет фиксацию результата просчета вторым счетчиком единиц, на счетный выход которого подается сигнал с блока совпадения ири одновременном срабатывании формирователя одиночных сигналов и первого счетчика единиц. При возникновении двух единиц на входе второго счетчика единиц на длине L посылки фазирования с его выхода выделяется сигнал, который воздействует на рекуррентный анализатор, замыкая обратную связь. В результате с рекуррентного анализатора выдается синхронизирующий импульс, используемый для синхронизации приемной части аппаратуры передачи данных. При отсутствии информации на входе приемника бинарного сигнала с выхода узла блокировки, настроенного на п тактов, производится сброс формирователя одиночных сигналов в исходное состояние.

Использование предлагаемого устройства уменьщает вероятность ложного выделения синхросигнала и повышает пропускную способность аппаратуры передачи данных.

о р м у л а изобретения

Устройство цикловой синхронизации в системах передачи цифровой информации, содержащее приемник бинарного сигнала, выход которого соединен с первым входом блока сравнения непосредственно, а с входом узла блокировки через рекуррентный анализатор, второй выход которого подключен к второму входу блока сравнения, отличающееся

тем, что, с целью повыщения помехоустойчивости и уменьшения вероятности ложного выделения синхросигнала, введены первый и второй счетчики единиц, формирователь меток времени, инвертор, блок совпадения и

формирователь одиночных сигналов, ири этом один из выходов формирователя меток времени соединен с выходом узла блокировки и с входом «Сброс первого счетчика единиц, а другой выход - с регистрирующим входом

первого счетчика единиц и через второй счетчик единиц с одним из входов блока совпадения, к другому входу которого подключен выход первого счетчика единиц, а выход блока совладения через формирователь одиночных

сигналов подключен к дополнительному входу рекуррентного анализатора, кроме того, счетный выход формирователя меток времени подключен к соответствующему входу формирователя одиночных сигналов, а выход блока

сравнения подключен через инвертор к счетным входам первого и второго счетчиков единиц.

Источники информации, принятые во внимание при экспертизе

1.Шляпоберский В. И. Элементы дискретных систем связи. М., Военное издательство Министерства обороны СССР, 1965, с. 257.

2.Мартынов Е. М. Синхронизация в системах передачи дискретных сообщений. М.,

«Связь, 1972, с. 172.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации при двоичном сверточном кодировании | 1982 |

|

SU1062881A1 |

| Устройство для определения достоверности передачи двоичной информации | 1975 |

|

SU618857A2 |

| Устройство выделения рекуррентного сигнала с обнаружением ошибок | 1986 |

|

SU1327308A2 |

| Устройство выделения рекуррентного синхросигнала с обнаружением ошибок | 1983 |

|

SU1102050A2 |

| Устройство для выделения рекуррентного синхросигнала | 1983 |

|

SU1116547A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛАМ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1994 |

|

RU2079855C1 |

| СПОСОБ КОДИРОВАНИЯ ИНФОРМАЦИИ ОТРЕЗКАМИ ЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2014 |

|

RU2568320C1 |

| Устройство синхронизации по циклам | 1990 |

|

SU1809543A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

Авторы

Даты

1977-10-30—Публикация

1976-03-22—Подача