1

Изобретение относится к запоминающим устройствам, в частности к постоянным запоминающим устройствам, и может быть использовано в автоматике и вычислительной технике.

Известны накопители для постоянных запомииающих устройств, содержащие группы сердечников, соответствующие разрядам чисел в системе счисления с основанием Р больше 2, с log:; р-разрядными выходными шинами в каждой группе, образованными последовательным соединением выходных щин соответствующих сердечников 1..

Наиболее близким техническим решением к данному изобретению является ячейка памяти для накопителя постоянного запоминающего устройства, содержащая три запоминающих трансформатора, две разрядные выходные щины, между которыми последовательно подключены два резистора, один из выводов первого резистора подключен к первой выходной разрядной шине и к началу выходной обмотки первого запоминающего трансформатора, конец которой подключен к началу выходной обмотки третьего запоминающего траисформато.ра и к концу выходной обмотки второго запоминающего трансформатора, начало выходной обмотки второго запоминающего трансформатора подключено ко второй разрядной шине и к одному из выводов второго резистора, конец выходной обмотки третьего запоминающего трансформатора подключен к шине нулевого потенциала (2.

В известных ячейках памяти для накопителей постоянных запоминающих устройств из-за большой индуктивности последовательно соединенных многовитковых выходных обмоток запоминающих трансформаторов увеличивается постоянная времени вторичных цепей ячейки памяти, что приводит к снижению быстродействия и умеиьшению амплитуды сигналов на выходных разрядных шинах. Эти недостатки снижают быстродействие ячейки памяти и надежность ее работы.

Цель изобретения - повышение надежности и быстродействия ячейки памяти для накопителя постоянного запоминающего устройства.

Эта цеЛь достигается тем, что ячейка содержит третий резистор,один из выввдов которого подключен к шине нулевого потенциала, а второй вывод соединен с концом выходной обмотки второго запоминающего трансформатора и со вторыми выводами первых двух резисторов.

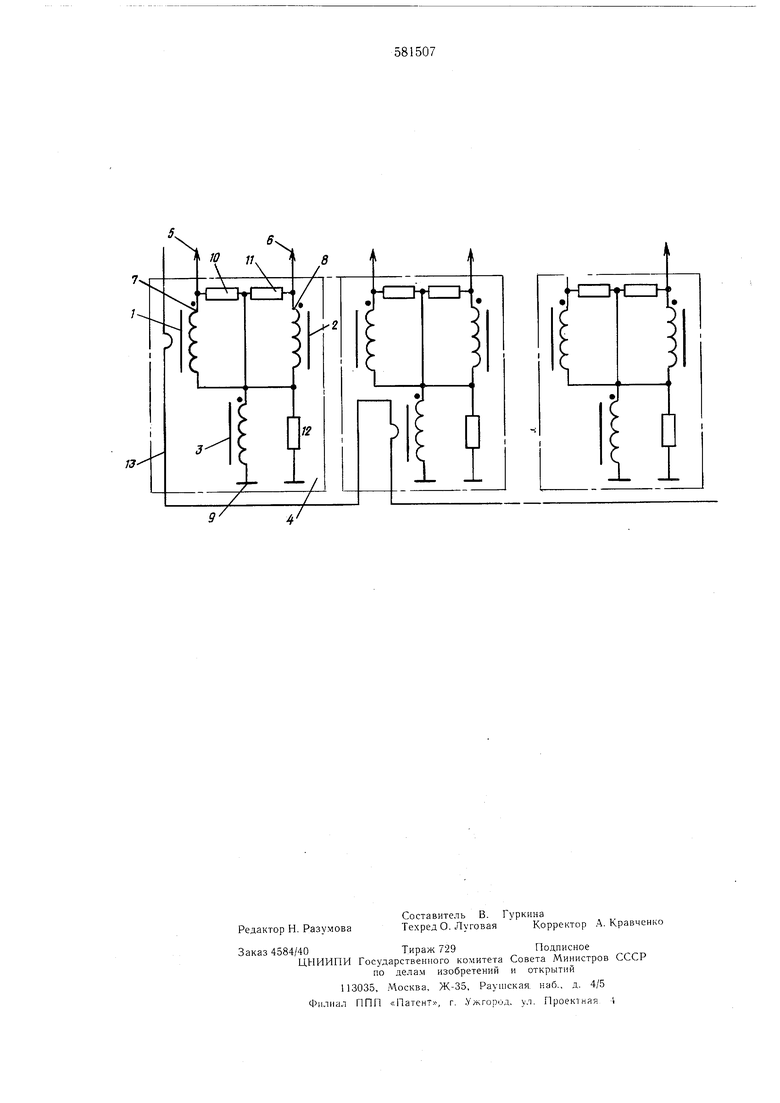

На чертеже изображена электрическая схема ячейки памяти для накопителя постоянного запоминающего трансформатора.

Она содежит три запоминающих трансформатора 1, 2, 3, ячейки памяти 4, две разрядные выходные шины 5, 6, выходные обмотки 7, 8, 9 запоминающих трансформаторов 1, 2, 3 соответственно и резисторы 10, 11, 12, кодовый провод 13.

Ячейка памяти для накопителя постоянного запоминающего устройства работает следующим образом.

При выборе кодового провода 13 по нему протекает ток опроса, и в выходных разрядных щинах 5, 6 ячейки памяти возникают считанные сигналы. При возникновении считанного сигнала в выходной обмотке 9 запоминающего трансформатора 3 он поступает через выходные обмотки 7, 8 запоминающих трансформаторов 1, 2 и резисторы 10, 11 на разрядные выходные щины 5, 6, и на них будет импульсное представление двоичного кода 11. При наличии считанных сигналов в выходных обмотках 7, 8 запоминающих трансформаторов 1, 2 на разрядных выходных щинах 5, 6 будет импульсное представление соответствующих двоичных кодов 01 и 10.

Технико-экономический эффект предлагаемой ячейки памяти для накопителя постоянных запоминающих устройств заключается в том, что она имеет более высокое быстродействие и надежность по сравнению с уже известными ячейками памяти.

Увеличение быстродействия обеспечивается уменьщением постоянной времени г - разрядных выходных ЩИН за счет предложенного включения основных и дополнительных резисторов с выходными обмотками запоминающих трансформаторов.

Повыщение надежности работы предложенной ячейки памяти обеспечивается увеличением амплитуды сигналов на разрядных выходных

шинах и эффектом компенсации помех в зоне полезного сигнала.

Амплитуда сигналов на разрядных выходных шинах увеличивается за счет уменьшения и.мпеданса разрядных выходных шин.

Формула изобретения

Ячейка памяти для накопителя постоянного запоминающего устройства, содержащая три запоминающих трансформатора, две разрядные вы.ходные щины, между которыми последовательно подключены два резистора, один из выводов первого резистора подключен к первой выходной разрядной шине и к началу выходной

обмотки первого запоминающего трансформатора, конец которой подключен к началу выходной обмотки третьего запоминающего трансформатора и к концу выходной обмотки второго запоминающего трансформатора, начало выходной обмотки второго запоминающего трансформатора подключено ко второй разрядной щине и к одному из выводов второго резистора, конец выходной обмотки третьего запоминаюцдего трансформатора подключен к щине нулевого потенциала, отличающаяся тем, что, с целью повьпления надежности и быстродействия ячейки памяти, она содержит третий резистор, один из выводов которого подключен к шине нулевого потенциала, а второй вывод соединен с концом выходной обмотки второго запоминающего трансформатора и со вторыми

выводами первых двух резисторов.

Источники информации, принятые во внимание при экспертизе;

1.Авторское свидетельство СССР Л 384138, кл. G И С 17/00, 1972.

2.Нефёдов О. Н. и др. Блок микрокоманд ЭВМ модели Л1 4030.Управляющие системы и

машины, 1974,№ 5, с. 135-137, р. 2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределительное устройство | 1982 |

|

SU1083233A1 |

| Матричный накопитель | 1979 |

|

SU799007A1 |

| Устройство для обращения к блокам памяти | 1982 |

|

SU1112405A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU734808A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| Шифратор для трансформаторного постоянного запоминающего устройства | 1976 |

|

SU613399A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

Авторы

Даты

1977-11-25—Публикация

1976-02-09—Подача