1

Изобретение относится к техннке передачи даиных и может использоваться В системах однонаправленной передачи дискретной информации.

Известно устройство для повышепия достоверности дисиретиой информации, соде)ржащее объединенные по входу нриемдик 1сигнала «Фаза, блок декодирования « промежуточный на.копитель, элемент ИЛИ, к одному входу которого подключен выход датчика сигнала «Фаза, а .к другому входу - выход датчика информации через кодирующий блок, причем выход промежуточного накопителя подключен к одному из входов блока мажоритарного (Сложения, к другому входу которого подключен выход первого блока памяти, а также второй блок памяти 1. Однако известное устройство не позволяет с достаточной точностью обнаруживать ошибочно принятую дискретную информацию.

Цель изобретения - повышение вероятности обнаружения ошибочно принятой дискретной информации. Для этого в устройство для повышения достоверности дискретной информации введены счетчик, регистр сдвига, блок управления передачей, блок управления приемом, первый, второй и третий ключи, выходной накопитель, дополнительные блок паМЯти 1И блок декодирования, блок сравнения и ко;Ммутатор «Передача-прием, при этом

выходы счетчика непосредственно и через регистр сдвига подключены к соответствуюш,им входам блока зправления передачей и блока управления приемом, к другим входам которого подключены соответственно выходы приемника силнала «Фаза и блока сравнения, к входам которого подключен выход блока декодирования непосредственно и через последовательно соединенные первый ключ и

дополнительный блок памяти. Выход промеЖ(уточного накопителя подключен к одному входу выходного накопителя непосредственно, через коммутатор «Передача-прием - к другому входу выходного накоиителя, к дополнительному входу блока мажоритарного сложения, выход которого непосредственно и через дополнительный блок декодирования подключен к соответству.юшим входа.м выходного накопителя, и к соответствующим входам элемента ИЛИ, счетчика и третьего ключа, выходы которого подключены к входам второго блока памяти, соединенного с коммутатором «Передача-прием, а через второй ключ - ко входам первого блока ламяти.

Кроме того, выход блока управления передачей подключен к соответствующим входам датчика информации, элемента ИЛИ и коммутатора «Передача -прием, выход блока управления приемом - к соответствующим

входам выходного накопителя, первого ивторого 1КЛ1Оча и коммутатора «Передача-прием, а .выход кодирующего блока - к соответствующему входу коммутатора «Передача-прием.

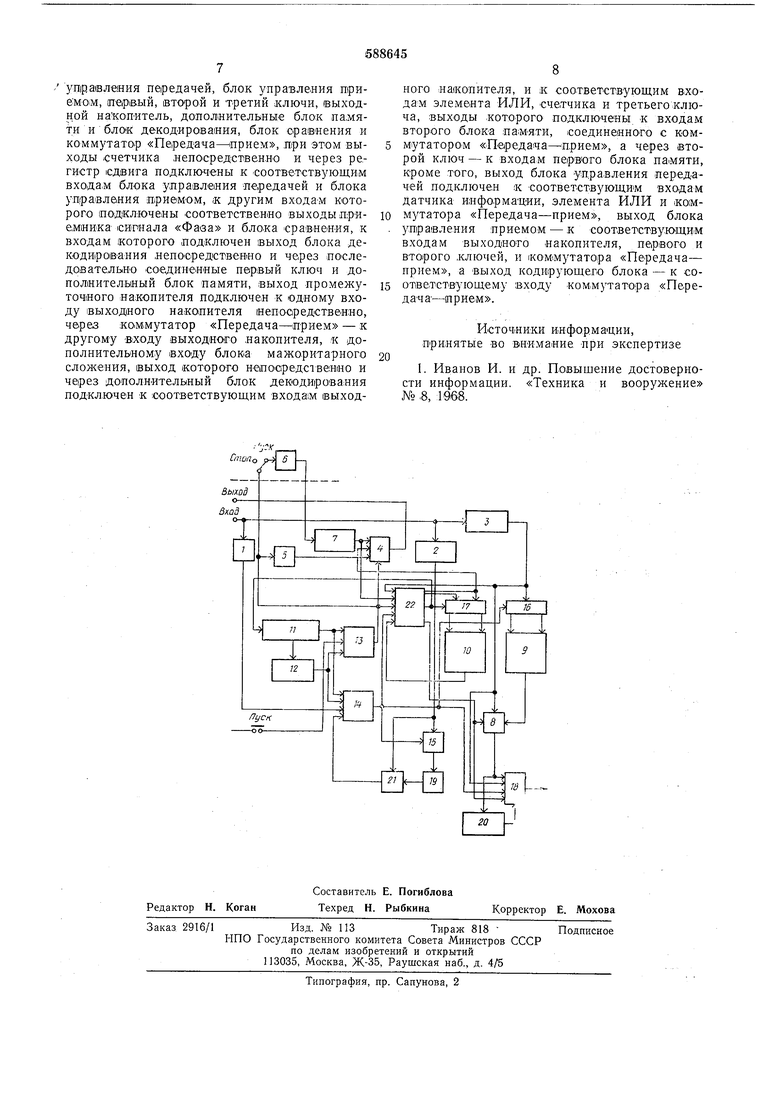

На чертеже изображена структурная электрическая схема юредложенного устройства.

Устройство содержит объединенные по входу приемник 1 сигнала «Фаза, блок 2 декодирования и промежуточный «а копитель 3, элемент ИЛИ 4, к одному входу которого подключен выход датчика 5 еигнала «Фаза, а к другому Входу - выход датчика 6 информации через кодирующий блок 7, причем выход промежуточного накопителя 3 подключен к одному -из входов блока 8 мажоритарного Сложения, к другому входу которого подключен выход первого блока 9 памяти, а также второй блок 10 памяти, счетчик 11, регистр 12 сдвига, блок 13 управления передачей, блок 14 управления приемом, первый ключ 15, Второй ключ 16, третий ключ 17, выходной накопитель 18, дополнительный блок

19памяти, долоднительный блок 20 декодирования, блок 21 сравнения и коммутатор 22 «Передача-прием. Выходы счетчика 11 непосредственно и через регистр 12 сдвига подключены к соответствующим 1ВХОдам блока 13 управления передачей и блока 14 управления приемом, к другим входам которого подключены Соответственно выходы приемника 1 сигнала «Фаза и блока 21 сравнения, к входам которого подключен выход блока 2 декодирования непосредственно и через последовательно соединенные первый ключ 15 и дополнительный блок 19 памяти. Выход гаромежуточного накопителя 3 подключен к одному входу выходного накопителя 18 непосредственно, а через коммутатор 22 «Передача- прием - К другому входу выходного накоплтеля 18, к дополнительному входу блока 8 мажоритарного сложения, выход которого непосредственно и через дополнительный блок

20декодирования подключен к соответствующим вХОдаМ выходного накопителя 18, и к соответствующим входам элемента ИЛИ 4, счетчика 11 и третьего ключа 17, выходы которого подключены к ВХодам второго блока памяти, соединенного с коммутатором «Передача- прием, а через второй ключ 16 - к входам лераого блока 9 памяти. Кроме того, выход блока 13 -удравлени-я передачей подключен к соОТв етствующим входам датчика б информации, элемента ИЛИ 4 и коммутатора 22 «Передача-приеМ, ВЫХод блока 14 управления приемом - к соответствующим входам выходного накопителя 18, первого ключа 15, второго ключа 16 и коммутатора 22 «Передача прием, а выход кодирующего блока 7 - к соответствующему входу коммутатора «Передача-прием.

Устройство работает следующим образом.

Для начала передачи нажима ют кнопку «Пуск и сигналом с выхода блока, 13 управления передачей заиускается датчик 5 сигнала «Фаза, который через элемент ИЛИ 4 ВЫдает на выход устройства последовательность «3 п элементов, предназначенную для ОСуществления фазирования приемной части по импульсу и по циклу. После передачи фазирующей команды сигналОМ с выхода блОКа зправЛения передачей На время, равное длительности / циклов, разрешается запуск датчика информации и через коммутатор «Передача-прием запускается счетчик и открывается третий ключ. При этом к калодым к двоичным символам, выдаваемым с выхода датчика информации, в кодирующем блоке добавляется (п-к)-проверочных символа; / Комбинаций (п, к) кода выдаются на выход

устройства через элеМент ИЛИ и одновреМенно через коммутатор «Передача-прием и открытый третий ключ записываются во второй блок памяти.

После того, KaiK счетчик 11 отсчитает /

циклов, сигнал с выхОДа регистра 12 сдвига через блок 13 управления передачей снова на один цикл запускает датчик 5 сигнала «Фаза и закрывает третий «люч 17, затем сигналом с выхода блока управления запускается счетчик 11, На I циклов открывается третий ключ 17 и /я-элементных комбинаций с выхода второго блока 10 памяти вновь выдаются на выход устройства через элемент ИЛИ 4 и одновременно записываются во второй блОК памяти. Сигнал с выхода блока 13 управления передачей при первой передаче/ комбинаций раЗрешает их выдачу на выход устройства через элемент ИЛИ 4 с выхода датчика 6 информации, при повторных передачах - с выхода второго блОКа 10 памяти. По окончании второго цикла работы счетчика И в третий раз сначала осуществляется запуск датчика сигнала «Фаза, затем счетчика и Вновь раэрещается выдача на выход

устройства сначала фавирующей команды, затем //г-элементных комбинаций с выхода второго блока 10 памяти, при этом третий ключ 17 закрыт и при третьей передаче комбинащий во второй блок 10 паМЯти они не записываются.

Таким образом, иа выход устройства три раза подряд выдается блок из (/+1)-комбинаций, первая из Которых является фазирующей командой. В далынейщем работа устройства в режиме «Передача осуществляется аналогично, за исключением того, что для первой передачи последующего блока из (/+1)-комбинации нет необходимости вновь нажимать .кнопку «Пуск - запуск передающей части будет осуществляться сигналом с выхода блока управления передачей 13.

В режиме «Прием инфорМация с выхода устройства поэлементно поступает на входы промежуточного накопителя 3, блока 2 декодирования и приемника 1 сигнала «Фава. ПОСле приема фазирующей команды сигналом с выхода приемника сигнала «Фаза через блок 14 управления приемом, Коммутатор 22 «Передача-прием запускается счетчик

11 и открывается третий ключ 17, сигналом

с. выхода блока 14 управления приемом открывается nepiBbifi ключ 15. Таким образом, разрешается запись информации с выхода промежуточного лакопителя 3 на вход второго блока 10 памяти и запись -сигнала с выхода бло:ка 2 декодирования «а вход дополнителыного блока 19 памяти. После приема / комбинаций в каждом ряду второго блока 10 памяти будет записана соответствующая л-элементгаая комбинация, а в каждом разряде дополнительного блока 19 памяти - с ошибкой (записана «1) «ли без ошибки (записан «О) эта комбинация была принята. При повторном приеме блока из (/+1)-комбинации вновь запускается счетчик 11, причем в случае неприема фазирующей команды из-з а искажений, вносимых помехами в канале связи, сигнал для запуска счетчика формируется в блоке 14 управления приемом за счет сигнала с выхода регистра 12 сдвига. При noBTOpHOiM приеме /-ком.бинаций в блоке 21 (Сравнения происходит сравнение признака, соответствующего принятой комбинации, с признаком, соответствующим приему этой комбинации первый раз и записанным в определенном разряде дополнительного блока 19 памяти. После повторного приема каждой ком:бинадии на выходе блока 21 сравнения возможен один из четырех сигналов:

00- комбинация пгринята без ошибки оба

раза;

1:1 - комбинация (принята с ошибкой оба раза;

01- комбинация принята без ошибки при

первом приеме и с ошибкой при втором;

10 - комбинация принята с ошибкой при nepiBiOM приеме и без ошибки при втором.

При появлении первого и третьего сигналов ключи 17, 16, 15 закрыты и соответствующая комбинация стирается на выходе промежуточного накопителя 3. При появлении второго сигнала сигналом с выхода блока управления приемом открывается второй ключ 16 и принятая комби-нация записывается в 1соответствующий ряд первого блока 9 пам.яти. При появлении четвертого сигнала сигналом с выхода блока управления приемом открываются первый и третий ключи 15, 17, принятая кО1мбинаЦия записывается в соответствующий ряд второго блока памяти 10 вместо Комбинации, записанной там при пе,рвом приеме, а в соответствующем разряде дополнительного блока 19 памяти стирается признак «I.

При третьем приеме блока из (/-|-1)-комбинаций сигналом с выхода блока 14 управления приемом вновь запускается счетчик 11 аналогично его Запуску при втором приеме блока. При этом ;в блоке 21 сравнения сравнивается признак принятой комбинации с соответствующим признаком, записанном в дополнительном блоке 19 памяти. После третьего приема каждой комбинации :на выходе

блока -сравнения возможен один из четырех сигналов:

00 - комбинация принята без ошибки в третий раз и без ошибки в первый или второй раз (или оба раза);

01-комбинация принята с ошибкой в третий раз и без ошибки в первый или второй раз (или оба раза);

10- комбинация принята без ошибки в третий раз и с ошибкой и первый, и

второй раз;

11- комбинация принята с ошибкой все

три раза. При появлении первого и (второго сигналов

сигналом с выхода блока управления приемом разрешается запись соответствующей комбинация на вход выходного накопителя 18 с выхода второго блока 10 памяти, при появлении третьего сигнала - непосредствеино ic выхода промежуточного накопителя 3. Во всех трех случаях k-информационных элемента комбинации, записанной в выходной накопитель 18, выдаются -на выход приемной части.

При появлении четвертого сигнала разрешается запись на входы выходного накопителя 18 и дополнительного блока 20 декодирования с выхода блока 8 мажоритарного сложения комбинации, сформированной путем

поэлементного мажоритарного сложения комбинаций, принятых первый раз (с выхода блока 10 памяти), второй раз (с выхода блока 9 памяти) и третий раз (с выхода промежуточного накопителя 3). При обнаружении

ошибки во вновь сформированной комбинации сигналом с выхода дополнительного блока 20 декодирования эта комбинация стирается «а выходе выходного накопителя 18, при отсутствии ошибки -выдается на выход приемной части.

Таким образом, предложенное устройство позволяет осуществить автом-атизацию процесса исправления ошибок при однонаправленной передаче информации с одновременным увеличением скорости передачи информации и степени повышения достоверности.

Формула и 3 о б р е т е н и я

Устройство для повышения достоверности дискретной информации, с.одержащее объединенные по входу приемник сигнала «Фаза, блок декодирования и промежуточный накопитель, элемент ИЛИ, к одному входу которого подключен выход датчика сигнала «Фаза, а к другому входу -выход датчика информации через кодирующий блок, причем выход промежуточного накопителя подключен к одному из входов блока мажоритарного

сложения, к другому входу -которого подключен выход первого блока памяти, а также второй блок памяти, отличающееся тем, что, с целью повышения вероятности обнаружения ошибочно принятой дискретной информации, введены счетчик, (регистр -сдвига, блок

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1983 |

|

SU1099397A2 |

| Устройство для приема дискретной информации,закодированной корректирующим кодом | 1984 |

|

SU1172022A2 |

| Устройство анализа кодовых комбинаций | 1976 |

|

SU649152A1 |

| Приемник дискретной информации для симплексных каналов связи | 1980 |

|

SU862376A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| Система передачи данных по каналам с обратной связью | 1980 |

|

SU966923A1 |

| Устройство для приема трехкратно повторяемых команд управления | 1979 |

|

SU873436A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1987 |

|

SU1462492A1 |

Авторы

Даты

1978-01-15—Публикация

1975-01-07—Подача