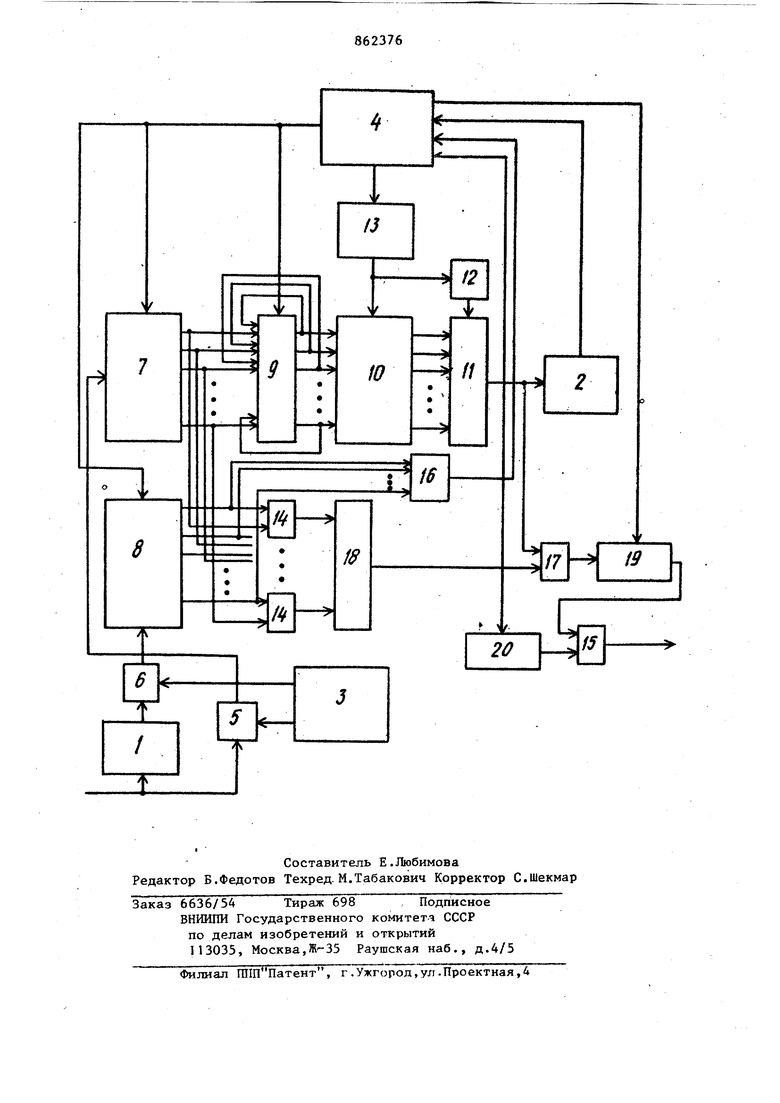

Изобретение относится к радиотехни ке и может использоваться в системах однонаправленной передачи дискретной информации. Известен приемник дискретной информации для симплексных каналов связи, содержащий объединенные по входу декодер и первый блок ключей, выход которого соединен с входом блока памяти кодовых комбинаций, а второй вход - с выходом блока управления приемом, другой выход которого и выхо декодера соединены с входами второго блока ключей, выход которого соединен с блоком памяти ошибок, блок управлеНИЯ считыванием, последовательно соединенные коммутатор, блок мажоритарно обработки и дополнительный декодер, выходной накопитель, выход которого .соединен с одним входом первого элемента ИЛИ, другой вход которого соеди нен с выходом блока формирования сти раний С,3 Однако достоверность приема информации этим приемником невысока. Цель изобретения - повышение достоверности приема информации. Для этого в известный приемник дискретной информации введены блок памяти, генератор сочетаний, блок установки режима, элементы И, три элемента ИЛИ, причем выходы блока памяти ошибок соединены с одними входами элементов И и входами второго элемента ИЛИ, выход которого соединен с одним входом блокауправления считьшанием, другой вход которого соединен с выходом дополнительного декодера, выходы блока памяти кодовых комбинаций соединены с другими входами элементов И и через блок памяти - с входами коммутатора, выходы блока памяти соединены с его соответствующими входами , первый выход блока управления считыванием через генератор сочетаний соединен с соответствующим входом коммутатора и входом блока установки режима, выход которого соединен с входом блока мажоритарной обработки; второй выход блока управления считыванием соедине с дополнительным входом блока памяти и другими входами блока памяти кодовых комбинаций и блока памяти ошибок третий выход блока управления считы ванием соединен с одним входом выход ного накопителя, другой вход которого соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с.выходом блока мажоритарной обработки,.второй вход - с выходом четвертого элемента ИЛИ, входы котор го соединены с выходами элементов И; четвертый выход блока управления считыванием соединен с входом блока формирования стираний. На чертеже представлена структурная электрическая схема предложенного приемника. Приемник дискретной информации для симплексных каналов связи, содер жит декодер 1, дополнительный декоде 2, блок 3 управления приемом, блок 4 управления считыванием, блокиключей 5,6, блок 7 памяти кодовых комбина1ЩЙ, блок 8 памяти ошибок, блок 9 памяти, коммутатор 10, блок 11 мажор тарной обработки, .блок 12 установки режима, генератор 13 сочетаний, элементы И 14, элементы ИЛИ 15 - 18, вы ходной накопитель 19 и блок 20 форми рования стираний. Приемник работает следующим обра зом. Принятые кодовые комбинации через блок ключей 5 записываются в блок 7, и при этом в соответствующие разрядаг блока В с выхода декодера 1 через блок ключей 6 записываются единицы при отсутствии ошибок в принятых комбинациях. После окончания третьего приема первой комбинации пакета блок 4 запускает генератор 13 и считывает с выхода первых трех регистров блока 7 по одной кодовой комбинации. Эти комбинации записываются в блок 9 с выхода которого через коммутатор 10 выдаются на вход блока 11 и снова записываются на свои места в блоке 9. При этом генератор I3 коммутирует в коммутаторе 10 выходы первых трех регистров блока 9 на входы блока II, а блок 12 устанавливает блок 11 для посимвольного сравнения трех комбинаций. Комб нации, сформированные в результате ажоритарной обработки, декодируются в дополнительном декодере 2 и попадают через элемент ИЛИ I7 на вход выходного накопителя 19, в котором стираются при выдаче сигнала ошибка с выхода декодера 2 через блок 4 на управляющий вход выходного накопителя 19. После четвертого приема первой комбинации с помов(ыо генератора 13 и коммутатора 10 осуществляется поочередная мажоритарная обработка для всех сочетаний по три из четырех комбинаций, после пятого приема - по три из пяти, а затем происходит мажоритарная обработка для всех пяти комбинаций (при этом блок I2 устанавливает соответствующий режим блока И) и т.д. Аналогично принятые комбинации подвергаются мажоритарной обработке во всех возможных сочетаниях. После того как найдено соче1;ание, при котором в результате мажоритарной обработки сформирована комбинация, декодирование которой показывает отсутствие ошибок, сигнал с выхода дополнительного декодера 2 через блок 4 разрешает выдачу информации с выходного накопителя 19 через элемент Ида 15. При этом генератор 13 устанавливается в исходное состояние, а комбинация в блоке 9 стирается, т.е. приемник устанавливается в начальный режим для аналогичной обработки следующей комбинации. В этом случае, когда хотя бы один раз комбинация была принята без ошибок, правильно принятая комбинация с выхода соответствующего регистра блока 7 через соответствующий элемент И 14 и элементы ШЗЛ 18,|7 записы- . вается в выходной накопитель 19 и оттуда выуцается получателю через элемент ИШ l5. При этом сигналом с выхода блока 8 через элемент ИЛИ 16 приемник устанавливается в начальный режим для аналогичной обработки следующей комбинации. Если в блок 4 сигнал с выхода блока 8 о наличии в блоке / безощибочно принятой комбинации поступит раньше запуска генератора 13, генератор 13 не запустите до начала анализа следующей комбинации пакета. Если в результате декодирования всех комбинаций, полученных в результате мажоритарной обработки во всех возможных сочетаниях, обнаружены

ошибки, приемник устанавливается в начальный режим, блок 7 запускает блок 20, с выхода которого через элемент ИЛИ 15 получателю выдается сигнал Стираиие.

Таким образом, многократная передача пакетов и.использование посимвольной мажоритарной обработки для комбинаций, принятых с ошибками, позволяют повысить достоверность приема информации.

Формула изобретения

Приемник дискретной информации для симплексных каналов связи, содержащий объединенные по входу декодер и первый блок клочей, выход которого соединен с входом блока памяти кодовых комбинаций, а второй вход -.с выходом блока управления приемом, другой выход которого и выход декодера соединены с входами второго блока ключей, выход которого соединен с блоком памяти ошибок, блок управле«« ния считыванием, последовательно соединенные коммутатор, блок мажоритарной обработки и дополнительный декодер, выходной накопитель, выход которого соединен с одним входом первого элемейта ИЛИ, другой вход которого соединен с выходом блока формирования стираний, отличающийся тем что, с целью повышения достоверности приема информации, введены блок памяти, генератор сочетаний, блок установки режима, элементы И, три элемента ИЛИ, причем выходы блока ftaмяти ошибок соединены с одними входами элементов И и входами второго элемента ИЛИ, выход которого соединен с одним входом блока управления считыванием, -другой вход которого соединен с выходом дополнительного декодера ВЫХОДЫ блока памяти кодовых комбинаций соединены с другими входами элементов И и через блок памяти - с входами коммутатора, выходы блока памяти соединены с его соответствующими входами, первый выход блока управления считыванием через генератор сочетаний ;соеда1нен с соответствующим входом коммутатора и входом блока установки резтма, выход которого соединен с входом блока мажоритарной обработки, второй выход блока управления считыванием соединен с дополнительным входом блока памяти и другими входами блока памйти кодовых комбинаций и блока памяти ошибок, третий выход блока управления считыванием соединен с одним входом выходного накопителя, другой вход которого соединен с выходом третьего элемента ИЛИ, первый вход KOTOpoio соединен с выходом бпока мажоритарной 9бработки, второй вход - с выходом четвертого элемента ИЛИ, входы которого соединены с выходами элементов И, четвертый выход блока управления считьтанием соединен с входом блока формирования стираний Источники информации,

принятые во внимание при экспертизе 1.Авторское свидетельство СССР

по.заявке 2095910/18-09,, кл. Н 04 L 1/10, U7.01.75.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

| Устройство для коррекции ошибок внешней памяти | 1989 |

|

SU1662011A1 |

| Устройство для приема дискретной информации | 1981 |

|

SU1131031A1 |

| Устройство анализа кодовых комбинаций | 1976 |

|

SU649152A1 |

| Устройство для мажоритарного декодирования циклических кодов при трехкратном повторении комбинации | 1984 |

|

SU1246380A1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ СТИРАНИЙ | 2008 |

|

RU2379841C1 |

| Устройство для приема и обработки избыточных сигналов | 1982 |

|

SU1115086A1 |

Авторы

Даты

1981-09-07—Публикация

1980-01-15—Подача